电阻式随机存取存储器 (ReRAM) 是在开发更具可扩展性、高容量、高性能、可靠的存储解决方案的竞赛中下一个有前途的存储器技术。

电阻式随机存取存储器 (ReRAM) 正在成为一种替代的非易失性存储器 (NVM) 解决方案,特别是在需要不断提高性能和能源效率的云和数据中心环境中[1]。随着人类通过视频流等高级服务和机器通过物联网 (IoT) 对数据的需求不断增长,ReRAM 技术表现出比闪存更低的读取延迟和更快的写入性能,同时还实现了 64pJ/cell 的程序能量比 NAND 提高了 20%。

在数据中心环境中,3D 垂直 ReRAM 阵列提供了高性能内存子系统,能够取代传统的基于 DRAM 或闪存的 SSD,从而以更小的外形尺寸和更低的能源需求加速数据处理、存储和检索。借助 ReRAM,可在提供 1GIOPs/U 的架构中实现低于 5 纳秒的延迟。

典型的 ReRAM 单元包含夹在两个金属电极之间的具有不同电阻特性的开关材料。ReRAM 的切换效应基于离子在电场影响下的运动以及切换材料存储离子分布的能力。反过来,这会导致 ReRAM 器件的电阻发生可测量的变化,从而减少随着时间的推移降低存储器组件性能的介电击穿效应。

ReRAM 技术最常见的挑战是温度敏感性、与标准 CMOS 技术和制造工艺的集成,以及单个 ReRAM 单元的选择器机制。因此,设计人员根据他们选择的开关材料和存储单元组织采用许多不同的方法来实现 ReRAM 技术。

综合起来,这些变量可能会导致 ReRAM 技术出现显着的性能差异。因此,评估 ReRAM 时应考虑的四个关键领域是:

可制造性

表现

密度

活力

让我们仔细看看每一个。

可制造性

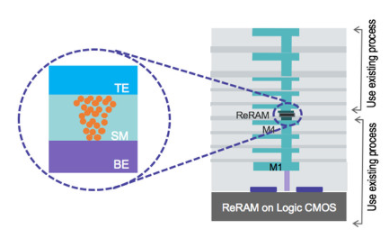

制造 ReRAM 器件时首选 CMOS 友好材料和标准制造工艺,因为它允许该技术轻松集成在两条金属线之间,直接连接到 CMOS IP 逻辑块,并在现有晶圆厂生产,无需专门的设备或材料(图1)。由于 ReRAM 是一种低温、后端 (BEOL) 工艺集成,因此可以在 CMOS 逻辑晶片上集成多层 ReRAM 阵列,以构建 3D ReRAM 存储芯片。这使得高度集成的解决方案在一个优雅且低成本的解决方案中由单个芯片上的片上 NVM、处理内核和模拟子系统组成。

【图1 | 使用标准 CMOS 工艺制造 ReRAM。]

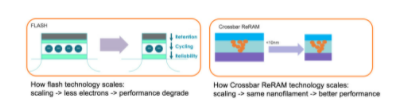

与闪存单元中的电子存储相比,其中一些电子损失会导致可靠性、保留和循环问题,从而导致退化,而 Crossbar 的 ReRAM 单元操作基于非导电层中的金属丝。Crossbar 的 ReRAM 缩放不会影响器件性能,并且具有低于 10 纳米缩放的潜力。

【图2 | Crossbar ReRAM 的单元操作允许该技术扩展到 10 纳米以下工艺而不会退化。]

表现

在编程操作方面,当前的 MLC/TLC NAND 或 3D NAND 闪存需要大约 600 µs 到 1 ms 来编程 8 到 16 KB 页面,而对于大块、4 到 8 MB 页面大约需要 10 ms。

NAND闪存在被编程之前也必须被擦除。垃圾收集是 NAND 闪存中数据管理的附加层,需要在存储空闲时正确释放具有过时数据的块。当垃圾收集将数据从一个块移动到另一个块时收到一个新请求时,这会产生问题,从而在几秒的范围内引入长且不确定的延迟。因此,SSD 写入通常包括在 SSD 控制器、NAND 闪存和 DRAM 组件之间多次写入数据,最初是在保存数据时,然后是在多个垃圾回收周期中移动有效数据时。因此,写入 SSD 闪存的数据多于主机系统最初发出的数据是很常见的。这种差异称为写入放大 (WA)。

WA 是不可取的,因为这意味着更多的数据被写入介质,增加了磨损,并且通过消耗原本为闪存的预期功能操作而保留的带宽而对性能产生负面影响。这在较小的工艺节点上尤其重要,其中 NAND 存储单元的最大周期降至 3,000 个编程周期以下。

相反,ReRAM 使用可更改位、免擦除操作,与 NAND 闪存相比,可提供低 100 倍的读取延迟和快 1000 倍的写入性能,而不受构建大块内存阵列的限制。ReRAM 执行独立原子操作的能力允许将其构建为更小的页面(例如 256 B 页面与 NAND 中的 16 KB 页面),每个页面都可以单独重新编程。这种类型的架构通过删除通常在垃圾收集期间访问的大部分后台内存来减轻存储控制器的负担。NAND 闪存系统的 WA 分数通常在 3 到 4 范围内,而 ReRAM 的特性使 WA 等于 1。这有利于存储解决方案的读写延迟、能耗和使用寿命。

针对 ReRAM 优化的下一代 SSD 控制器将能够更快地更新较小的页面,进一步减少与 NAND 相关的后台内存操作,并提供大约数十微秒的更低、更具确定性的读取延迟。

活力

减少后台内存操作的数量可以提高数据存储解决方案的性能和整体耐用性,还可以降低存储控制器的整体功耗、DRAM 使用量以及数据存储组件消耗的读写功率预算。

密度

高密度 ReRAM 面临的一项技术挑战是潜行(或泄漏)电流。这可以使用具有 1 个 TnR 存储单元阵列的选择器设备来缓解,这使得单个晶体管可以管理大量互连的存储单元。这使得大容量固态存储成为可能。

虽然 1 TnR 使单个晶体管能够以低功耗驱动 2,000 多个存储单元,但它也会导致潜行路径电流的泄漏,从而干扰 ReRAM 阵列的性能和可靠性。Crossbar 的场辅助超线性阈值器件能够将泄漏电流抑制在 0.1 nA 以下,并已在 4 Mb、3D 可堆叠无源集成阵列中成功展示。它实现了报告的最高选择性 10^10,以及小于 5 mV/dec 的极其陡峭的开启斜率、快速的开启和恢复 (《50 ns)、大于 100 M 的循环寿命和加工温度低于300°C。

为云和数据中心提供更快、更高效的存储

ReRAM 技术通过能够满足不断增长的数据需求的更快、更密集和超低延迟的解决方案实现下一代企业存储。随着能源使用和寿命成为云和数据中心环境中的关键总拥有成本 (TCO) 指标,ReRAM 的进步和容量的增加将继续推动 ReRAM 的价值主张。

审核编辑:郭婷

-

控制器

+关注

关注

112文章

16356浏览量

177986 -

DRAM

+关注

关注

40文章

2314浏览量

183471 -

晶体管

+关注

关注

77文章

9688浏览量

138157

发布评论请先 登录

相关推荐

评估云和数据中心应用程序的ReRAM技术选择

评估云和数据中心应用程序的ReRAM技术选择

评论