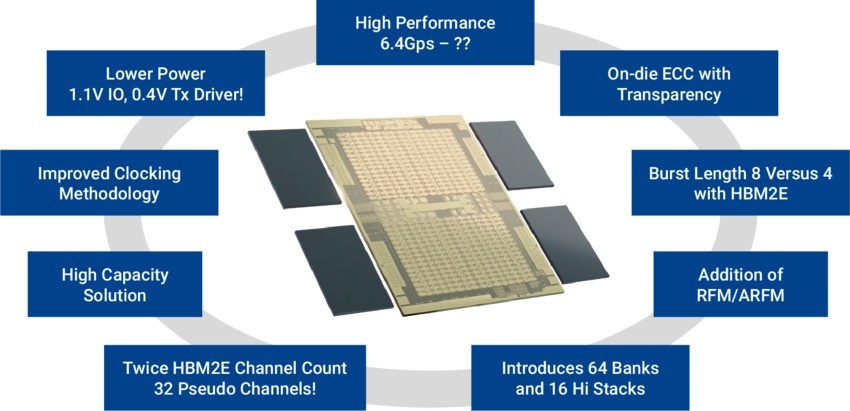

2022 年 1 月,JEDEC 发布了新标准 JESD238“高带宽内存 (HBM3) DRAM”。与现有的 HBM2E 标准 (JESD235D) 相比,HBM3 标准提出了多项增强功能,包括支持更大的密度、更高速运算、更高的 Bank 数、更高的可靠性、可用性、可维护性 (RAS) 功能、低功耗接口和新的时钟架构。HBM3 存储器很快就会被用于 HPC 应用,例如 AI、图形、网络,甚至可能用于汽车。本文重点介绍了 HBM3 标准的一些关键功能,例如高容量、低功耗、改进的信道和时钟架构以及更先进的 RAS 选项。图 1 中突出显示了一些关键功能。

图 1:HBM3 与 HBM2E 相比具有多项改进,包括更高的容量、更先进的 RAS 功能和更低的功耗

更大、更快、更低功耗

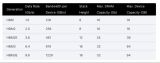

HBM2E标准的每个裸片的最大容量为2GB,每个堆栈可以放置12层裸片,从而可实现24GB的最大容量。虽然标准是允许的,但我们尚未看到市场上出现任何 12 层的 HBM2E 堆栈。HBM3 标准支持裸片的最大容量是4GB,以及高达 16 层的堆栈,总存储空间可以做到 64 GB,相比HBM2E有近 3 倍的增长。Synopsys 预计 8 层和 12 层堆栈选项中的 16 GB 和 24 GB HBM3 器件很快就会上市。 为了支持更高密度的器件,HBM3 增加了从 12 层堆栈到 16 层堆栈的可用 Bank 数,最多提供 64 个 Bank,增加了 16 个 Bank。 HBM3 标准的最高速度为 6.4 Gbps,几乎是 HBM2E 的最高速度 3.6 Gbps 的两倍。 在不久的将来,我们有理由期待第二代 HBM3 设备的出现。只需看看 HBM2/2E、DDR5(6400 Mbps 升级到 8400 Mbps)和 LPDDR5(最大速度为 6400 Mbps,并快速让位于以 8533 Mbps 运行的 LPDDR5X)的速度历史记录,就可见一斑。HBM3 速度高于 6.4 Gbps?这只是时间问题。 除了提高容量和速度外,HBM3 还一直在专注于提高能效。HBM2E 已经提供了最低的传输每比特能耗,这主要是由于它是无端接接口,但 HBM3 在 HBM2E 上还有显著改善。与 HBM2E 的 1.2V 核心电压相比,HBM3 将核心电压降低至 1.1V。除了 100mV 内核电源压降外,HBM3 还可将 IO 信号从 HBM2E 的 1.2V 降低至 400mV。

通道架构

HBM2E 将通道定义为 128 位接口,由两个 64 位伪通道组成。在从系统访问内存方面,引脚接口基于每个通道进行定义,而设计人员则认为伪通道是一项关键功能。HBM2E 对伪通道的突发长度为 4 拍,允许以 32 字节数据包(8 字节宽,每次访问 4 拍)访问内存,该数据包的大小与大多数 GPU 缓存行相当。 HBM3 保持 HBM DRAM 的整体接口大小不变,即 1024 位数据。然而,该 1024 位接口现在被划分为 16 个 64 位通道,更重要的是,被划分为 32 个 32 位伪通道。由于伪通道的宽度已减小到 4 字节,因此对存储器的访问的突发长度增加到 8 拍,从而维持用于存储器访问的 32 字节数据包大小。 伪通道的数量翻倍,加上数据速率的翻倍提升,HBM3可提供比HBM2E更卓越的性能。

可靠性、可用性、可维护性 (RAS)

HBM3 沿袭了 HBM2E 的一些特征,例如数据总线上的 DBI(ac) 和奇偶校验。命令和地址 (CA) 奇偶校验等其他特征已发生改变,从命令中的编码变为 CA 总线上的单独信号。 HBM3 中 RAS 的最大变化之一是如何处理纠错码 (ECC)。我们首先来了解一下 ECC 的主机侧。 HBM2E 为主机提供了一个选项,允许 DM 信号重新用作 ECC 存储位置,从而启用边带 ECC 实现。参考 HBM2E 的伪通道大小,这为用户提供了非常熟悉的 ECC 选项,与 DDR4 ECC DIMM 非常相似 — 支持 64 位数据和 8 位 ECC。 HBM3 已通过多种方式改变了这种 ECC 方法。首先是完全移除 DM 信号。如果系统的目标是将少于 32 字节的数据传输到存储器,则需要执行读改写操作,这可能会对性能造成不利影响。 从 HBM3 标准中删除 DM 信号后,每个伪通道增加了两个 ECC 信号。这并不能为用户提供与 SECDED ECC 相同的功能,因为用户必须真正考虑 32 字节数据(8 拍期间 4 字节数据)和 2 字节校验位(8 拍期间 2 位数据)的整个数据包访问,以汇编 34 字节/272 位代码。 HBM3 标准还考虑了器件侧,要求 HBM3 DRAM 具有片上 ECC。片上 ECC 使用 272 位数据字和 32 位校验位构建,形成 304 位代码字。HBM3 DRAM 的数据字大小是主机使用的代码字大小。现在 HBM3 DRAM 不仅保护数据,还保护主机生成的校验位。 HBM3 标准实时地提供 ECC 运算的结果。每个伪通道包括两个严重性信号,当从 HBM3 DRAM 读取时,这两个严重性信号提供有关突发访问的信息。所提供的信息是四个回答之一 — 所提供的数据没有错误,所提供的数据更正了单个错误,所提供的数据更正了多个错误,或者所提供的数据有未更正的错误。 当器件处于“自刷新”状态或主机发出“刷新所有 Bank”命令时,HBM3 DRAM 器件还支持错误检查和ECS。ECS 操作的结果可通过 IEEE 标准 1500 测试访问端口 (TAP) 访问 ECC 透明度寄存器获得。 HBM3 标准的新 RAS 功能支持刷新管理 (RFM) 或自适应刷新管理 (ARFM)。通常,RFM/ARFM 被用作一种有意或无意反击 Row Hammer 的技术。当重复访问 DRAM 行或行区域会影响未访问的附近行时,会发生 Row Hammer,从而影响这些附近行中的数据。使用 HBM3 DRAM 中的信息,HBM3 控制器能够确定何时需要额外的刷新管理来缓解 Row Hammer。

新的时钟架构

HBM3 的主要功能之一是新的时钟方案。在所有前几代 HBM 中,从主机到器件的单个时钟基本上同步了主机和器件之间的接口。该时钟信号 (CK) 用于设置从主机传递到器件的 CA 信号的传输速率。此外,它还固定了数据 (DQ) 和数据选通 (WDQS/RDQS) 在主机和器件(写入)或器件和主机(读取)之间传输的速率。 在考虑 HBM2E 时,时钟信号和数据选通均以 1.8 GHz 的最大速率运行,因此 CA 接口上信息传输的最大有效速率与数据一样,都为 3.6 Gbps。 HBM3 通过将传统时钟信号从主机去耦到器件和数据选通信号来更改时钟架构。事实上,虽然 HBM3 中 WDQS 和 RDQS 的全新最大速率为 3.2 GHz,可实现高达 6.4 Gbps 的数据传输速率,但 CK 从主机到器件的最快速率仅为 1.6 GHz(即使数据通道以 6.4 Gbps 运行)。 将时钟信号与选通分离,能使时钟信号的运行速度大幅度慢于数据选通。CA 总线上的最大信息传输速率现在为 3.2 Gbps,因为 CA 时钟的最大传输速率已限制为 1.6 GHz。虽然 HBM2E 需要 3.6 Gbps 的 CA 传输速率,但 HBM3 只需要 3.2 Gbps 的 CA 传输速率。

高速内部时钟

分离 CA 时钟和数据选通的决定不仅会影响主机和器件之间的接口,还会影响主机内部 HBM3 控制器和 HBM3 PHY 的接口。 在典型主机内,控制器和 PHY 与外部存储器通信。控制器和 PHY 之间的接口通常使用称为 DDR PHY 接口 (DFI) 的规范来实现。DFI 规范允许 SoC 设计师把通常将系统命令转换为 HBM 命令的 HBM3 控制器和通常将 SoC 上的数字域转换为主机到器件接口的模拟域的 HBM3 PHY 的设计分开。在 HBM3 控制器和 HBM3 PHY 之间具有已定义的接口,为设计师和集成商提供了在数字(控制器)和模拟 (PHY) 之间拆分设计团队的清晰描述。 在高性能 HBM2E 解决方案中,除了带宽外,延迟也是控制器和 PHY 的重点。在 HBM2E 系统中,时钟和选通以相同频率运行,最高可达 1.8 GHz。HBM2E 系统的最低延迟解决方案是使用 DFI 1:1 频率比 – 使控制器、DFI、PHY 和存储器都在同一 1.8 GHz 时钟上运行。 新的 HBM3 时钟架构使用户能够在从 HBM2E 迁移到 HBM3 时专注于低延迟、高性能的解决方案。如上所述,带 HBM3 的 CA 总线的最高定义频率为 1.6 GHz,而数据选通以 3.2 GHz 运行。这使用户能够为 HBM3 控制器和 PHY 实现 DFI 12 频率比。在这种情况下,控制器、DFI、PHY 和存储器时钟均以 1.6 GHz 运行,而选通频率为 3.2 GHz。这为设计师提供了命令和地址接口的 DFI 1:1 频率比以及数据的 DFI 1:2 频率比,所有这些都最大限度地减少了延迟。

总结

HBM3 标准提供了优于 HBM2E 标准的多项改进。有些是预期的改进 - 更大、更快和功耗更低的器件,有些是意想不到的 – 信道架构变更、RAS 改进和更新的时钟方法。新标准累计为用户提供显著改善的 HBM 存储器,用于下一代 SoC。 新思科技提供完善的 HBM3 IP 解决方案,包括控制器、领先工艺节点中可用的 PHY 以及已验证IP。新思科技是 JEDEC 的活跃成员,帮助推动了最新存储器标准的制定和采用。新思科技的可配置存储器接口 IP 解决方案可以进行定制以满足 SoC 的确切要求,用于图形、云计算、网络、AI 等应用,甚至是汽车。

审核编辑 :李倩

-

存储器

+关注

关注

38文章

7528浏览量

164295 -

gpu

+关注

关注

28文章

4768浏览量

129315 -

堆栈

+关注

关注

0文章

182浏览量

19815 -

HBM3

+关注

关注

0文章

74浏览量

165

原文标题:设计师需要了解的 HBM3 相关知识

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

HBM3E量产后,第六代HBM4要来了!

HBM格局生变!传三星HBM3量产供货英伟达,国内厂商积极布局

中国AI芯片和HBM市场的未来

三星HBM芯片遇阻英伟达测试

三星联席CEO在AI合作交流中力推HBM内存

韩美半导体新款TC键合机助力HBM市场扩张

HBM3E起飞,冲锋战鼓已然擂响

NVIDIA预定购三星独家供应的大量12层HBM3E内存

英伟达CEO赞誉三星HBM内存,计划采购

SK海力士HBM3E正式量产,巩固AI存储领域的领先地位

三星强化HBM工作团队为永久办公室,欲抢占HBM3E领域龙头地位

HBM、HBM2、HBM3和HBM3e技术对比

介绍HBM3标准的一些关键功能

介绍HBM3标准的一些关键功能

评论