静态时序分析在电路设计中的作用重要。

如果电路出现建立时间(根据网络资料理解:为将信号稳定建立,数据输入端信号保持稳定的最短时间)错误,电路工作速度变慢。

如果电路出现保持时间(根据网络资料理解:为使传递信号正确,输入信号保持稳定的最短时间,若保持时间错误,正确的输入信号会被其他输入信号覆盖或不能按时传输到对应位置,导致输入信号错误)错误,电路可能不能正常工作。

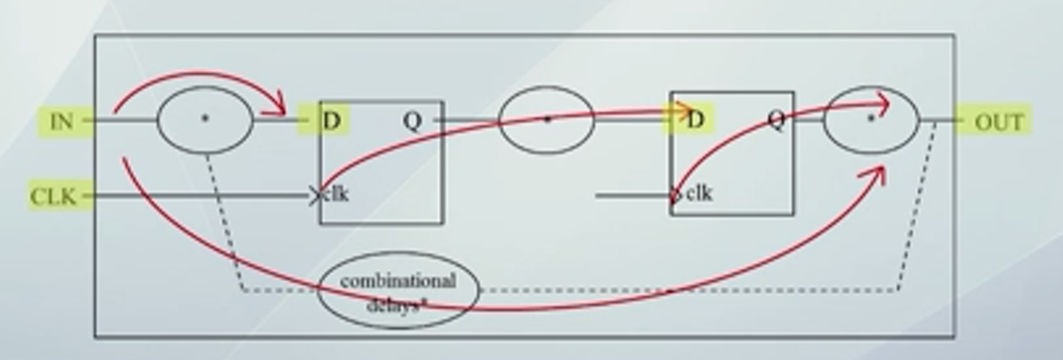

一个芯片电路通常包含四种类型的时序路径:

(1)从芯片内部的源D触发器(发送数据的触发器)开始,经过一系列数据云图(一系列组合逻辑电路),送达到芯片内部的目标D触发器的数据端。

(2)输入路径,从芯片的输入端,经过一系列数据云图,送达到芯片内部的D触发器。

(3)输出路径,芯片内部的D触发器,经过一系列数据云图,送达到芯片的输出端。

(4)信号从芯片输入端经过一系列组合逻辑电路达到芯片输出端,时钟信号对其不产生影响。

所有的时序分析均基于以上四种时序路径分析。归纳以上四种路径,所有的输入信号均来源于芯片输入端和时钟输入,所有的输出信号都输出到芯片输出端或下一个时序器件的输入端。

图片来源:学堂在线《IC设计与方法》

Quarus Ⅱ工具(PLD设计工具,PLD是可编程器件,一种芯片的设计方式)有两种方式进行静态时序分析。

一种是自动化的方式,点击编译按钮,Quarus Ⅱ工具会自动完成包括静态时序分析、布局布线等工作。

另一种是手动的方式,在大型设计中,设计人员一般会采用手动方式进行静态时序分析。手动分析方式既可以通过菜单操作(个人理解:通过鼠标点击和键盘输入)进行分析,也可以采用Tcl脚本(工具控制语言,个人理解运用代码控制)进行约束和分析。

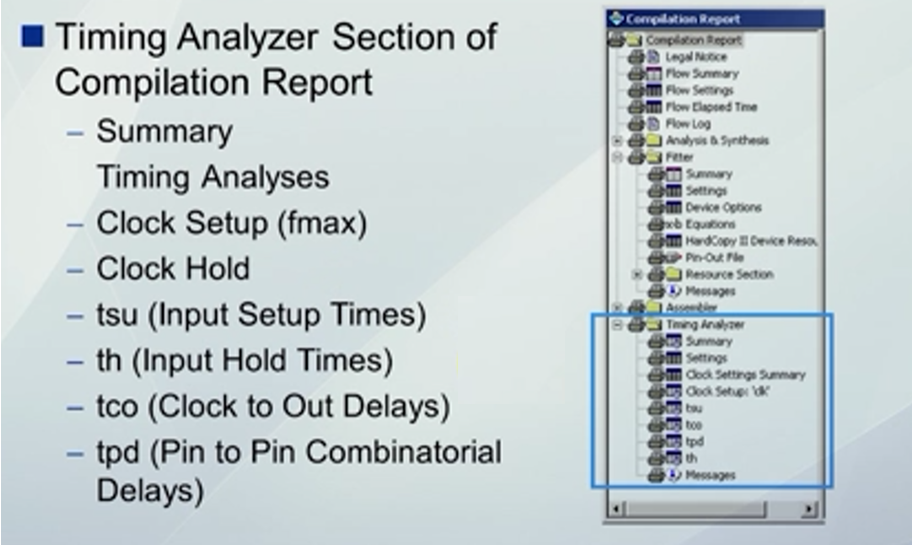

下图蓝框内为时序分析结果,需要关注的分析结果包括:时序分析约束的设置、芯片报告的总结、内部时钟率分析(芯片建立时间和保持时间的报告)、输入路径的建立时间和保持时间的报告、输出的TCO(时钟输出延迟)报告、组合逻辑路径延时报告。

图片来源:学堂在线《IC设计与方法》

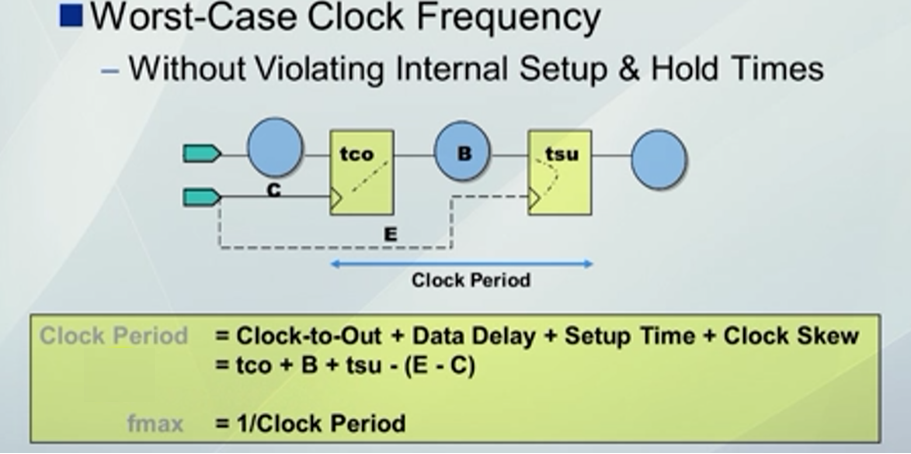

下图是时钟周期(Clock Period)的描述。

信号从源触发器(图中标有tco的黄色小矩形)输出到目标触发器(图中标有tsu的黄色小矩形)需经过内部组合电路B(图中标有B的圆形),经过内部组合电路B会产生延时。

时钟信号传递到源触发器会产生延时C,传递到目标触发器会产生延时E。因为传递到源触发器和目标触发器的路径不同,所以C和E不一定相同。

时钟信号到达触发器时,数据会经过tco(Clock to Out)的延时,再经过路径B(Data Delay)的延时,同时目标触发器需要tsu(Setup Time)的延时达到稳定。

除上述三个延时外,还需考虑时钟信号传递到触发器的延时。若E的延时大于C的延时,数据传输时间余量增多,其他条件不变,时钟周期(Clock Period)可以缩短。若C的延时大于E的延时,数据传输时间余量减少,其他条件不变,时钟周期(Clock Period)需要增加。

综上,时钟周期的描述公式如下图黄色矩形内的公式所示。芯片工作的最高频率为时钟周期的倒数。

图片来源:学堂在线《IC设计与方法》

-

电路设计

+关注

关注

6747文章

2826浏览量

220609 -

触发器

+关注

关注

14文章

2065浏览量

63617 -

时序

+关注

关注

5文章

411浏览量

39049

原文标题:芯片设计相关介绍(31)——PLD静态时序分析

文章出处:【微信号:行业学习与研究,微信公众号:行业学习与研究】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

MIC5236:低静态电流μCap LDO稳压器的卓越之选

Microchip MCP1700:低静态电流LDO的卓越之选

深入解析SGM2047:超低静态电流LDO的卓越之选

ADP165/ADP166:低静态电流LDO稳压器的卓越之选

SGM6029:超低静态电流同步降压转换器的卓越之选

Microchip TC1302A/B:低静态电流双输出LDO的卓越之选

深入解析LTC2924:高效电源时序控制器的卓越之选

深入剖析UCD90160A:16轨电源时序器与监控器的卓越之选

RGB时序灯条的工作原理讲解

SGM66099同步升压转换器:超低静态电流的高效之选

ADP7000系列示波器特色功能:抖动分析,捕捉时序之微

Chroma 80611 电源时序/安规综合分析仪:电器安全与性能的自动化验证专家

vivado时序分析相关经验

汽车软件团队必看:基于静态代码分析工具Perforce QAC的ISO 26262合规实践

芯片设计之PLD静态时序分析

芯片设计之PLD静态时序分析

评论