电子发烧友网报道(文/周凯扬)进入AI和云时代以来,显而易见的趋势之一就是FPGA出现的频率开始降低了,且不说曾经的两大FPGA巨头均已被x86厂商收购,就连FPGA引以为豪的多样化和灵活性,也被专注于特定应用但全定制化、成本低的ASIC压得有些抬不起头来。FPGA厂商们也没法维系那么多的应用,去和不断涌现的ASIC初创公司在各个领域去一一硬碰硬。

与此同时,FPGA大厂在被收购后,也开始顺应他们的技术路线,可以看到他们的产品方向开始往数据中心、通信基建这些平均产品单价更高的应用上发展,尤其是智能网卡、IPU、DPU这类产品。虽然说中端FPGA产品并没有就此消失,但明显竞争力已经大不如前了,过去的那些产品连满足现代计算处理的标准和需求都有些勉强,更不用说未来了。FPGA需要一阵令其重获新生的新风,而基于RISC-V打造的SoC FPGA或许就能充当这样的角色。

FPGA上的RISC-V

RISC-V和FPGA的关系打从一开始就非常密切,不少RISC-V核心、处理器都是在FPGA上实现或验证的。与此同时,RISC-V从IP、架构和指令上带来的创新也被FPGA厂商们看在眼里,诸如Microchip、易灵思、安路科技等厂商都开始基于RISC-V打造全新的FPGA产品,英特尔也开发了为其FPGA打造的RISC-V软核,Xilinx也成了RISC-V国际基金会的战略会员,RISC-V在FPGA上的普及速度可能远超你的想象。

以Microchip的PolarFire为例,作为首个支持RISC-V ISA的SoC FPGA系列,终于在今年6月正式进入量产阶段了,具体包括MPFS250T和MPFS025T这两款产品。PolarFire系列采用了4输入LUT+DFF的设计,最大规模的MPFS460T可以做到461K逻辑单元。

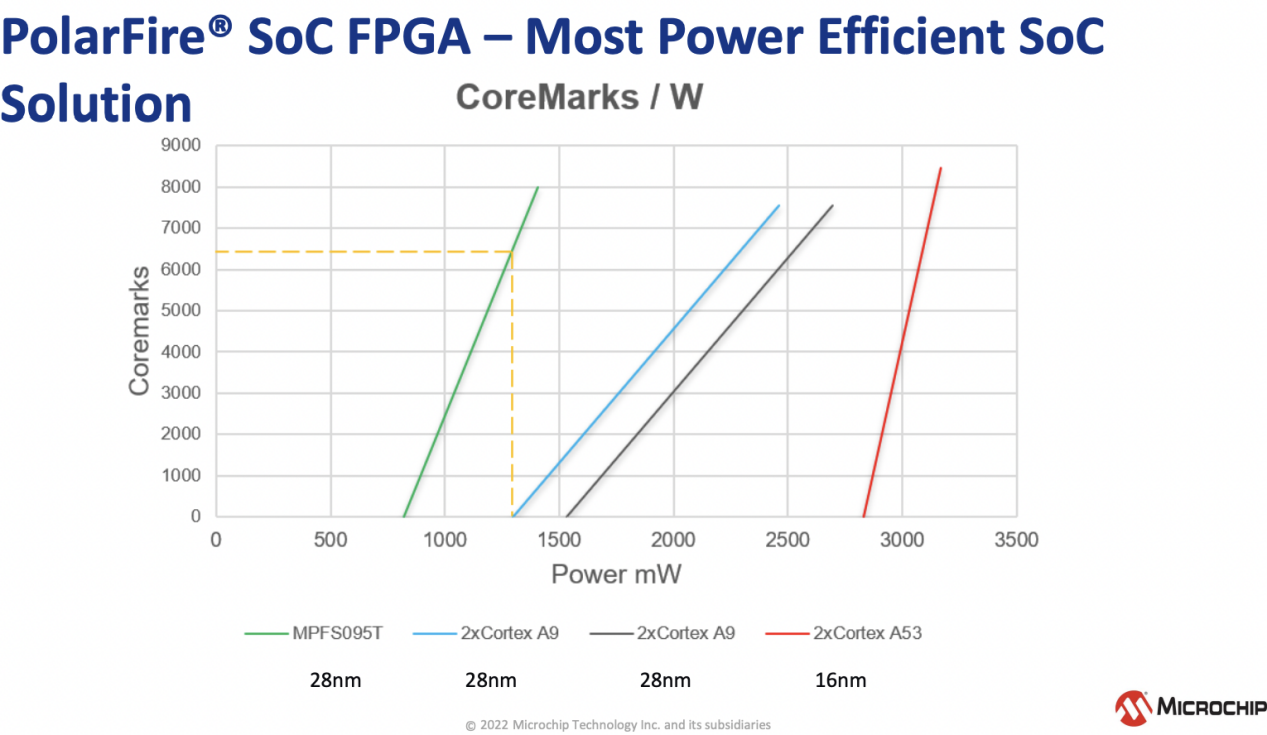

PolarFire CoreMark跑分 / Microchip

而在SoC方面,PolarFire采用了5个64位RISC-V核心的设计,E51作为monitor单核,负责启动和配置处理器子系统,另外四个U54核心则主要用于负责运行Linux之类的操作系统。至于为何选择RISC-V而不是像旗下另一SoC FPGA系列SmartFusion一样选择ARM,Microchip也给出了同等逻辑单元密度下CoreMark跑分的对比,可以看出即便是在工艺落后(28nm对比16nm)的情况下,基于RISC-V的PolarFire SoC依然是最高效的那个,Microchip指出与其他中端FPGA相比,可以将能耗降低最多50%。

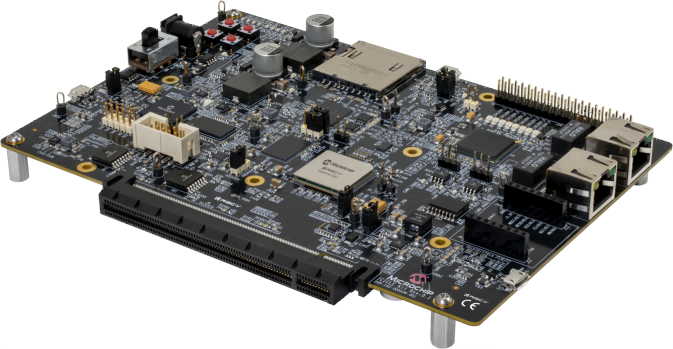

PolarFire FPGA开发套件 / Microchip

为了方便开发者完成不同SoC之间的嵌入式应用程序移植,Microchip也专门打造了MI-V这一面向RISC-V的生态系统,在本身提供RISC-V软核IP的同时,也和IAR Systems、SiFive、Zephyr等第三方公司合作,提供开发工具、CPU IP和RTOS等支持。

拥抱开源生态

Rapid Silicon是一家专注于打造AI FPGA的初创公司,从他们的董事长兼首席执行官Naveed Sherwani博士的公开发言中,可以看出Rapid Silicon作为开源FPGA基金会的创始成员之一,计划利用FPGA开拓边缘AI应用,比如智能家居、安防监控和汽车传感器管理和智能座舱等市场,而他们手里的王牌既有专用AI技术,也有开源EDA软件。

Rapid Silicon在近期推出了Gemini,一个基于台积电16nmFF工艺的FPGA,采用了常见的FPGA设计,比如6输入的可分割LUT、DSP区块和真双端口的Block RAM。最大规模为250K逻辑单元、1250个DSP区块和9.5Mb的片上Block RAM,4个输出PLL支持生成高达1GHz的时钟信号。作为中端FPGA,其规模不算太大,但完成边缘AI的应用还是绰绰有余的。

Gemini框架 / Rapid Silicon

对于硬件资源充裕的FPGA来说,RISC-V和Arm未必就是不能共存的死对头,这点在Gemini也能体现出来。Gemini集成了单核32位的RISC-V处理器和双核的ARM A53处理器。32位的RISC-V处理器作为支持自定义指令的实时应用处理器,最高频率可达533MHz,同时拥有16KB的I/D cache和64KB的程序内存。

Gemini上的64位Arm处理器浮点单元频率可达1.6GHz,此外还集成了支持最高2166Mbps DDR内存的DRAM控制器、PCIe 4.0的PCIe控制器、10G以太网控制器等,均由高性能低延迟的FlexNoC互联在一起。

更重要的是,Gemini的诞生还是利用他们自己的开源FPGA EDA套件Raptor打造出来的,这也证明了依靠开源工作流打造FPGA系统是完全可行的。2021年10月,Rapid Silicon获得了来自成为资本领投的1500万美元种子资金,考虑到成为资本是RISC-V国际基金会的高级会员,创始人李世默也是RISC-V国际基金会理事,愿意对Rapid Silicon投资也就不足为奇了。

结语

与传统的ASIC方案相比,SoC FPGA还是有着不少优势的,比如没有昂贵的NRE成本或是最小采购量的需求。再者,FPGA最大的优势还是在可编程上,即便是已经出货的产品也能重新编程,进一步降低设计风险。而RISC-V的出现,则为这类SoC FPGA带来了一个全新而开放的ISA选择。

-

ASIC芯片

+关注

关注

2文章

91浏览量

23720 -

FPGA芯片

+关注

关注

3文章

246浏览量

39775 -

RISC-V

+关注

关注

44文章

2227浏览量

46000

发布评论请先 登录

相关推荐

RISC-V发展及FPGA厂商为什么选择RISC-V

RISC-V近期市场情况调研

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

risc-v的发展历史

rIsc-v的缺的是什么?

为什么要有RISC-V

解锁RISC-V技术力量丨曹英杰:RISC-V与大模型探索

玄铁RISC-V生态大会深圳召开,达摩院引领RISC-V创新应用

RISC-V能让FPGA从ASIC时代崛起吗?

RISC-V能让FPGA从ASIC时代崛起吗?

评论