2022年8月22日,数字实现EDA先进解决方案供应商芯行纪科技有限公司(以下简称“芯行纪”)宣布推出首款自主研发的数字实现EDA产品——AmazeFP智能布局规划工具。

AmazeFP将机器学习技术与布局规划引擎结合,在兼顾性能、功耗和面积(PPA)的同时,提供了高度智能的拥塞感知、便捷的数据流分析和宏单元自动整理对齐功能,有效解决当前数字芯片在后端设计阶段布局规划节点面临的经验值需求高、手工耗时长、数据流结构分析手段单一、设计问题后期定位收敛性差等难题,助力用户在后端设计初期快速有效地获取优化布局方案,减少迭代次数,从而节约大规模设计的研发成本,提速产品上市时间。

AmazeFP:高度智能化的布局规划工具

芯片设计进入后端设计流程后,依次会进入布局规划、标准单元摆放、时钟树生成、布线、优化等阶段。伴随先进工艺制程的不断进步,设计的规模日益扩大,随之每一个设计环节需要的时间也愈长,例如一个GPU模块布局规划方案可能要经历数十轮次迭代和花费数周才能初步定型,模块开发人员在应对优化PPA的要求时也承受着巨大的时间目标压力,而芯片布局规划作为芯片后端设计流程中的第一步,起着万丈高楼始于基石的重要作用。表现优异的布局规划不仅能实现更好的PPA,也为设计流程的后续步骤提前扫除障碍,加速设计收敛,保证项目高质量地顺利流片。

融合机器学习技术,拥有智能拥塞感知模型,内嵌数据流导向引擎,自动整理对齐宏单元等新一代数字实现EDA软件特征,使得AmazeFP在布局规划过程中表现优越。

//

AmazeFP采用的机器学习技术在考虑了时序、面积、功耗因素的基础上快速获取高质量的宏单元布局思路,提供初步布局规划;

智能拥塞感知模型可以大幅提升拥塞预测的精确度,并据此调整宏单元位置,确保芯片整体的可绕通性;

内置的数据流导向引擎,可自动规划分组宏单元摆放,减少各模块之间总体布线长度,加速宏单元关键路径的时序收敛;

自动整理对齐功能可以根据用户所选的宏单元自动生成网格化归准窗口,极大节省用户手动规整对齐宏单元的时间。

AmazeFP实际使用案例

1

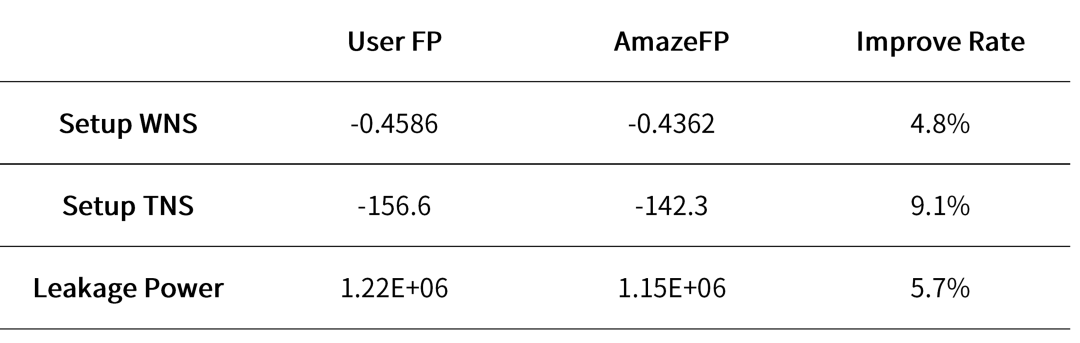

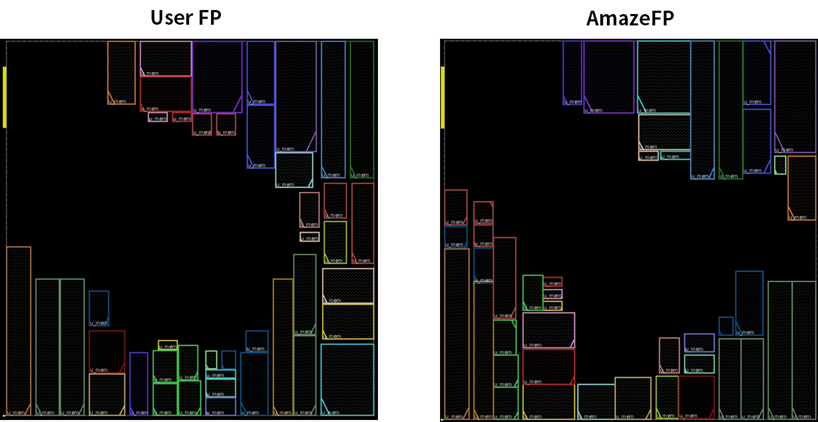

案例一为视频编解码设计模块,该设计共包含44个宏单元,工作频率为1.5GHz。如图一所示,左图为工程师经过数次调整和迭代之后确定的手动摆放的宏单元布局,整体耗时约为三天,右图为AmazeFP依据设计数据流结构以及布线拥塞感知之后自动摆放的宏单元布局,整体运行时间为30分钟。根据这两种布局规划,在全部完成布局布线工作后,对比时序的结果,AmazeFP的全局Setup WNS和Setup TNS相较于手动布局规划分别有4.8%和9.1%的提升,其中Reg2Reg Setup WNS改善54.6%,Reg2Reg Setup TNS改善86.1%。与此同时,AmazeFP提供的布局方案节省了5.7%的静态功耗。

表一:案例一手动布局规划与AmazeFP自动处理结果对比

图一:视频编解码设计模块的宏单元布局对比

2

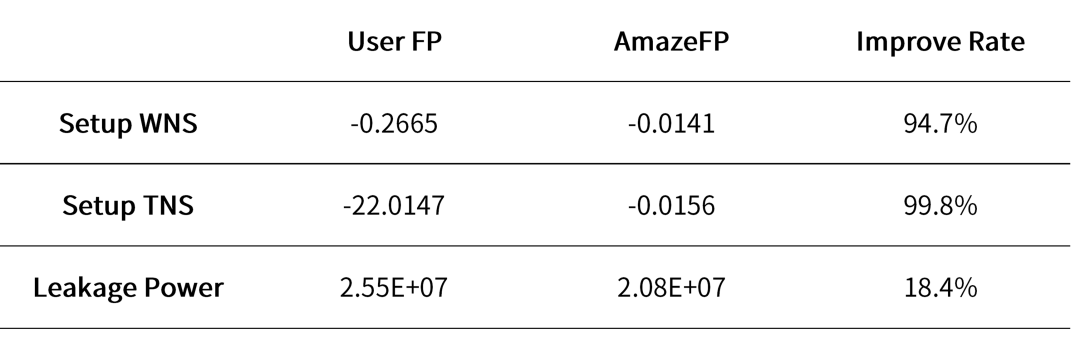

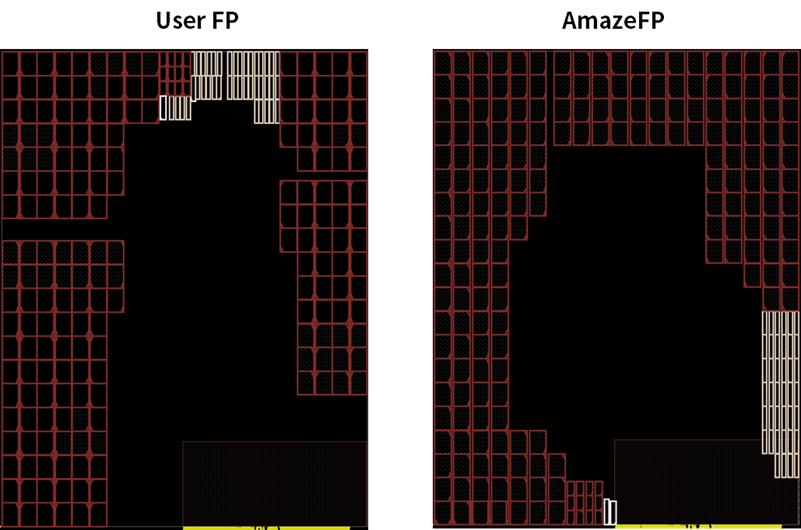

案例二为GPGPU设计模块,该设计中共包含246个宏单元,工作频率为1GHz。如图二所示,左图为工程师耗时5天经过多次迭代调整之后手动摆放的宏单元布局,右图为AmazeFP 2小时内自动摆放的宏单元布局。经过相同设置的布局布线流程后,时序结果分析显示,AmazeFP的全局Setup WNS和Setup TNS分别有94.7%和99.8%的提升,其中Reg2Reg Setup WNS 和 Setup TNS为0。在功耗优化方面,AmazeFP相较于手动布局规划减少12.6%的绕线长度(Wirelength)和18.4%的静态功耗。

表二:案例二手动布局规划与AmazeFP自动处理结果对比

图二:GPGPU设计模块的宏单元布局对比

AmazeFP优客计划

芯行纪坚持用创新来引领数字实现EDA产品的自主研发,在解决产品功能实现的基础上,追求Smart、Speedy、Simple的“3S”产品理念,把机器学习等技术真正贯穿于基础软件架构和具体功能实现,从丰富的设计经验中提炼关键需求,着力于解决设计过程的真正痛点。基于强大的研发团队实力,芯行纪期待聆听合作伙伴的创意需求,“AmazeFP优客计划”致力于及时地将任何能够提升设计效率的优秀创意展现于产品的更新版本。

审核编辑 :李倩

-

智能化

+关注

关注

15文章

4900浏览量

55494 -

机器学习

+关注

关注

66文章

8425浏览量

132770

原文标题:芯行纪推出首款自主研发的智能布局规划工具AmazeFP

文章出处:【微信号:gh_2894c3fc5359,微信公众号:芯行纪】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

艾伟达发布数字芯片EDA工具adsDesigner

联合电子首款800V高压平台逆变砖产品实现量产交付

国内首款自主研发28nm显示芯片量产

国数集联研发出首款CXL多级网络交换机

国芯新材料研发并推出全球首款可商用的钾离子电池产品

本源超导量子计算机自主制造链11类产品系列之一:国产首个量子芯片设计工业软件Q-EDA

首款自主研发的数字实现EDA产品——AmazeFP

首款自主研发的数字实现EDA产品——AmazeFP

评论