在高速PCB设计的学习过程中,串扰是一个需要大家掌握的重要概念。它是电磁干扰传播的主要途径,异步信号线,控制线,和I/O口走线上,串扰会使电路或者元件出现功能不正常的现象。

串扰(crosstalk)

指当信号在传输线上传播时,因电磁耦合而对相邻的传输线产生的不期望的电压噪声干扰。这种干扰是由于传输线之间的互感和互容引起的。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

克服串扰的主要措施是:

加大平行布线的间距,遵循3W规则;

在平行线间插入接地的隔离线;

减小布线层与地平面的距离。

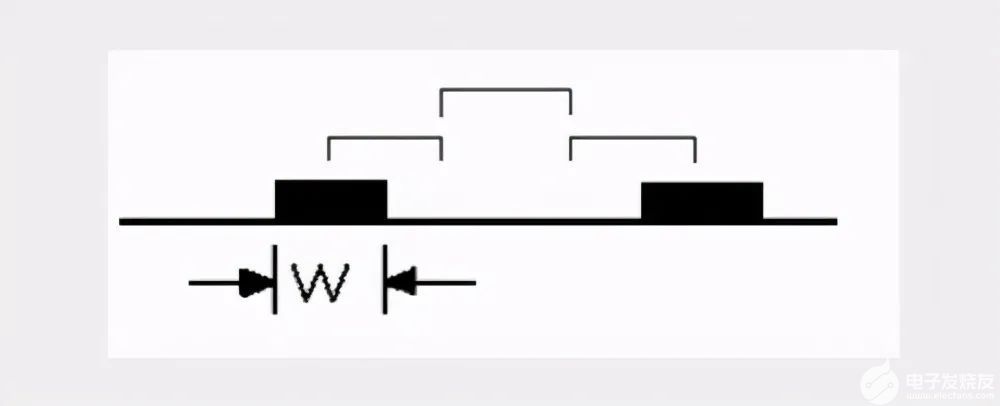

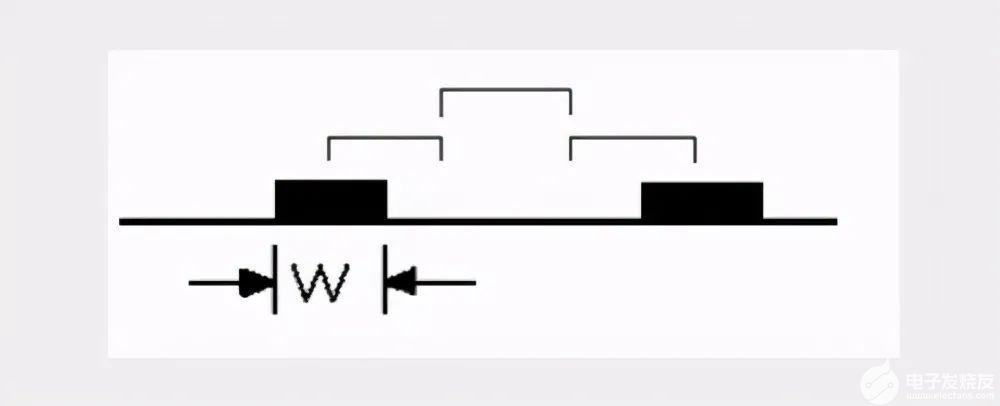

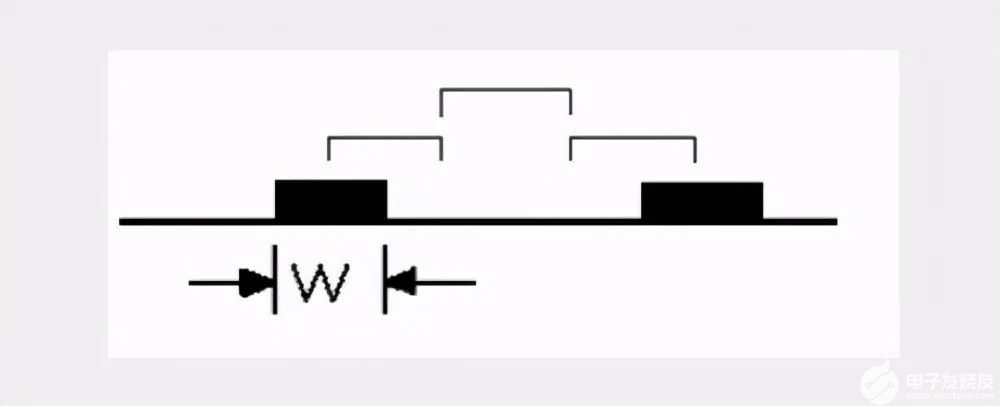

3W规则

为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要达到98%的电场不互相干扰,可使用10W的间距。

注:在实际PCB设计中,3W规则并不能完全满足避免串扰的要求。

避免PCB中出现串扰的方法

为避免PCB中出现串扰,工程师可以从PCB设计和布局方面来考虑,如:

1、根据功能分类逻辑器件系列,保持总线结构被严格控制。

2、最小化元器件之间的物理距离。

3、高速信号线及元器件(如晶振)要远离I/O互连接口及其他易受数据干扰及耦合影响的区域。

4、对高速线提供正确的终端。

5、避免长距离互相平行的走线布线,提供走线间足够的间隔以最小化电感耦合。

6、相临层(微带或带状线)上的布线要互相垂直,以防止层间的电容耦合。

7、降低信号到地平面的距离间隔。

8、分割和隔离高噪声发射源(时钟、I/O、高速互连),不同的信号分布在不同的层中。

9、尽可能地增大信号线间的距离,这可以有效地减少容性串扰。

10、降低引线电感,避免电路使用具有非常高阻抗的负载和非常低阻抗的负载,尽量使模拟电路负载阻抗稳定在10Ω~10kΩ之间。因为高阻抗的负载将增加容性串扰,在使用非常高阻抗负载的时候,由于工作电压较高,导致容性串扰增大,而在使用非常低阻抗负载的时候,由于工作电流很大,感性串扰将增加。

11、将高速周期信号布置在PCB板内层。

12、使用阻抗匹配技术,以保证信号完整性,防止过冲。

13、注意对具有快速上升沿(tr≤3ns)的信号,进行包地等防串扰处理,将一些受EFTlB或ESD干扰且未经滤波处理的信号线布置在PCB的边缘。

14、尽量采用地平面,使用地平面的信号线相对于不使用地平面的信号线来说将获得15~20dB的衰减。

15、信号高频信号和敏感信号进行包地处理,双面板中使用包地技术将获得10~15dB的衰减。

16、使用平衡线,屏蔽线或同轴线。

17、对骚扰信号线和敏感线进行滤波处理。

18、合理设置层和布线,合理设置布线层和布线间距,减小并行信号长度,缩短信号层与平面层的间距,增大信号线间距,减小并行信号线长度(在关键长度范围内),这些措施都可以有效减小串扰。

-

pcb

+关注

关注

4332文章

23198浏览量

400987 -

串扰

+关注

关注

4文章

189浏览量

27028

发布评论请先 登录

相关推荐

关于高速PCB设计的串扰知识

关于高速PCB设计的串扰知识

评论