正如我们许多人所知,集成电路或 IC 是在一个小封装中的许多小电路的组合,它们一起执行一项任务。就像运算放大器或 555 定时器 IC 是由许多晶体管、触发器、逻辑门和其他组合数字电路组合而成的。类似地,触发器可以通过使用逻辑门的组合来构建,而逻辑门本身可以通过使用几个晶体管来构建。

逻辑门是许多数字电子电路的基础。从基本的触发器到微控制器,逻辑门构成了比特如何存储和处理的基本原理。他们使用算术逻辑陈述系统的每个输入和输出之间的关系。有许多不同类型的逻辑门,它们中的每一个都有用于不同目的的不同逻辑。但本文的重点将放在OR Gate上,因为稍后我们将使用 BJT 晶体管电路构建 OR Gate,类似于我们之前构建的AND Gate 晶体管电路。

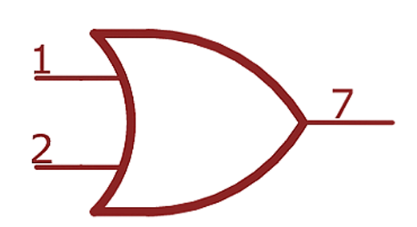

或逻辑门

或门实现布尔“析取”,即它有助于找到给定二进制输入的最大值。

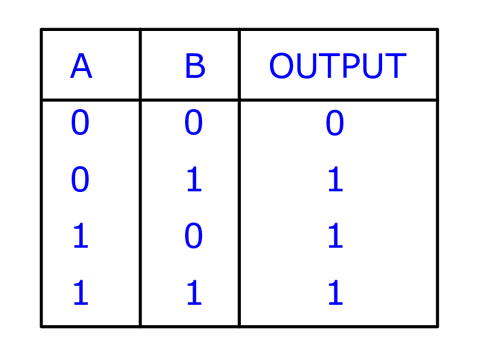

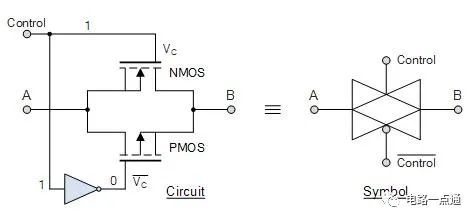

OR门的电路符号如图1所示,弯曲端是输入端,尖端是输出端。他们遵循的逻辑很简单,如果任何一个输入为真或输入 A或输入 B 为真,则输出为真。或门真值表如下所示。

该原理可以扩展到所需的任意数量的输入,如果任何一个(或至少一个)输入为真,则输出为真。在本文中,我们将使用晶体管构建 OR 逻辑门,如果您想了解更多关于 OR 门以及它们如何工作的信息,您可以查看OR 门文章的基础知识。

所需零件

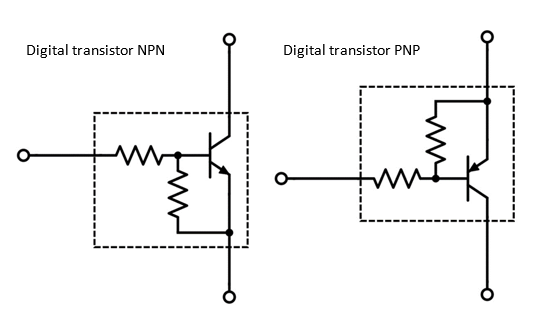

NPN小信号晶体管(2N2222、BC547等)

1K电阻

10K 电阻

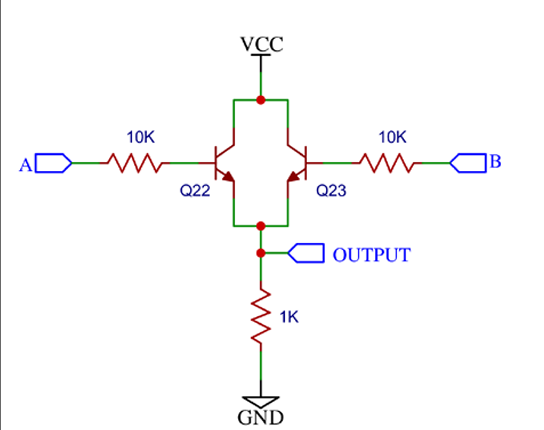

使用晶体管的或门 - 电路图

OR门的第一个版本是最简单的——它由两个并联的发射极跟随器共享一个公共发射极电阻器组成。

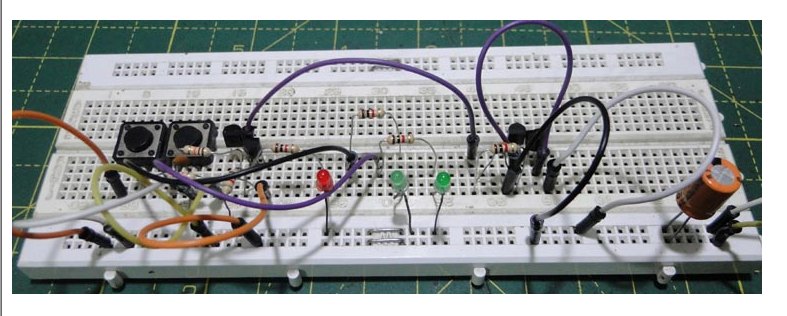

上面的电路图显示了使用 NPN 晶体管构建或门的最简单方法。当输入 A 保持高电平时,小电流通过晶体管 Q22 的基极。这会打开 Q22,并且(相对)大电流从集电极流向发射极。电流在发射极电阻上下降。发射极电阻两端的电压为 V CC – 0.7V,因此输出“跟随”输入,增益略小于单位。当输入B 保持高电平时也会发生同样的事情。 当两个输入都保持高电平时,两个晶体管都处于活动状态,但发射极电阻上的电压降相同,输出仍然是高电平。该电路显示出完美的 OR 行为。将开关和 LED 连接到输入可以更好地显示电路的行为,如下图所示。

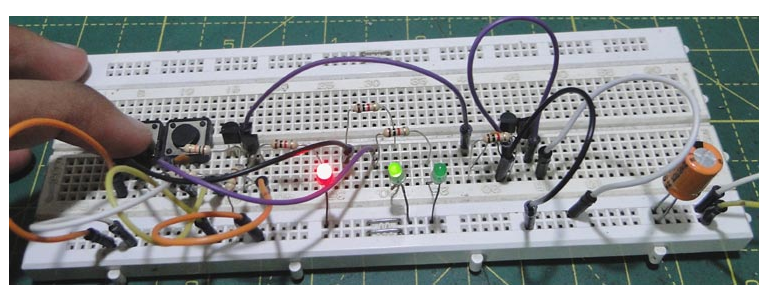

情况1:当两个输入都为低时,输出为低

情况2:当一个输入为低,另一个为高时,输出为高

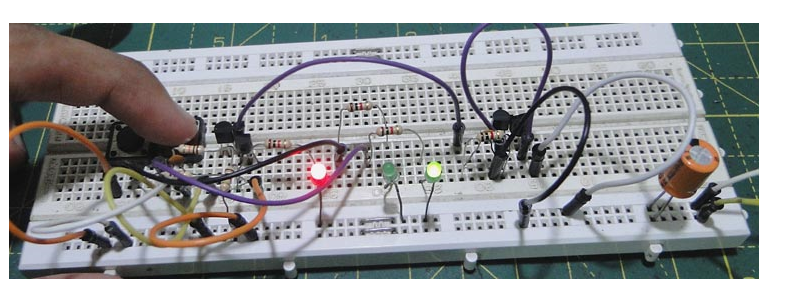

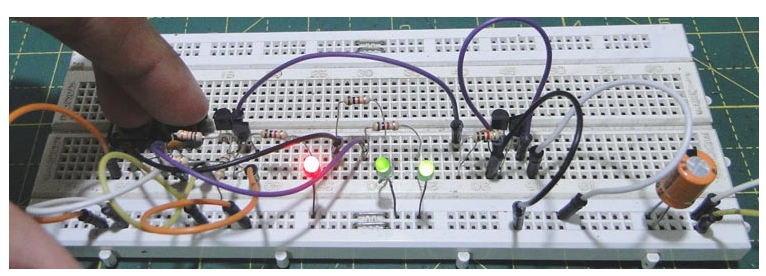

情况3:反之亦然,当其他输入为低时,输出为高

案例4:最后当两个输入都为高时,输出为高

如您所见,电路正在工作并遵循我们之前讨论的真值表。如果您对这条粗略的电路感到满意,您可以在这里停下来,但如果您想对电路进行一些改进,请继续阅读。

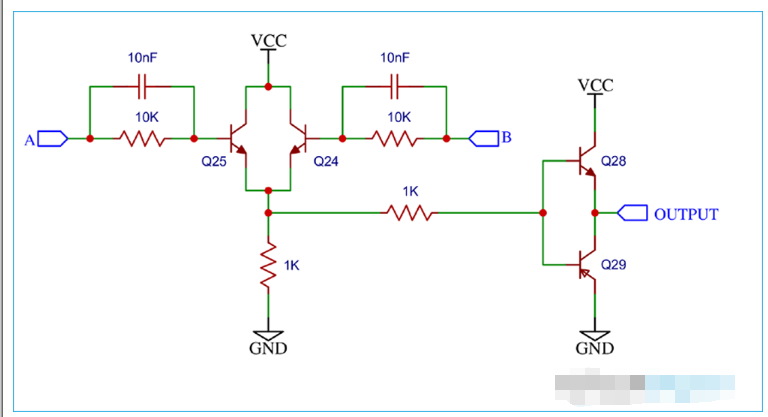

使用晶体管的或门 - 改进版

上面显示的电路是 OR 门的一个非常简单的实现,但由于一些原因,该电路很少用于 IC 制造。如果我们将一个输入连接到 V CC,将一个开关连接到另一个输入并探测输入和开关并在开关的上升沿触发,我们会注意到一个小问题。

输出仅在一段时间后才变为高电平,即不会立即响应输入。在输出端看到输入所花费的时间称为传播延迟。删除输入时也会发生同样的事情。输出需要一些时间才能回到地面。

这是因为晶体管的基极电容。一种解决方案是降低所有电阻器的值,以便更多电流流动并且电容快速充电。但这会导致过多的功耗。为了避免这种情况,我们在基极电阻上添加了两个小的(《10nF)“加速”电容器,以减少“存储”时间。

另一个问题是这个电路不能像它提供的那样吸收尽可能多的电流。采购不是问题,因为至少有一个晶体管打开(当至少一个输入为高电平时)直接连接到输出,因此输出可以提供相当大的电流。

然而,当晶体管关闭时,只有 1K 电阻将输出拉低,并且吸收电流受到限制。为了使驱动对称,增加了一个输出推挽级。这两种修改都大大减少了上升和下降传播延迟。

或门的应用

与与门一起,或门构成了所有逻辑电路的一个组成部分。例如,如果微控制器需要监控十个输入,则一个 10 输入或门将告诉控制器是否有任何一个输入为高电平,而无需十个输入引脚。

逻辑或的另一个有趣应用是在您的汽车中。仅当所有车门都关闭时,安全带警告灯才会关闭,换句话说,如果任何一扇(或至少一扇)车门打开,警报就会亮起。

-

逻辑门

+关注

关注

1文章

142浏览量

24048 -

晶体管

+关注

关注

77文章

9684浏览量

138094 -

或门

+关注

关注

1文章

17浏览量

10476

发布评论请先 登录

相关推荐

如何使用晶体管设计或门

如何使用晶体管设计或门

评论