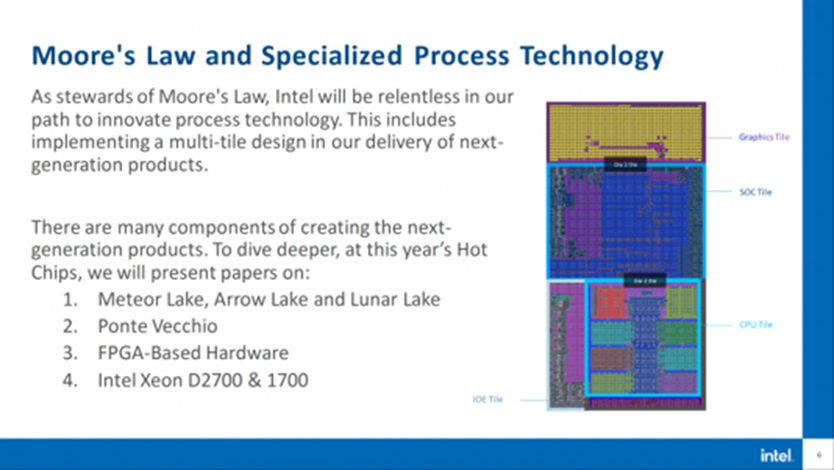

在半导体行业会议 Hot Chips 34 上,英特尔展示了2.5D和3D芯片块(tile)设计所需的创新架构和封装技术,这些技术将引领芯片制造进入新时代,并在未来数年内推动摩尔定律的发展。

英特尔首席执行官Pat Gelsinger(帕特·基辛格)分享了公司即将推出的一系列产品细节,包括Meteor Lake、Arrow Lake、Lunar Lake 、Ponte Vecchio GPU、Intel Xeon D-2700与D-1700以及FPGA,并概述了其新的系统晶圆代工模式。

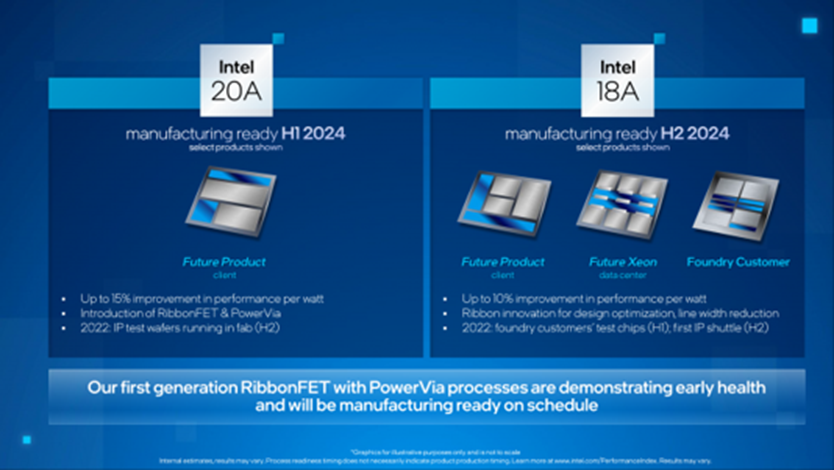

Pat Gelsinger 指出,英特尔在新产品中结合了如RibbonFET 、 PowerVIA 、 High-NA 微影制程以及2.5D 、3D 封装技术, 另外英特尔还设下了从当前单一封装1千亿个晶体管进步至2030年1兆个晶体管的目标。

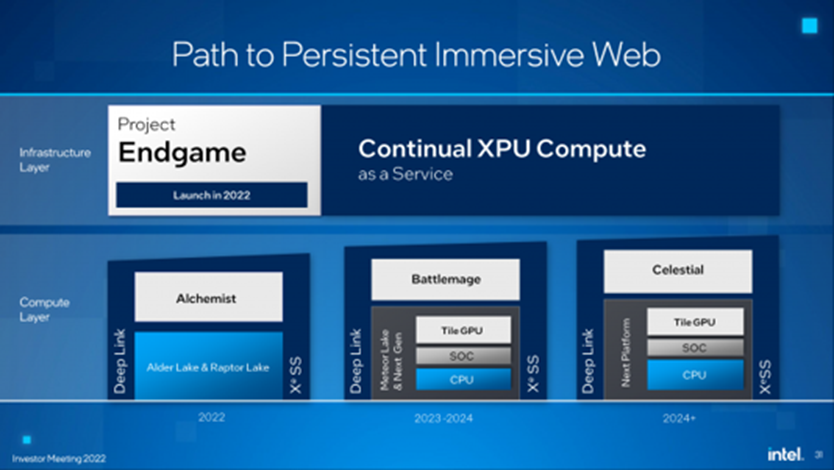

同时英特尔也指出当前是半导体新技术发展的黄金时代,晶圆制造需要自以往单一晶圆代工的思维转型至微系统晶圆代工。英特尔的系统晶圆代工模式可以结合更先进的封装、开放的小芯片(chiplet)生态系统和软件组件,通过组装和提供系统单封装(systems in a package)的方式,满足全球对于运算能力和全面沉浸式数字体验永无止境的渴求。英特尔也通过持续推进先进制程工艺和芯片块设计,来满足产业需求。

英特尔在Hot Chips 34 提供了多款即将上市的产品架构预览。

14 代 Meteor Lake、15 代 Arrow Lake、以及 16 代 Lunar Lake 系列

这些处理器具有如下特点:

● 英特尔下一代 3D 客户端平台;

● 具有 CPU、GPU、SOC 和 IO Tiles 的分解式 3D 客户端架构;

● 采用基础块的 Meteor Lake 和 Arrow Lake,辅以 Foveros 互连;

● 基于 UCIe 通用小芯片互连的开放式生态系统。

Meteor Lake 是英特尔打入客户端小芯片生态系统的第一步。4-Tile 布局中包括了 CPU、GPU、SoC 和 IOE 块,并且它们基于不尽相同的工艺节点。比如主 CPU tile使用了 “Intel 4”(7nm EUV)工艺节点,而 SoC 和 IOE tile则是基于台积电 N6 工艺。

不过英特尔准备如何部署其 tGPU 图形tile呢?

起初有传闻称,英特尔有意采用台积电 3nm 工艺节点,但出于某些原因而中途改变了计划,转而采用台积电 5nm 工艺节点。不过,Meteor Lake CPU 的 tGPU,也一直都是照着台积电 5nm 方案去设计的。

来源:cnBeta

其次,随着下一代先进晶圆的成本增加,单芯片的研发成本也在水涨船高。尽管英特尔可以选择咬牙为 Meteor Lake 用整体设计,以带来更强的竞争力。但高昂的定价,或难以吸引到足够多的客户。

此外以 6P+4E 的移动芯片产品线为例,在 CPU / IOE tile、以及通向 SoC Tile 的 Graphics Tile 之间有两个 Die-to-Die 连接。英特尔表示,这其实是 Foveros 3D 封装的一部分,且在主力小芯片顶部有一个基于自家 22nm FFL 工艺的无源中介层。虽然目前该中介层尚未发挥任何用途,但该公司确有计划在未来使用更先进的封装技术、并在其中使用有源的小芯片。在 MeteorLake CPU 上,也尚未使用到 EMIB 技术。

来源:cnBeta

然后是 14 代 Meteor Lake 和 15 代 Arrow Lake CPU,英特尔证实其正在向桌面和移动平台发展。作为下一代 LGA 1851 平台的主力,前者目标是 2023 年发布,后者则是 2024 年。

至于 16 代 Lunar Lake CPU,据说该系列最初是为 15W 的低功耗移动 CPU 细分市场而考虑的。但鉴于距离产品推出还有数年时间,期间也难免会迎来一些改变。

来源:cnBeta

值得一提的是全新tile架构的 14 代 Meteor Lake,将为游戏玩家带来崭新的体验。其基于“Intel 4”(7nm EUV)工艺节点,可将每瓦性能提升 20%,并计划于 2022 下半年前流片。如果一切顺利,首批 Meteor Lake 将于 2023 年上半年发货、并于同年晚些时候上市。在CPU 架构方面,预计该系列芯片会采用 Redwood Cove 高性能 P 大核 + Crestmont 小核(E 核)。尽管 P 核与 Golden Cove / Raptor Lake 有许多相似之处,但 E 核将迎来重大的架构变化。

来源:cnBeta

紧随其后的是使用“ Intel 20A” 工艺节点的 15 代 Arrow Lake,尽管插槽与 Meteor Lake 兼容,但大小核升级到了 Lion Cove + Skymont 。随着新 SKU(8P+32E)核心数量的增加,英特尔希望借此带来更大的竞争优势。不过更让人感到惊讶的,还是英特尔直接跳过了“Intel 4” 节点,为其选用了“ Intel 20A”工艺。框图显示 Meteor / Arrow Lake 分别拥有 3 / 4 个tile,但后者仍有大量细节有待揭晓。

同时 Meteor / Arrow Lake 将为额外的核心 IP 保留台积电 N3 工艺节点,推测会用于 Arc GPU 核显。另外“ Intel 20A”节点将受益于下一代 RibbonFET 和 PowerVia 技术,每瓦性能提升 15%、并计划于 2022 下半年前开测首批晶圆。

最后是全新的 16 代 Lunar Lake 大平台,凭借更新的“ Intel 18A”工艺节点,其不仅可在性能上占据优势、还有望在能效上领先于竞争对手。与“ Intel 20A”节点相比,其每瓦特性能提升 10%、利用了增强的 RibbonFETRR 设计、并减少了线宽。若能在 2024年下半年顺利投产,Lunar Lake 将于 2025 年的某个时候正式发布。

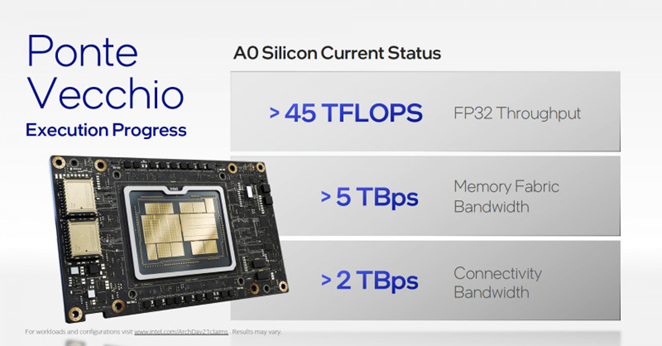

数据中心级 GPU Ponte Vecchio

Ponte Vecchio 是英特尔首款针对 HPC 级数据中心所开发的超高效能 GPU 产品,以多个复杂设计的芯片块以及嵌入式多芯片互连桥接( EMIB )与 Foveros 先进封装连接,再透过 MDFI 互连扩展到两个堆叠,使单一封装包含超过 1 千亿个晶体管,再辅以英特尔开放软件模型,以One API简化API抽象与块架构设计。

为5G 物联网、企业与云端应用设计的Xeon D-2700 与Xeon D-1700

这两系列芯片是英特尔为顺应新时代网络基础与物联网应用所开发的,特别考虑到实际场域的功耗与空间限制,通过芯片块设计,整合先进运算核心、可灵活运用封包处理器的100G以太网络、内嵌加密加速、时间协调运算(TCC )、时效性网路( TSN )与AI处理最佳化。

高性能和具有高度弹性的硬体加速工具 FPGA

FPGA 向来都是具备高度弹性的硬件加速工具,尤其近日更在射频领域发挥了相当大的潜力,英特尔借助整合数字与模拟芯片块,融合了来自不同制程节点、不同晶圆代工厂的芯片块,提供具备新效率、可缩减开发者时间与最高灵活性的设计。

审核编辑 :李倩

-

英特尔

+关注

关注

61文章

9946浏览量

171685 -

封装技术

+关注

关注

12文章

547浏览量

67981 -

晶圆代工

+关注

关注

6文章

859浏览量

48576

原文标题:Hot Chips 34 :英特尔透露多款3D芯片创新架构与封装技术

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英特尔推出全新实感深度相机模组D421

IBM Cloud将部署英特尔Gaudi 3 AI芯片

新思科技面向英特尔代工推出可量产的多裸晶芯片设计参考流程,加速芯片创新

英特尔CEO:AI时代英特尔动力不减

m3芯片相当于英特尔几代cpu m3芯片相当于英特尔什么显卡

Ansys和英特尔代工合作开发多物理场签核解决方案

最新技术!英特尔于IFS Direct Connect会议上公布3D芯片技术、逻辑单元、背面供电等未来代工技术!

英特尔透露多款3D芯片创新架构与封装技术

英特尔透露多款3D芯片创新架构与封装技术

评论