随着数据传输速率越来越高,现在计算机系统中的数据传输接口基本上都串行化了,像USB、PCIe、SATA、DP等等外部总线将并行总线挤压到只剩下内存总线这个最后的堡垒。当然,就算是并行传输总线最后的倔强DDR也在不断吸收SERDES上的技术来提升自己,尤其是均衡器(Equalization,EQ)技术,在DDR5标准中,DRAM将被指定涵盖DFE(判决反馈均衡)能力。

随着信号速率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。

并行数据各个bit 的传播延时不相等(data skew)

时钟的传播延时和数据的传播延时不一致(skew between data and clock)

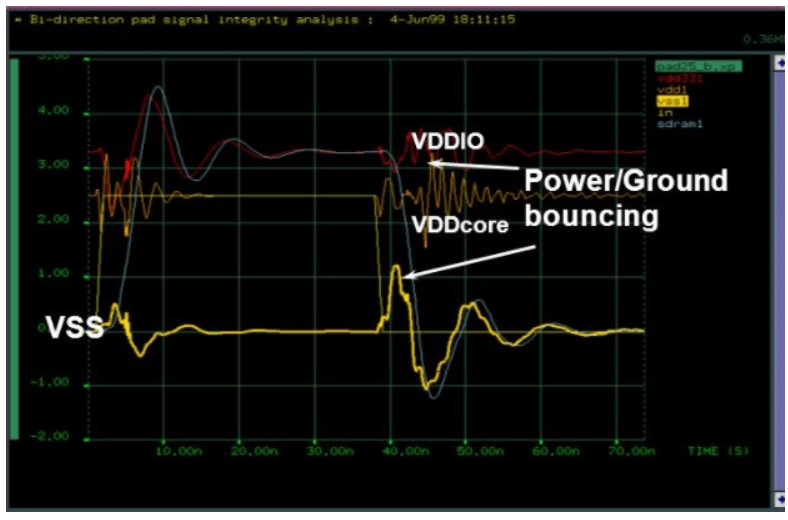

要提高接口的传输带宽有两种方式,一种是提高时钟频率,一种是加大数据位宽。那么是不是可以无限制的增加数据的位宽呢?这就要牵涉到另外一个非常重要的问题–同步开关噪声(SSN),数据位宽的增加,SSN 成为提高传输带宽的主要瓶颈。

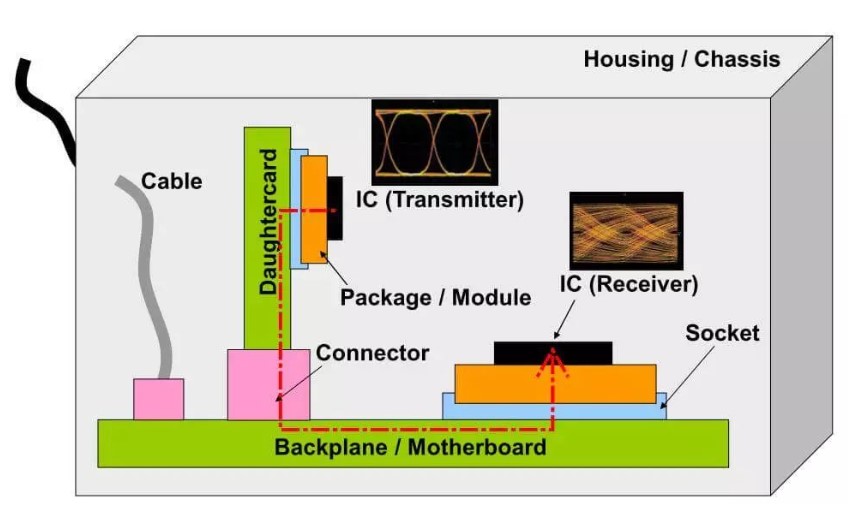

由于信道的非理想特性,信号从Tx通过FR4 PCB板传输到Rx,这中间会有信号插损、回损、近/远端串扰,再继续提高频率,信号会严重失真,这就需要采用均衡和数据时钟相位检测等技术,这也就是SerDes所采用的技术。

单端信号和差分信号之间的差异

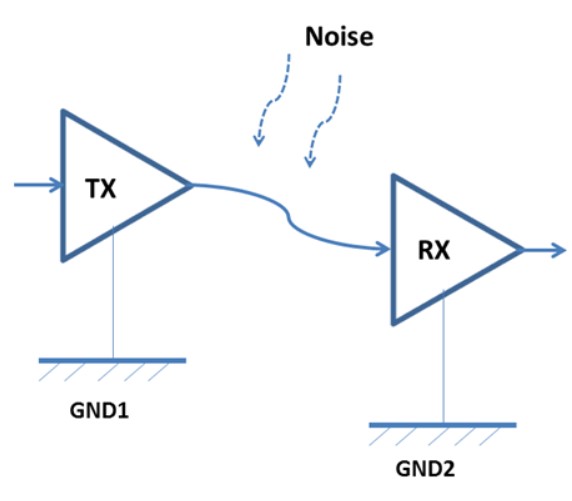

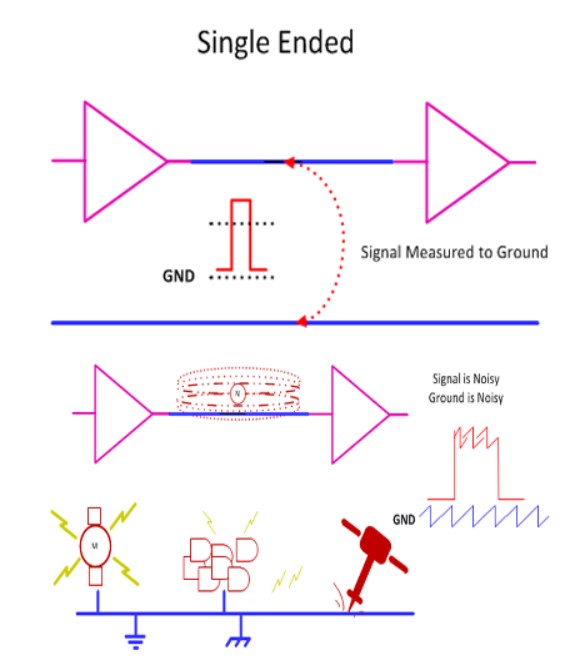

单端信号即用一根走线来传输信号,信号由相对于地参考平面(0V GND)的电平来确定逻辑“ L”和逻辑“ H”,例如TTL接口或CMOS接口,是单端信号。

随着速率的提高,单端信号的上升/下级沿也变得陡峭,因此,输出开关噪声会导致信号产生过冲和下冲,并且当多位信号同时转换时,还要考虑地弹(ground bounce)问题,同时,单端信号以参考地平面作为信号回流路径,这也为Layout带来了挑战,由传输线阻抗不匹配引起的反射效应会变得非常严重。

差分信号

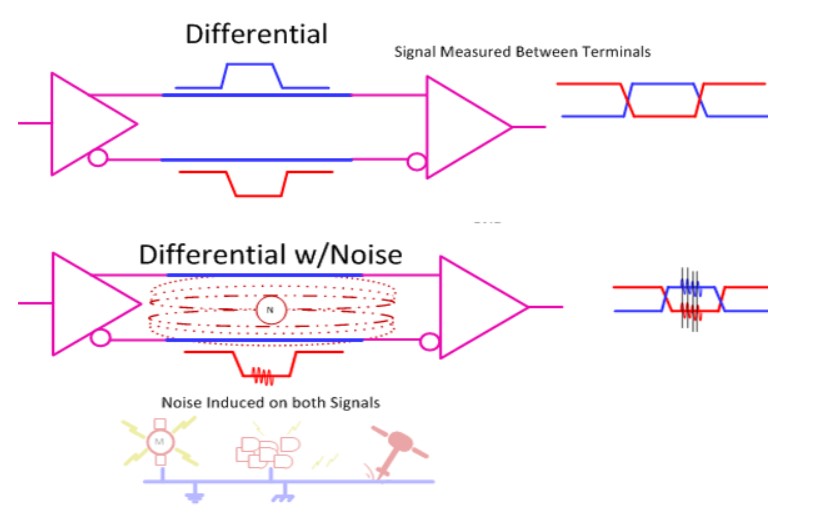

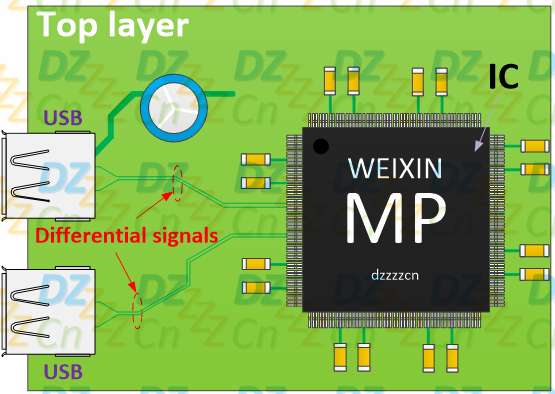

差分信号有别于单端信号一根信号线传输信号然后参考GND作为高(H)、低(L)逻辑电平的参考并作为镜像流量路径的做法,差分传输在两根传输线上都传输信号,这两个信号的振幅相等,相位相差180度,极性相反,互为耦合。

差分信号的优点

差分信号的第一个好处是,因为你在控制「基准」电压,所以能够很容易地识别小信号。在一个参考地做「0 V」基准的单端信号传输系统里,测量信号的精确值依赖系统内「0 V」的一致性。信号源和信号接收器距离越远,他们局部地的电压值之间有差异的可能性就越大。从差分信号恢复的信号值在很大程度上与「地」的精确值无关,而在某一范围内便可。

差分信号的第二个主要好处是,它对外部电磁干扰(EMI)是高度免疫的。一个干扰源几乎相同程度地影响差分信号对的每一端。既然电压差异决定信号值,这样将忽视在两个导体上出现的任何同样干扰。除了对干扰不大灵敏外,差分信号比单端信号生成的EMI还要少。

差分信号提供的第三个好处是,在一个单电源系统,能够从容精确地处理「双极信号」。为了处理单端,单电源系统的双极信号,我们必须在地和电源干线之间某任意电压处(通常是中点)建立一个虚地。用高于虚地的电压来表示正极信号,低于虚地的电压来表示负极信号。接下来,必须把虚地正确地分布到整个系统里。而对于差分信号,不需要这样一个虚地,这就使我们处理和传播双极信号有一个高真度,而无须依赖虚地的稳定性。

随着集成电路的发展和对更高数据速率的要求,低压供电成为急需。降低供电电压不仅减少了高密度集成电路的功率消耗,而且减少了芯片内部的散热,有助于提高集成度。减少供电电压和逻辑电压摆幅的一个极好例子是低压差分信号(LowVoltageDifferentialSignalingLVDS)。

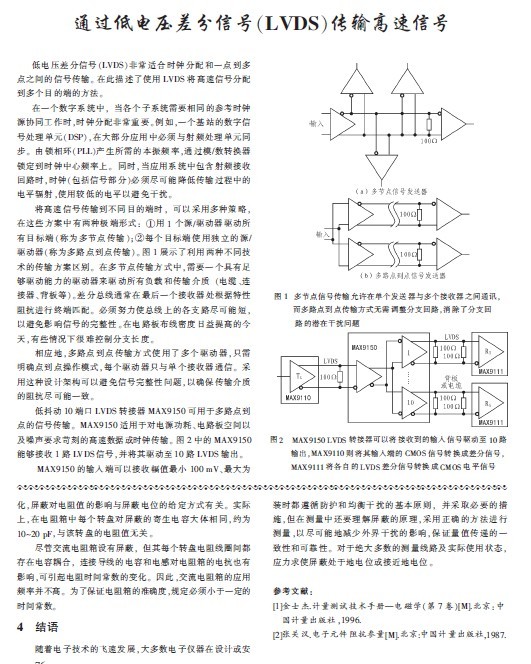

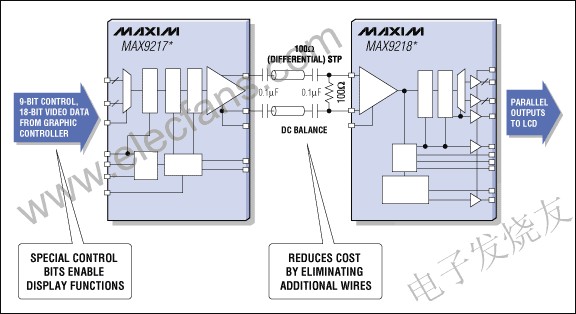

低电压差分信号(LVDS)是一种高速点到点应用通信标准。多点LVDS (M-LVDS)则是一种面向多点应用的类似标准。LVDS和M-LVDS均使用差分信号,通过这种双线式通信方法,接收器将根据两个互补电信号之间的电压差检测数据。这样能够极大地改善噪声抗扰度,并将噪声辐射降至最低。

LVDS是一种用于替代发射极耦合逻辑(ECL)或正发射极耦合逻辑(PECL)的低功 耗逻辑 。LVDS的主要标准是TIA/EIA-644。有时也会对LVDS使用另一种标准,即IEEE 1596.3—SCI(可扩展一致性接口)。LVDS广泛用于高速背板、电缆和板到板数据传输与时钟分配,以及单个PCB内的通信链路。

LVDS的优势包括

通信速度高达1 Gbps或以上

电磁辐射更低

抗扰度更高

低功耗工作

共模范围允许高达±1的接地失调差额

M-LVDS

面向多点低电压差分信号(M-LVDS)的标准TIA/EIA-899将LVDS延伸到用于解决多点应用中的问题。相对于TIA/EIA-485 (RS-485)或控制器局域网(CAN),M-LVDS能够以更低的功耗实现更高速度的通信链路。

M-LVDS相对于LVDS的额外特性包括

驱动器输出强度更高

跃迁时间可控

共模范围更广

面向总线空闲条件提供故障安全接收器选项

为什么使用LVDS或M-LVDS?

图1中将LVDS和M-LVDS与其他多点和点到点协议进行了比较。两种标准都有低功耗要求。LVDS和M-LVDS的特征是在差分电压摆幅较低的情况下实现差分信号。相对于LVDS,M-LVDS指定了更高的差分输出电压,以便允许来自多点总线的更高负载。

两种协议都是面向高速通信设计的。典型应用环境下会采用PCB走线或较短的有线/背板链路。LVDS的共模范围就是针对这些应用而设计。相对于LVDS,M-LVDS扩展了其共模范围,允许多点拓扑结构中具有额外噪声。

LVDS/M-LVDS应用考虑

总线类型和拓扑结构

时钟分配应用

LVDS/M-LVDS信号的特性

端接和PCB布局

抖动和偏斜

数据编码和同步

隔离

审核编辑:刘清

-

数据传输

+关注

关注

9文章

1878浏览量

64544 -

lvds

+关注

关注

2文章

1042浏览量

65784 -

DRAM芯片

+关注

关注

1文章

84浏览量

18011 -

低压差分信号

+关注

关注

0文章

11浏览量

9590

发布评论请先 登录

相关推荐

差分信号的优势和影响

通过低电压差分信号(LVDS)传输高速信号

通过低电压差分信号(LVDS)传输高速信号

ADI推出多点低电压差分信号收发器ADN469xE

一文详解LVDS低电压差分信号

LVDS振幅差分信号技术的优势和劣势

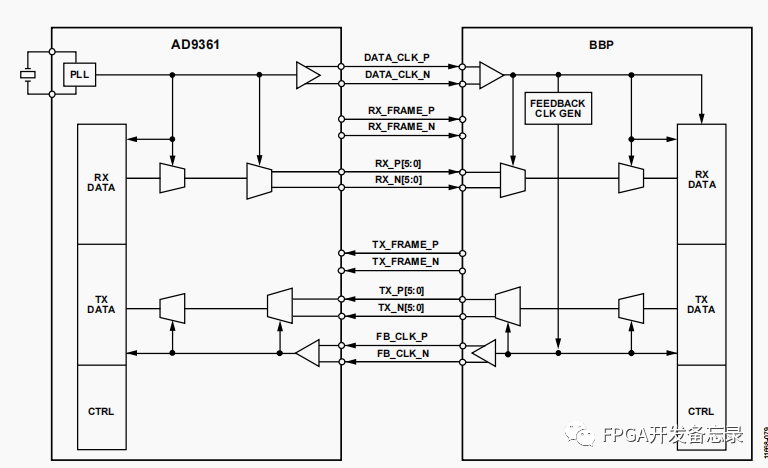

AD9361数据路径在低电压差分信号(LVDS)模式下运行

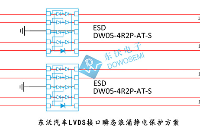

低电压差分信号(LVDS)接口浪涌静电放电防护电路图

低电压差分信号(LVDS)是什么?有哪些优势

低电压差分信号(LVDS)是什么?有哪些优势

评论