在超越摩尔定律的技术方向上,业界有很多热议,最热门的莫过于通过更先进的工艺制程来提升单位面积内晶体管的密度。然而,出于成本和技术难度等多方面的考虑,并非所有设计都需要采用7nm、5nm甚至3nm这样的高阶制程。随着单片集成的成本不断上升,许多企业开始探索其他选择,先进的封装技术如2.5D和3D系统级封装(SiP)就是其中的热门选项。

目前,业界正在努力使用先进的封装技术将多个先进的,也可以是成熟的“小芯片”放在一个封装中(也被称为异构集成),与3D封装一起,在系统级扩展摩尔定律。这就是目前半导体行业的热门技术——Chiplet。

什么是Chiplet?

Chiplet也称为“小芯片”或“芯粒”,它是一种功能电路块,包括可重复使用的IP块。出于成本和良率等考虑,一个功能丰富且面积较大的芯片裸片(die)可以被拆分成多个小芯片,这些预先生产好的、能实现特定功能的小芯片组合在一起,借助先进的集成技术(比如3D封装)被集成封装在一起即可组成一个系统芯片。

Chiplet技术有很多优势:

首先,通过把大芯片分割成较小的芯片,可有效改善生产的良率,降低制造成本。

其次,可根据不同IP的需求,选择适合的工艺节点,从而显著提高制造良率,进一步节约成本——比如数字IP可以使用高阶工艺制程以达到我们期望的高性能,而模拟IP可以选用更经济、更成熟的工艺技术,同样能达到设计效果。

还有一个突出优势,那就是一些经过验证且技术成熟的小芯片可以重复使用,这样做既减少了企业的设计时间和成本,还能有效扩充企业的资源库。

当然,硬币都有两个面,Chiplet亦如此。从制程节点和良率角度看,Chiplet制造成本肯定是降低了,但因为被分割的这些小芯片在功能上(如I/O控制)是分开的,其功能可能很难再扩展。另外,将大芯片分割成多个小芯片然后再堆叠起来,封装的成本可能会有一定的增加。

为什么需要Chiplet?

在讨论为什么需要Chiplet之前,先让我们来看看半导体制造业有多烧钱。

2021年初,台积电(TSMC)宣布将其2021年资本支出预算大幅提升至250亿至280亿美元,并随后还将其进一步提升至300亿美元左右。在TSMC的投资中,有较大一部分资本支出应该是用于购买EUV光刻机。在今年第三季度财报发布会上,ASML总裁兼首席执行官Peter Wennink表示:公司第三季的营收达到52亿欧元。第三季的新增订单金额达到62亿欧元,其中29亿欧元来自EUV系统订单,客户对于光刻系统的需求仍在高点。预期2021年第四季的营收约为49亿欧元到52亿欧元,研发成本约6.7亿欧元。三星在5nm制程节点的投资和努力在业界有目共睹,遗憾的是其良率不足50%,一直没有达到预期,现在公司正在其华城工厂的V1产线部署昂贵的EUV光刻机,希望借此提高良率。

随着芯片制造成本的大幅上升,并不是每家企业都能承担得起动辄几亿元的芯片流片费用,一个保险的方式就是——把成熟的大芯片分割成多个小芯片,再借助SiP封装技术将它们整合到一起——这样就产生了对Chiplet SiP的需求。

Chiplet为企业提供了一种创建更高级设计的替代方法,以最具成本效益的方案,将设计的晶体管数量增加到超出单个大芯片所能容纳的数量,实现晶体管数量“超摩尔”的增益。这也是业界一直对Chiplet抱有极大期望的重要原因。

Chiplet进化史

多年来,SiP技术一直是半导体封装行业的焦点。来自Yole的数据表明,SiP市场预计将从2020年的140亿美元增加到2026年的190多亿美元。自20世纪90年代以来,SiP就以多芯片模块(MCM)的形式出现,虽然各公司的定义有些差别,但作用是一致的,即SiP可以将芯片、无源器件,甚至包括MEMS等全部组合在一起合并到一个封装中。Chiplet其实也可以算是一种SiP技术,是系统级芯片(SoC)中IP模块的芯片化。

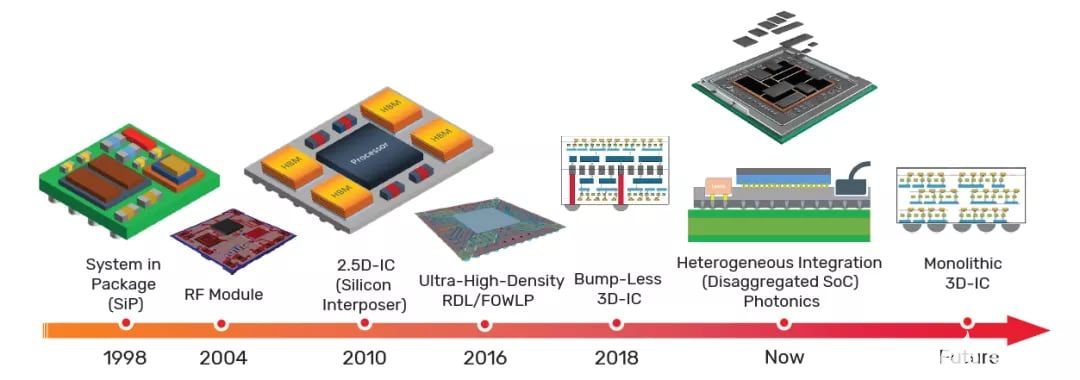

图1:先进的多芯片封装演进路线图(图源:Cadence)

SiP与Chiplet这两种技术均解决了在每个新节点上开发SoC的难度和成本不断增加的问题。对于Chiplet而言,供应商或封测企业可能会因此而建立起一个拥有各种功能的小芯片IP库。长此以往,公司的知识产权将得到极大丰富。如果将这些IP用于新产品开发,将缩短产品的上市时间。

Chiplet市场的知名供应商

事实上,Chiplet并不是一个全新的概念,如同SiP、异构集成以及MCM一样已经存在了很长时间。许多主要芯片制造商都在大力支持这项技术,AMD、英特尔(Intel)和TSMC都宣布或推出了Chiplet产品,只是它们的实现方式会有所不同。

TSMC Chiplet解决方案

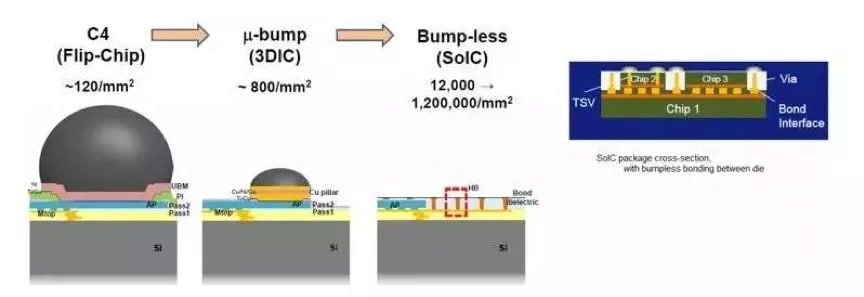

TSMC提出了无凸点系统集成芯片(SoIC)。作为Chiplet解决方案,SoIC是一种3D结构,由带TSV的有源插入器上的逻辑、存储器或两种芯片类型堆叠而成,采用晶圆上芯片(CoW)工艺,可处理芯片之间<10µm的焊盘间距。它的创新在于实现了从管芯和基板之间的微凸点连接过渡到直接管芯连接之间的无凸点(热压)键合的转变。TSMC的报告显示,SoIC与使用TSV和40µm间距微凸点的传统3D IC相比,具有更高密度键合的结构,提供了更好的信号完整性、功率完整性和更低的通信延迟以及更大的带宽。

图2:凸点和无凸点技术特性与SoIC封装的比较(图源:TSMC)

AMD Chiplet解决方案

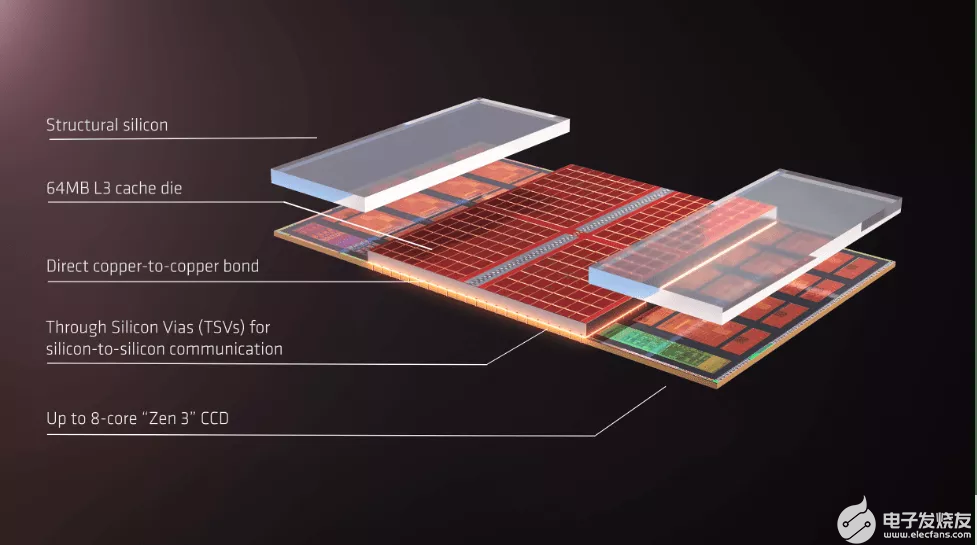

AMD目前的Chiplet解决方案采用了层压基板,并且已经推出基于Chiplet技术的多个版本的服务器处理器。在今年的Computex上,AMD发布了基于3D Chiplet技术的3D V-Cache实验性的产品。它使用了TSMC的3D Fabric封装技术,将包含有64MB L3 Cache的Chiplet以3D堆叠的形式与处理器封装在一起,在系统层面,它就像一个单片芯片。这种新的体系结构将使处理器的性能得到显著改善,且不会带来更多的功耗,这是单片集成所无法达到的。

图3:AMD基于3D Chiplet技术的3D V-Cache处理器(图源:AMD)

Intel Chiplet解决方案

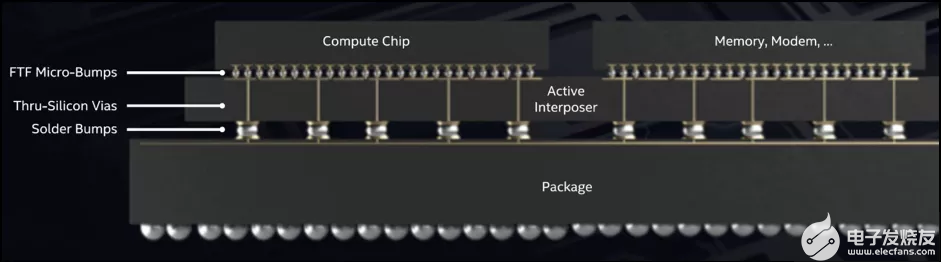

Intel的Chiplet解决方案称为Foveros。作为异构系统集成的一种形式,Foveros技术将为设计人员提供更大的灵活性,使他们能够将具有各种内存和I/O元素的IP块混合并匹配到一起。接下来。Intel预计将在许多产品线中利用这项技术。

图4:具有3D face-to-face堆叠的Foveros技术(图源:Intel)

结语

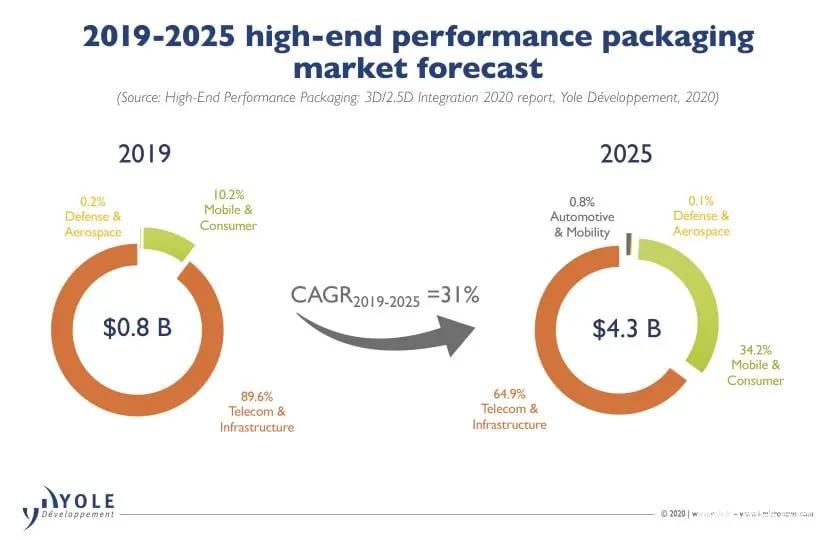

2019年之前,高性能封装在DRAM、HBM和FPGA中商业化的势头非常强劲,主要用于各种处理器的制造,包括处理器内核、SSD、内存块,以及图形等应用中的CPU和GPU。根据Yole的报告,2019年高端封装市场价值8.71亿美元,预计到2025年将达到43亿美元,2019年至2025年的复合年增长率为31%。

图5:高端半导体封测市场预测(图源:Yole)

近些年,关于“摩尔定律已死”的报道时常见诸报端。现在,半导体工业已经进入了一个新的时代,在此期间,先进的封装技术将发挥越来越重要的作用,因为行业再也不能仅仅依靠单片集成来实现更高的性能,同时还要保持较高的经济效益。Chiplet是一种异构集成解决方案,它正在把我们带入下一个半导体时代。届时,摩尔定律有望以一种新的方式或途径得以延续。

审核编辑 黄昊宇

-

芯片

+关注

关注

463文章

54410浏览量

469159 -

摩尔定律

+关注

关注

4文章

640浏览量

81146 -

chiplet

+关注

关注

6文章

499浏览量

13645

发布评论请先 登录

什么是摩尔定律?

为摩尔定律“续命”,Chiplets技术能行吗?

为摩尔定律“续命”,Chiplets技术能行吗?

评论