很久没有分享自己的debug过程了,实在是因为这种过程需要介绍太多的背景故事,不是容易很详细的展开。

不过今天想跟大家分享的只是一个很简单的double tail comparator,没有那种很复杂的故事需要先聊上好久,所以想着写文章也是记录也是分享也是学习(有时候有很棒的评论,我也能学到很多,谢谢很多热心读者!),今天大致说一下这个comparator的debug过程。

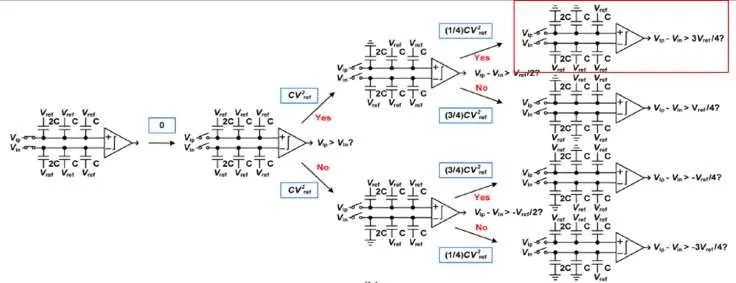

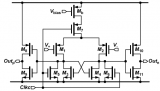

我之前帮人做了一个大概200MHz的10 bits SAR ADC的comparator,SAR用的是大家经常看到的(比如之前我提过的CC Liu那篇经典JSSC)结构。comparator则是double tail comparator。

Liu, Chun-Cheng, Soon-Jyh Chang, Guan-Ying Huang, and Ying-Zu Lin. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure.; IEEE Journal of Solid-State Circuits 45, no. 4 (2010): 731-740

前仿PVT,MC我都跑了一遍,看起来做的还行。于是心里有底气的我,就把这个comparator交给了做ADC的同事。我抽了版图寄生的av_extracted coupled c之后,又单独跑了后仿,看起来也还行。于是我又交给了同事做ADC的后仿。然后……同事跟我说中间大概第六七步的时候就比出来的结果错了,而且只是tt就错了……

这感觉有点打脸了-_-

作为一个包售后的designer,我定然是义不容辞的要去debug了。于是我做了下面这些事情。

首先,我拿着ADC后仿的test bench研究了一下。

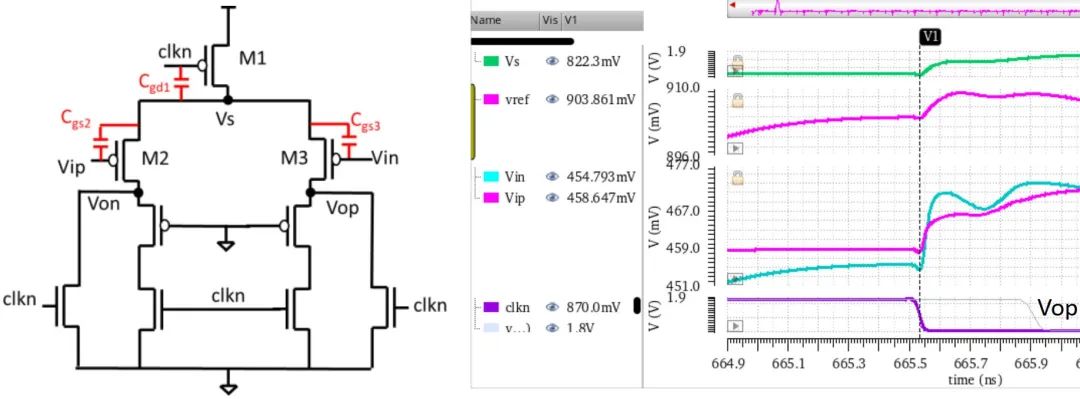

因为是pmos的input pair,第一级的clock都是clkn控制的。所以,当clkn从1变成0的时候,发生了什么?右边波形图的第一行是M1的drain端Vs,第三行,是两个输入端vip和vin,第四行的紫色线是clkn,很浅的灰色线是vop。当clkn还没变化的时候,很明显,vin是小于vip的,所以vop应在clkn变成0之后继续保持1.但是,它怎么了?干嘛掉下去了?

再仔细看看我放置V1的那条虚线(在viva上面按v就行),clkn下降沿来的时候,vip和vin都往下掉了一点点。为什么会掉下去?

重新看左图电路,我画了M1的Cgd1和input pair的Cgs。这种瞬间变化的“奇景”,在电路里最常见的就是电容之间的电荷传导了。(电容很快的,啪的一下就过去了,它们不讲武德的^_^)想想要是mosfet的传导,还得先从反型层开始,然后沟道电荷,然后才能导通,明显多了几步,自然慢了对吧?所以clkn的1->0使得Cgd1上面的电荷被抽走了一些(我拿正电荷打比方,比较直观),下面的两个Cgs跟着上面的老大哥被吸走一点电荷,所以让vip和vin掉下去了一点点。

看来看去,vip和vin好像掉的也不多,作者君这个慢一拍的家伙分析这个干啥?

想想看,既然是寄生电容之间的短兵相接,是不是可以从寄生电容身上找找办法?

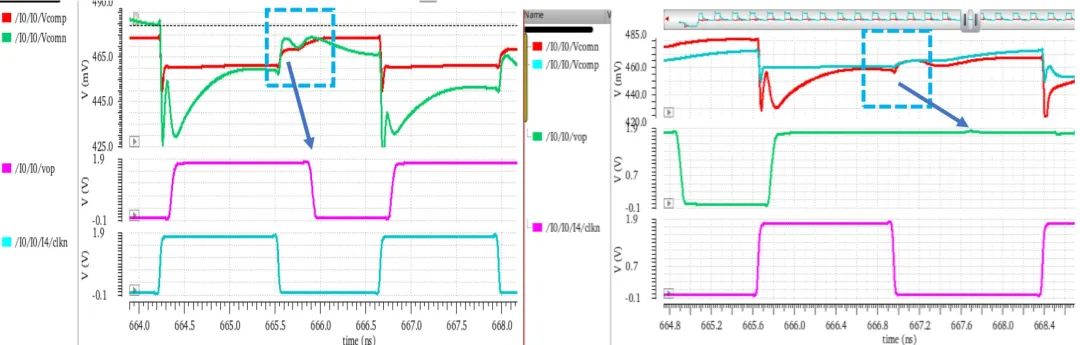

作者君有个大胆的想法,于是做了一个尝试:最初的版本里面,M1的Width是8um,右边的图里,M1的width被改成了2um。呵呵呵,因为M1的Cgs1减小了,果然后续的影响没有那么大了(蓝色虚线框里),可以看到第二行里面的vop就没掉下来,结果对了!

(不过呢,看一下蓝色箭头,右边vop的输出比左边慢了不少。当然会慢:上面M1减小了这么多,等于之后整个第一级的总电流受限了,想想这样带来的潜在影响有点大啊!万一太慢了导致时间不够用,岂不是很惨?)

粗暴减小M1的方法暂时按下不表。

其实呢,万物之间皆有关联……好高深的样子!不是,上面右图里面第二行那个verf是什么东西?作者君画这个干什么?

当然是有用的啦!这个vref就是C.C.Liu那个图里的verf了。比如我的VDD是1.8V,选个合适的vref比如说0.9V,input swing就是1.8V了。(这个ADC的capacitor array就是不停的被在vref和vss之间顶来顶去的)

一个理想的LDO,加上一个理想的buffer,给我一个理想的0.9V。很可惜,现实很骨感,哪有那么好的vref?上面第二张图里的vref为什么往上走了?怪了怪了。

这篇的内容先到这里,vref的问题我们留到下一篇再讲吧?^_^

审核编辑:汤梓红

-

adc

+关注

关注

98文章

6501浏览量

544741 -

Doubler

+关注

关注

0文章

7浏览量

7197 -

DEBUG

+关注

关注

3文章

94浏览量

19928

原文标题:一个传统double tail comparator的debug过程分享(一)

文章出处:【微信号:analogIC_gossip,微信公众号:通向模拟集成电路设计师之路】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

tail实时滚动显示log文件内容

Implementing Double Data Rate

Dual Comparator Forms Temperat

Comparator/DAC Combinations So

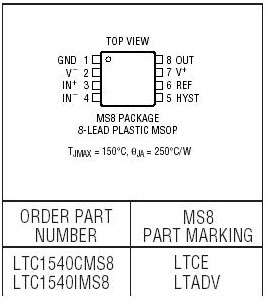

LTC1540-Nanopower Comparator w

Linux中tail与cat的区别

Comparator动态噪声的仿真

结合搜索与Double DQN的非完备信息博弈算法

HT8 MCU Comparator应用须知

double tail comparator的debug过程(一)

double tail comparator的debug过程(一)

评论