存储供应商正在竞相为 3D NAND 添加更多层,这是一个由数据爆炸和对更高容量固态驱动器和更快访问时间的需求驱动的竞争市场。

美光已经在完成 232 层 NAND 的订单,而且不甘示弱,SK 海力士宣布将于明年上半年开始量产 238 层 512Gb 三层单元 (TLC) 4D NAND。或许更重要的是,芯片制造商私下表示,他们将利用行业学习为目前正在开发的 3D-IC 堆叠 NAND。

西门子 EDA技术产品经理 Ben Whitehead 表示:“处理器的摩尔定律在过去几年中一直滞后,但对于 NAND 闪存来说仍然存在并且很好。”“这是一件好事,因为现代计算和网络对快速存储有着无法满足的需求。”

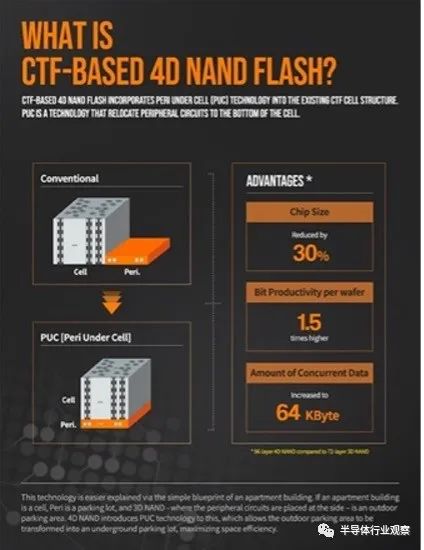

SK 海力士于 2018 年推出了 96 层 NAND 的 4D 命名法。尽管有这个名字,但该公司并未在四维空间中创建其产品或模仿 tesseract 立方体。但这个词也不完全是营销噱头。它是 3D 架构变体的商品名。

“对于 DRAM,大约需要 10 或 15 年的研发才能取得成果,但对于 3D NAND,发展速度非常快。当你想到通常的开发速度时,你会感到惊讶,” Synopsys研发总监Xi-Wei Lin说。“除了技术本身,它还是一款杀手级应用。苹果是第一个放入闪存来存储数据的。今天,我们买 iPhone 还是看内存有多少,而且都是闪存。从那里开始,大数据、人工智能和分析需要高性能计算。闪存正在填补硬盘驱动器和 RAM 内存之间的这一关键延迟差距。由于功耗、外形尺寸和密度成本,您可以看到应用程序,尤其是在数据中心、分析和游戏领域。”

演变与革命

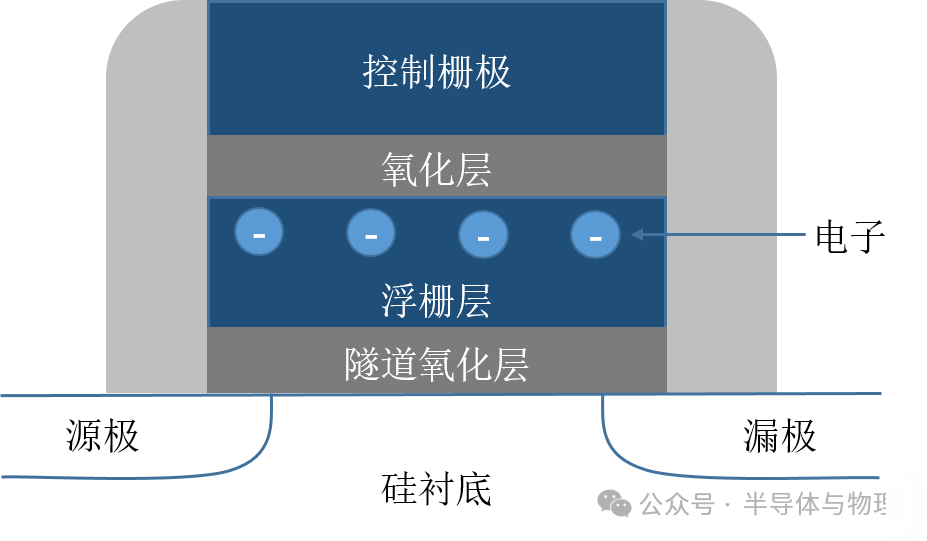

回顾 2D NAND,它具有平面架构,浮栅 (FG) 和外围电路彼此相邻。2007 年,随着 2D NAND 达到其规模极限,东芝提出了 3D NAND 结构。

三星在 2013 年率先推出了其所谓的“V-NAND”。

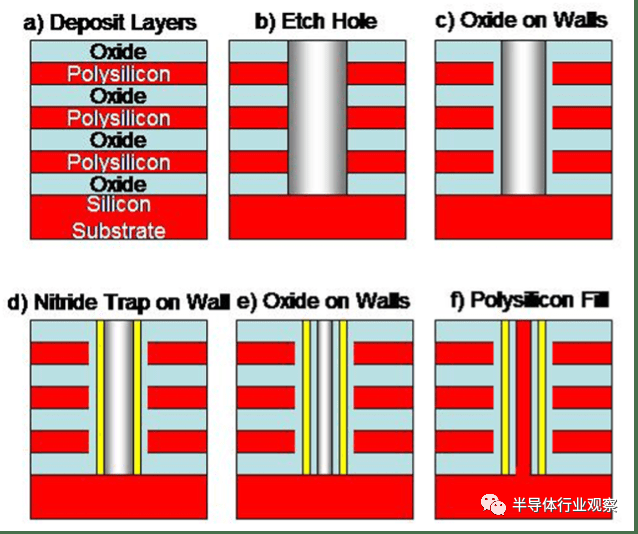

3D 设计引入了多晶硅和二氧化硅的交替层,并将浮栅交换为电荷陷阱闪存 (CTF)。区别既有技术上的,也有经济上的。FG 将存储器存储在导电层中,而 CTF 将电荷“捕获”在电介质层中。由于制造成本降低,CTF 设计很快成为首选,但肯定不是唯一的。

IBM 研究员 Roman Pletka 指出:“尽管所有制造商都转向电荷陷阱单元架构,但我预计传统浮栅单元在未来仍将发挥不可忽视的作用,尤其是对于容量或保留敏感的用例。”

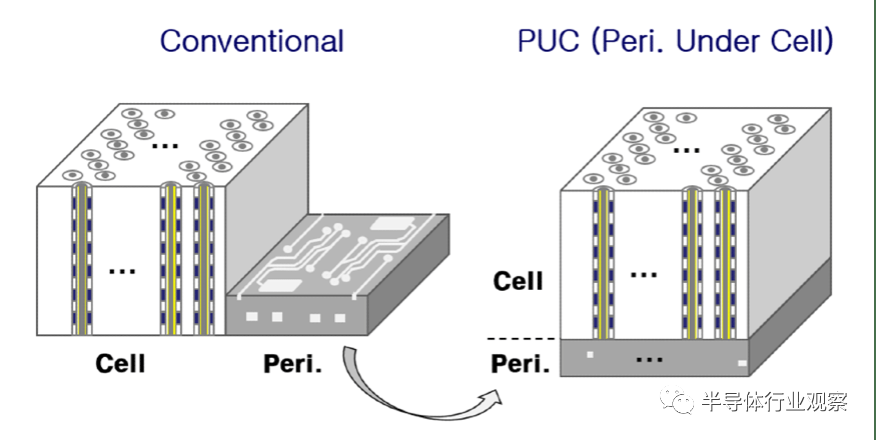

尽管如此,海力士表示,尽管创新了摩天大楼般的堆叠,但第一代 3D NAND 设计将外围电路保留在一边。

最终,3D NAND 供应商将外围电路移至 CTF 之下。在 SK Hynix 的术语中,它现在是 Periphery Under Cell (PUC) 层。一方面,说“4D NAND”比 CTF/PUC NAND 更短更酷。另一方面,最终这是 3D NAND 的另一种变体,每单位的单元面积更小。用于更小尺寸的类似设计有不同的商品名称,例如 Micron 的 CMOS under Array (CuA)。

图 1:SK 海力士对 4D NAND 的解释。

资料来源:SK 海力士全球新闻编辑室。

图 2:外围电路是 4D NAND 的底层。

资料来源:SK 海力士全球新闻编辑室。

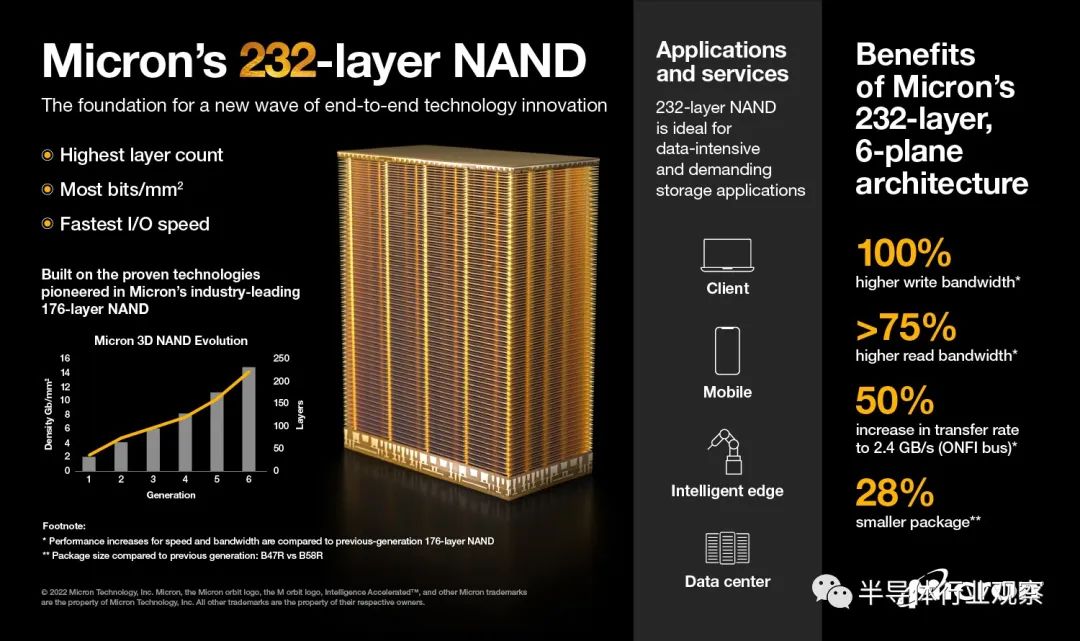

美光本身在 2022 年 7 月下旬宣布推出 232 层 NAND,该产品正在生产中。根据该公司的新闻稿,美光表示,其 232 层 NAND 是存储创新的分水岭,首次证明了在生产中将 3D NAND 扩展到 200 层以上的能力。

“添加这些层的主要作用是增加容量,因为每个人都在寻找更多的 SSD 容量,” Cadence产品营销集团总监 Marc Greenberg 说。“因此,添加更多层基本上意味着您可以在单一封装中存储更多千兆字节,并在单一类型的多层 3D NAND 组件上进行存储。这是一种能力游戏,添加所有这些层和其背后的技术。”

美光还声称拥有业界最快的 NAND I/O 速度 — 2.4 Gbps — 与上一代产品相比,写入带宽提高了 100%,每个芯片的读取带宽提高了 75% 以上。此外,232 层 NAND 包含六平面 TLC 生产 NAND,美光表示这是所有 TLC 闪存中每个裸片最多的平面,并且能够在每个平面上独立读取能力。

据行业分析师称,这可能是该公告中最令人印象深刻的部分。由于有六个平面,这个芯片可以表现得好像它是六个不同的芯片。

图 3:美光的 232 层 NAND。

来源:美光

中国的长江存储技术有限公司(YMTC)也宣布推出一款 232 层 3D NAND 模块。何时进入量产尚不清楚。

制造:优势与挑战

在去年的 IEEE IEDM 论坛上,三星的 Kinam Kim 发表了一个主题演讲,他预测到 2030 年将有 1,000 层闪存。这听起来可能令人头晕目眩,但这并不完全是科幻小说。“与 NAND 闪存的历史趋势线相比,这已经放缓了,”Imec 存储存储器项目总监 Maarten Rosmeulen 说。“如果你看看其他公司,比如美光或西部数据,他们在公开声明中提出的内容,他们甚至比这还要慢。不同的制造商之间也存在一些差异——似乎他们正在延长路线图,让它放慢速度。我们相信这是因为保持空间运转需要非常高的投资。”

尽管如此,竞争风险仍然足够高,以至于这些投资是不可避免的。“主要的前进方向,主要的乘数,是向堆栈添加更多的层,”Rosmeulen 说。“进行 XY 缩小和缩小内存孔的空间非常小。这很难做到。也许他们会在这里或那里挤压几个百分点,把孔放在一起,孔之间的缝隙更少,诸如此类。但这并不是最大的收获。如果你能继续堆叠更多的层,密度只能以目前的速度显着提高。”

图 4:NAND 制造中的 3D 步骤。

资料来源:客观分析

进一步堆叠似乎是合理的,除了整个过程的核心不可避免的问题。

“主要挑战在于蚀刻,因为您必须蚀刻具有非常高纵横比的非常深的孔,”Rosmeulen 说。“如果你看看上一代有 128 层,这是一个大约 6、7 或 8 微米深的孔,只有大约 120 纳米直径,极高的纵横比——或者可能更高一点,但不是那么很多。蚀刻技术有进步,可以一次性蚀刻更深的孔,但不会更快。您无法提高蚀刻速度。因此,如果工艺流程以沉积和蚀刻为主,而这些工艺步骤并没有提高成本效率,那么添加更多层就不再像降低成本那样有效。”

蚀刻也只是多个步骤之一。“除了蚀刻之外,您还需要用非常薄的介电层上下均匀地填充这个孔,”Synopsys 的 Lin 说。“通常情况下,由于晶圆的化学性质,沉积几纳米的层并不容易。在这里,他们必须一路向下才能填满。有亚原子层沉积方法,但它仍然具有挑战性。另一个大挑战是压力。如果你建立了如此多的层,这些层会经历一些蚀刻/沉积/清洁/热循环,这可能会导致局部和全局压力。在本地,因为在你钻孔后,你需要在整个堆栈中切出一个非常深的沟槽。它变成了一个非常高的摩天大楼,摇摇欲坠。如果你开始经历一些洗涤或其他过程,很多事情都可能导致两座摩天大楼相互倒塌。那么你就失去了收益。而且通过将如此多的材料放在一起,切割不同的图案,这会产生全局应力,并导致晶圆翘曲,这将导致晶圆厂无法处理,因为晶圆必须是平的。

这只是开始。请记住,蚀刻正在穿过不同材料的层。”

Objective Analysis 的 Handy 表示,三星的解决方案是创建极薄的层。“这对整个行业很有用,因为每个人都使用几乎相同的工具来创造这些东西。”

让它更好地工作

闪存的基本概念也存在固有的功能挑战。“人们越来越依赖需要越来越强大的纠错算法来与这些设备一起工作,”Cadence 的 Greenberg 说。

问题是 NAND 闪存设备内置的智能并不多。“通常情况下,SSD 发生在控制器端,”Greenberg 解释说。“控制器正在向 NAND 闪存设备发送命令,NAND 闪存设备会做出响应,但它并没有太多的智能。它只是响应请求,例如针对特定地址的数据块。NAND 闪存设备将简单地响应该数据块。但是在控制器端,你必须首先对接收到的数据进行纠错,然后确定该块中是否存在不可接受的错误数量,然后决定如何重新映射该块地址空间并在其位置放置一个不同的块。所有这些决定都发生在控制器端。”

尽管如此,由纳米级摩天大楼建造的世界重新强调了 ONFI 控制器和 ONFI PHYS 等组件,并为设计人员提出了新的挑战。

“内存工厂可以生产的层数使与这些内存接口的控制器的设计验证问题变得非常复杂——而且它们可能并不那么明显。SSD 控制器必须处理更多的内存通道。将许多pipeline与越来越快(但永远不够快)的主机接口连接起来会在非常意想不到的地方产生瓶颈,”西门子的 Whitehead 说。“另一个设计验证挑战是功率。长期以来,大多数存储控制器的优先级较低,但现在已转变为关键功能。移动到较小的节点会有所帮助,但代价高昂。商业模式不能容忍重新旋转,更不用说供应链难以排长队了。上市时间的延迟让高层管理人员非常清楚。存储的增长动力甚至更多,这需要我们重新思考如何验证设计。AI 加速器需要更大的存储控制器,这可能会很快消耗您的仿真和原型设计能力。边缘智能需要数量级更复杂的设计验证。内存计算,如 CSD,需要测试新的处理器组合,将 RTOS 和 HTOS 与以前看不见的工作负载混合在一起。”

这是人们如此关注验证 IP 的原因之一。

Siemens Digital Industries Software 的 ICVS 产品经理 Joe Hupcey 表示:“使用此 IP 的自动化可以快速生成测试平台,让设计和验证团队在几分钟内启动并运行。”“这种生产力水平使我们能够对整个设计进行架构探索,从而尽早对所选择的权衡取舍充满信心。同时,它还建立了自动跟踪指标的框架——如代码、功能和场景覆盖率——使团队能够衡量他们的进度并拥有做出签核决定所需的数据。最后,基于我们在 CXL/PCIe 协议方面的专业知识,我们看到通用 Chiplet Interconnect Express (UCIe) 等新兴标准在使团队能够协作以快速设计和验证这些大规模可扩展内存模块方面发挥着关键作用。”

此外,Imec 正在探索 3D NAND 的潜在新结构。它展示了所谓的“沟槽架构”,这是一种设计变体,其中存储单元是沟槽侧壁的一部分,两个晶体管位于沟槽的相对两端。Imec 铁电体项目总监 Jan Van Houdt 解释了它的价值:“与目前使用的环栅(或圆柱形)架构相比,3D 沟槽架构具有双倍密度的潜力。”

然而,他接着指出了一些缺点。“有两个高纵横比(=具有挑战性的)蚀刻步骤而不是一个,以及在闪光情况下隧道氧化物中的电场较低。第二个缺点在使用铁电 FET 时不存在,这使得沟槽版本对铁比对闪存更有吸引力。”该设计仍处于原型阶段。

结论

2016 年,专家指出,由于技术问题,3D NAND 可能会在 300 层或接近 300 层时失去动力。这似乎已被今天的谨慎乐观所取代。

“[在 SK Hynix 的 238 层之后] 我预计层数在未来几年会以大致相同的速度增加,”IBM 的 Pletka 说。“然而,从技术角度来看,由于高纵横比蚀刻工艺,增加层数受到挑战,而且资本支出也受到挑战,因为制造芯片的时间随着层数的增加而增加。这就是为什么我们将通过制作更薄的层、横向缩放(例如更密集地放置垂直孔)以及使用更高效的布局(例如共享位线和逻辑缩放)来看到新的缩放方向(例如,使用拆分门架构或存储更多每个单元的位数)。有了这些技术,预计 NAND 闪存的存储密度至少在未来 5 到 10 年内会以类似的速度增长。”

其他人同意。“当人们说我们不能超过这个层数时,没有物理限制,”Objective Analysis 的首席分析师 Jim Handy 说。“在半导体领域,总是有人说我们做不到。我们不能在 20 纳米以下进行光刻。现在,他们正在研究 1 纳米。三星谈到了 1,000 层。可能在 20 年后我们会笑,我们曾经认为这很多。”

审核编辑 :李倩

-

存储器

+关注

关注

38文章

7534浏览量

164489 -

堆叠

+关注

关注

0文章

35浏览量

16656 -

3d nand

+关注

关注

4文章

93浏览量

29179

原文标题:3D NAND,层数堆叠会有极限吗?

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

预期提前,铠侠再次加速,3D NAND准备冲击1000层

TechWiz LCD 3D应用:局部液晶配向

自带尺寸标注的3D预览为制造商组件提供更强劲的客户体验

3D打印技术,推动手板打样从概念到成品的高效转化

3D NAND的发展方向是500到1000层

铠侠瞄准2027年:挑战1000层堆叠的3D NAND闪存新高度

一PCB相关企业成为英特尔指定的设备供应商

铠侠计划2030-2031年推出千层级3D NAND闪存,并开发存储级内存(SCM)

3D打印连接器正在兴起

存储供应商正在竞相为 3D NAND 添加更多层

存储供应商正在竞相为 3D NAND 添加更多层

评论