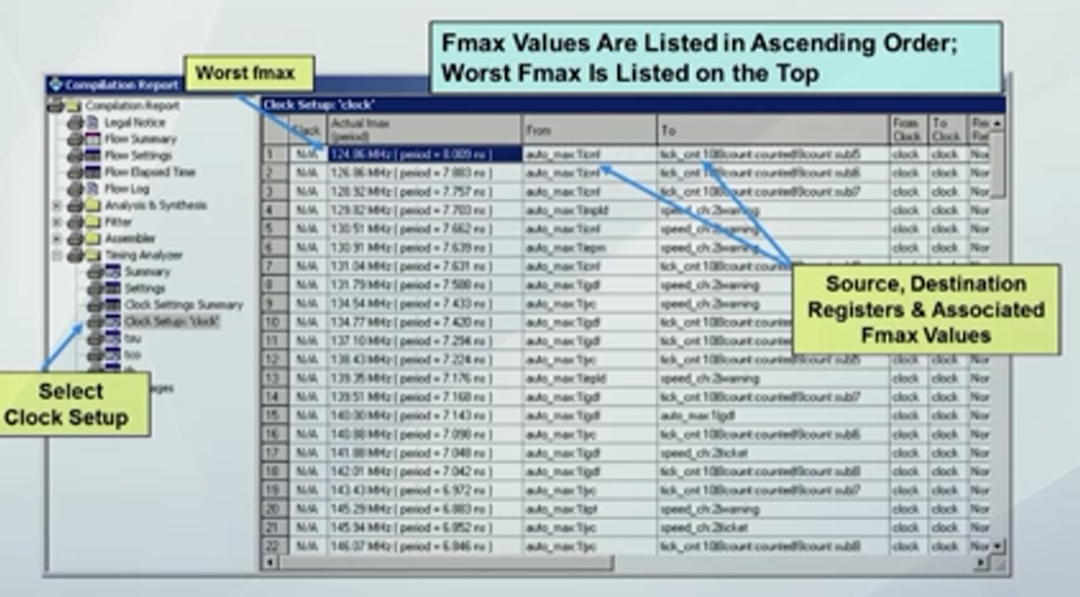

图一是Quartus Ⅱ工具关于时序分析建立时间分析报告结果(个人理解:该报告可以作为时钟周期报告)。Quartus Ⅱ工具可以详细给出每一条路径的分析结果,路径信息按照延时由大到小的顺序排列,因为延时最长的情况通常被认定为最坏情况,所以需要关注延时长的情况。

图一的第一列展示的是延时的时间长度,最长的关键路径延时为8ns(1ns=10-9s),对该时间取倒数,可以得出芯片的工作频率在125MHz左右。

除此之外,图一还展示了延时路径的一些信息,包括源节点(可以理解为数据发送端)信息、目标节点(可以理解为数据接收端)信息等。目标节点从顶层到底层(含个人理解:门级信息,具体到某个节点的某个引脚)的信息均列出,设计人员可以通过以上信息分析出该路径在设计中的实际位置,方便对电路设计进行优化。

图一,图片来源:学堂在线《IC设计与方法》

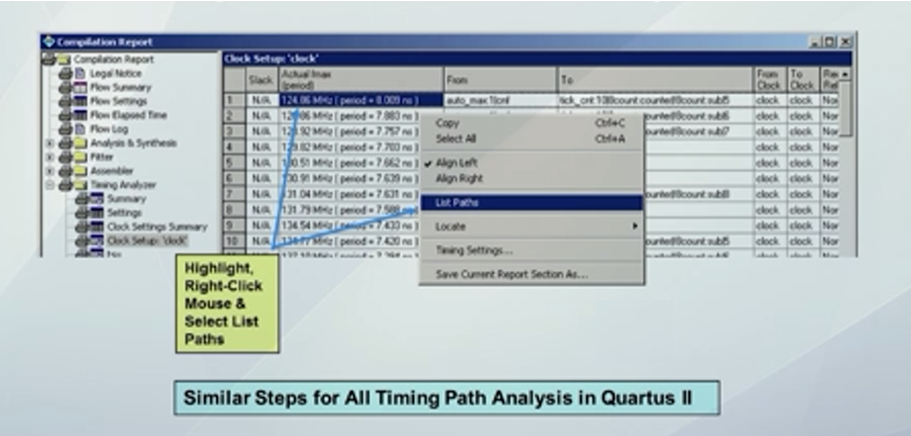

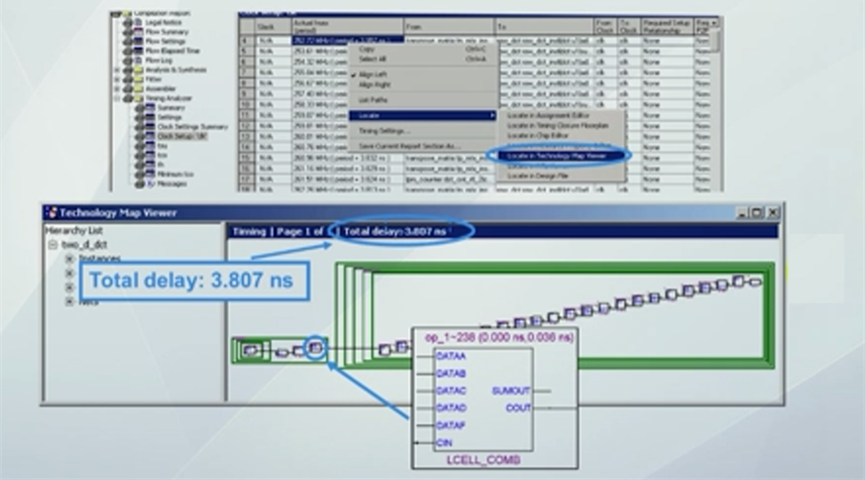

设计人员可以通过图二的操作列出某一路径的详细信息,图二的操作可以展示延时最长路径的详细信息。

图二,图片来源:学堂在线《IC设计与方法》

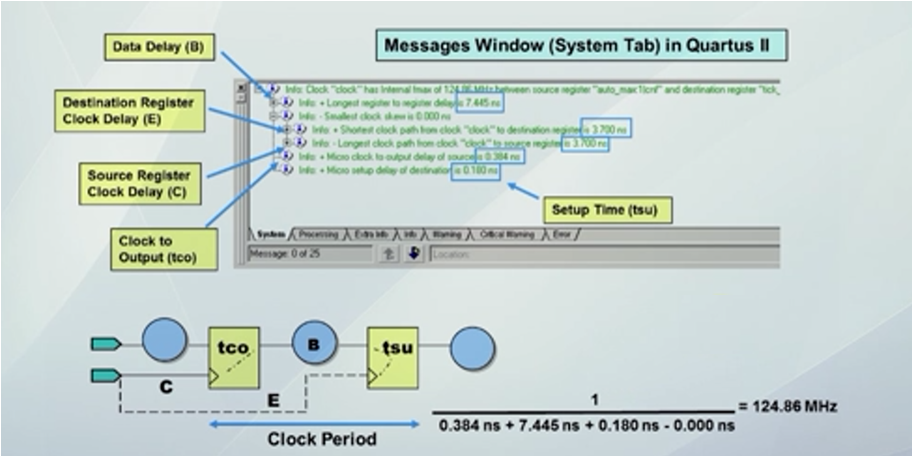

经过图二的操作,Quartus Ⅱ工具会显示出图三界面,图三列出了延时最长路径的详细信息。

图三左下角是时序分析的模型图,设计人员可以对照模型图在图三界面中找到C(时钟信号传递到源触发器的延时)、E(时钟信号传递到目标触发器的延时)、B(从源触发器到目标触发器所经过的组合逻辑电路的延时)、tco(源触发器延时)、tsu的信息(目标触发器延时)。

图三界面中,一共有七行信息。第二行列出了最长的B的延时为7.445ns。第四行列出了最短的E的延时为3.7ns,第五行列出了最长的C的延时为3.7ns,可以发现C=E,这是因为该芯片面积较小,所以C和E相等。第六行列出了tco为0.384ns,第七行列出tsu为0.18ns。

根据时钟周期的公式:

time period=tco+B+tsu-(E-C)

可以计算得出time period(时钟周期)等于8.009ns。工作频率为timeperiod的倒数,其值约为124.86MHz。

图三,图片来源:学堂在线《IC设计与方法》

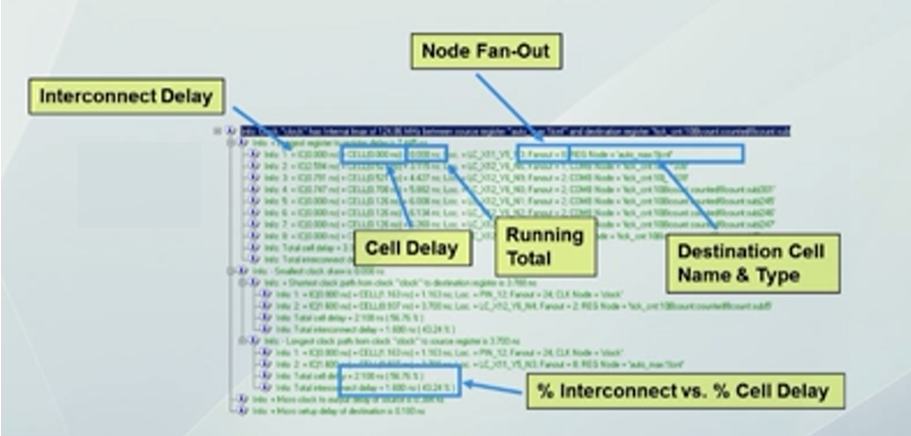

Quartus Ⅱ工具可以将图三中更详细的信息展示,如图四上侧,列出B路径的详细信息。图四上侧展示了互连线延时和单元(个人理解:一个门器件)的延时、元器件的扇出系数(扇出系数越大,延时越大)、节点相关信息。

图四下侧展示了总结性的报告,包括总互连线延时、总的单元延时、以及两种延时所占的比例。设计人员可以通过两种延时的比例判断延时过长的原因是因为互连线过长,还是因为逻辑过复杂。

图四,图片来源:学堂在线《IC设计与方法》

图五下侧的窗口展示了使用Technology Viewer(Quartus Ⅱ工具中一种运用图形展示分析结果的方式)展示最长延时路径。如图五所示,输入D触发器经过十几个单元达到输出D触发器,说明最长延时路径延时过长的原因是电路逻辑过复杂。

设计人员也可以通过Technology Viewer观测某个元器件所使用的信号、元器件的类型、元器件的延时。

图五,图片来源:学堂在线《IC设计与方法》

审核编辑:刘清

-

IC设计

+关注

关注

38文章

1297浏览量

104009 -

时钟

+关注

关注

11文章

1734浏览量

131528 -

触发器

+关注

关注

14文章

2000浏览量

61182 -

时序分析

+关注

关注

2文章

127浏览量

22569

原文标题:芯片设计相关介绍(32)——Quarus Ⅱ工具时序分析结果

文章出处:【微信号:行业学习与研究,微信公众号:行业学习与研究】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

车载总线监控分析及仿真工具 - VBA

锁存器的基本输出时序

时序逻辑电路故障分析

电源时序器的电压显示功能

数据分析的工具有哪些

matlab神经网络工具箱结果分析

FPGA 高级设计:时序分析和收敛

影响气密性测试结果的原因分析及解决方案分享

QuarusⅡ工具时序分析结果

QuarusⅡ工具时序分析结果

评论