DDR3 地址线

DDR3为减少地址线,把地址线分为行地址线和列地址线,在硬件上是同一组地址线;地址线和列地址线是分时复用的,即地址要分两次送出,先送出行地址,再送出列地址。

一般来说列地址线是10位,及A0...A9;行地址线数量根据内存大小,BANK数目,数据线位宽等决定(感觉也应该是行地址决定其他) ;

BANK

bank是存储库的意思,也就是说,一块内存内部划分出了多个存储库,访问的时候指定存储库编号,就可以访问指定的存储库,内存中划分了多少个bank,要看地址线中有几位BA地址,如果有两位,说明有4个bank,如果有3位,说明有8个bank

DDR3 容量计算

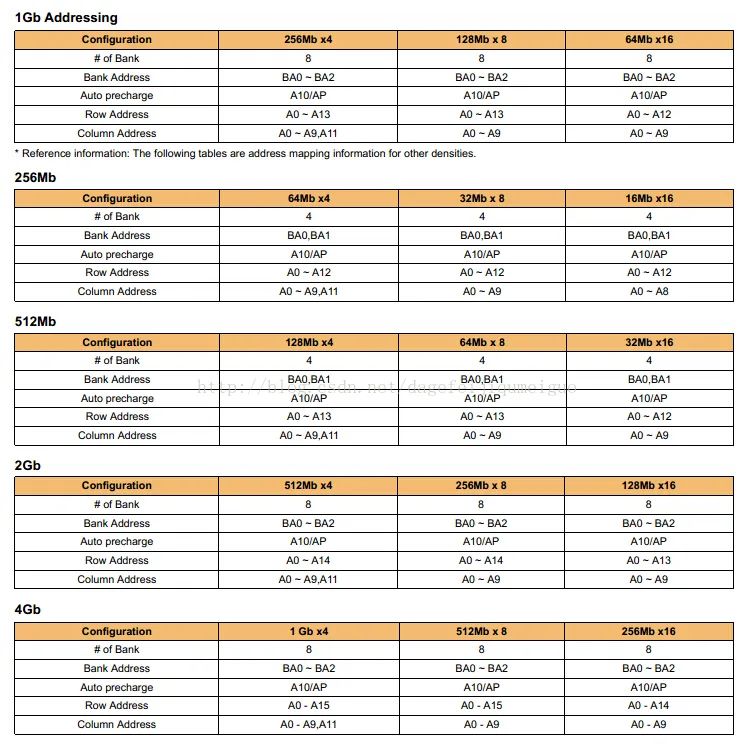

下面这张图是芯片k4t1g164qf资料中截取的;以1Gb容量的DDR2颗粒为例(其他的类似);假设数据线位宽为16位,则看64Mb x 16这一列:

bank地址线位宽为3,及bank数目为 2^3=8;

行地址线位宽位13,及A0...A12;

列地址线位宽为10,及A0...A9;

有 2^3 * 2^13 * 2^10 = 2^26 =2^6Mb = 64Mb

再加上数据线,则容量为 64Mb x 16

-

DDR3

+关注

关注

2文章

276浏览量

42323 -

存储

+关注

关注

13文章

4332浏览量

85958 -

容量计算

+关注

关注

0文章

6浏览量

6793

原文标题:DDR3地址和容量计算、Bank理解

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DDR3、DDR4、DDR5的性能对比

如何选择DDR内存条 DDR3与DDR4内存区别

DDR4的主要参数

基于FPGA的DDR3多端口读写存储管理设计

华邦倾力挺进DDR3市场,抓住转单商机

赋能产业互联网,高通量计算让世界更高效!

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据表

完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

关于DDR3地址的容量计算

关于DDR3地址的容量计算

评论