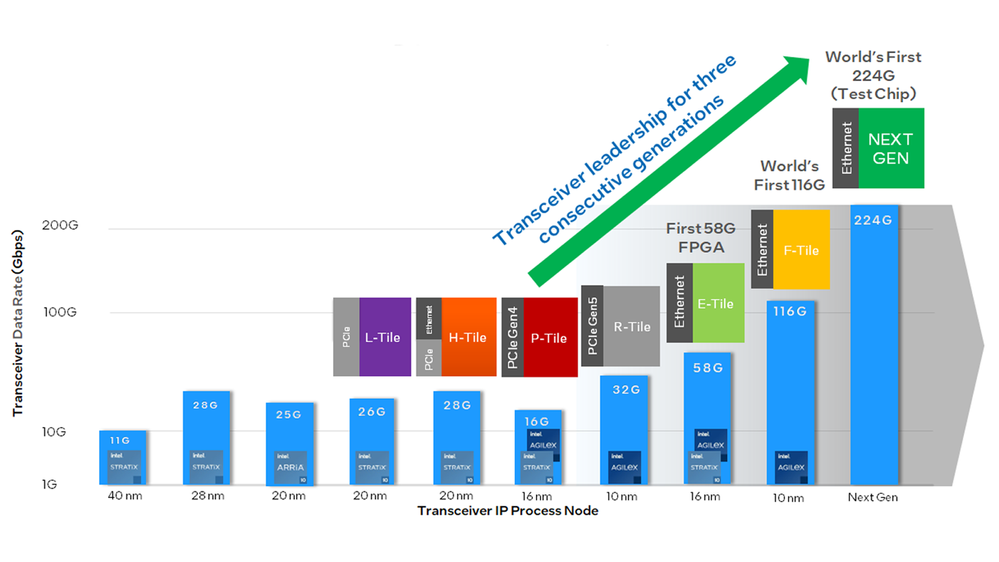

高速串行收发器在 20 多年前出现时便迅速成为一种基础 FPGA 组件。随着带宽的爆发式增长,它们变得越来越重要。这些高速收发器设计足够灵活、可配置性强,能够直接实现多种标准数字串行通信协议,包括以太网、PCI Express (PCIe)、Compute Express Link (CXL)、串行数字接口 (SDI) 等。长期以来,英特尔在高速串行收发器的开发方面一直保持其先进性 (如图 1 所示)。

图1:英特尔 FPGA 收发器技术保持先进性

图 1 显示,由于采用了十分先进的英特尔 FPGA 制程工艺,高速收发器数据速率已从 40 nm 制程节点的 10 Gbps 提升到了 116 Gbps;同时,英特尔已展示了一款 224 Gbps 高速收发器测试芯片,这预示着 FPGA 收发器技术的发展方向。

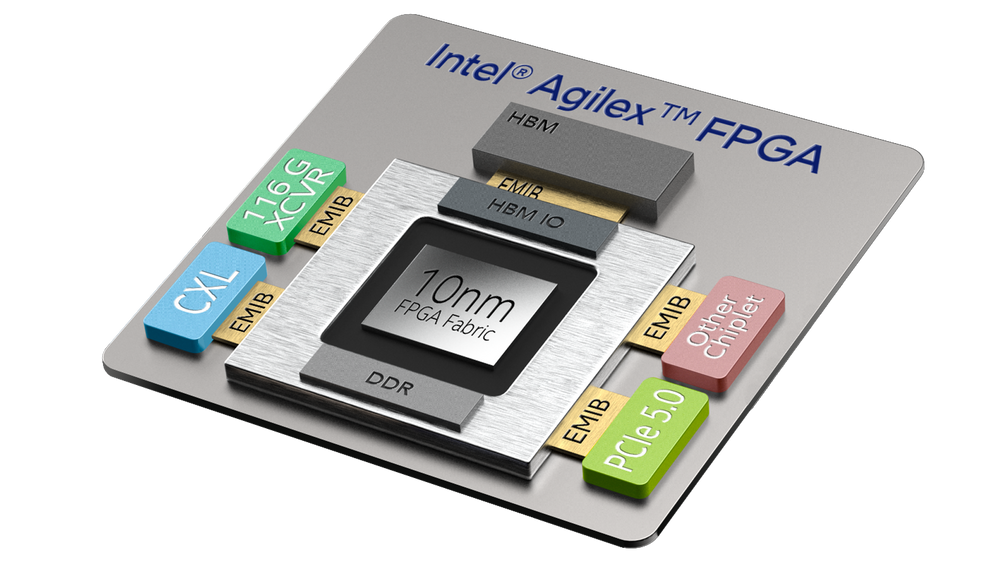

新近英特尔 FPGA 家族,包括英特尔 Agilex FPGA、英特尔 Stratix 10 FPGA 和 SoC FPGA 在内,都集成了单独的、英特尔称之为“Tile”的小芯片,用来实现高速收发器。这种基于 Tile 的 FPGA 构建方法为快速且经济高效地开发具有许多功能的广泛器件系列提供了极大的灵活性。

图 2 显示的是英特尔 Agilex FPGA 的内部结构。图中五个小芯片围绕着一个中央半导体芯片,芯片内含英特尔 Agilex FPGA 的可编程逻辑结构及其他逻辑电路,包括 DDR 和高带宽内存 (HBM) 控制器。五个小芯片中有四个标记了“116G XCVR”、“CXL”、“PCIe 5.0”和“Other Chiplet”字样,第五个标记为“HBM”的小芯片实际上是一个包含了数 GB HBM DRAM 的小芯片堆栈。

图 2:英特尔 Agilex FPGA

尽管根据高速串行协议标记了不同的名称,但“116G XCVR”、“CXL”和“PCIe 5.0”的要表达的意思相似。英特尔开发了这些小芯片,以提供高速串行收发器功能。每个 F-tile 收发器小芯片为 FPGA 增加了 20 条高速收发器通道。在每个 F-tile 上的 20 个高速收发器中,有四个 FHT 收发器 (每个收发器都能够使用 PAM4 调制技术以快达 116 Gbps 的速度运行),有 12 个 FGT 收发器 (每个收发器都能够使用 PAM4 调制技术以 58.125 Gbps的速度运行)。总的来说,这 20 个高速收发器可提供超过 700 Gbps 的数据带宽。对于最多有四个 F-tile 的英特尔 Agilex I 系列和 M 系列 FPGA,高速串行总带宽超过了 2.4 Tbps。

英特尔刚刚发布了一个 5 分钟的视频,展示了英特尔 Agilex FPGA 家族的高速数据传输功能,这些功能由 F-tile 的高速收发器提供支持。演示中使用的是英特尔 SuperLite IV IP,一种低开销的串行流协议。SuperLite IV IP 利用了 F-tile 的 PHY 直连功能,该功能具有 PMA 直连模式,可绕过 F-tile 媒体访问控制 (MAC) 和物理编码子层 (PCS) 硬核 IP 模块。在高速收发器中绕过这些元件可大大降低时延,因而使 SuperLite IV 协议成为芯片到芯片、板对板和背板应用的理想选择。

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

收发器

+关注

关注

10文章

3424浏览量

105960 -

英特尔

+关注

关注

61文章

9949浏览量

171692 -

通信协议

+关注

关注

28文章

879浏览量

40297

原文标题:解析丨传输速率可达 2.4 Tbps!英特尔® Agilex™ FPGA 支持高效数据传输

文章出处:【微信号:英特尔FPGA,微信公众号:英特尔FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英特尔展示互连微缩技术突破性进展

英特尔推出全新英特尔锐炫B系列显卡

英特尔是如何实现玻璃基板的?

英特尔携手日企加码先进封装技术

英特尔CEO:AI时代英特尔动力不减

英特尔加大玻璃基板技术布局力度

BittWare提供基于英特尔Agilex™ 7 FPGA最新加速板

英特尔旗下FPGA公司Altera正式亮相

英特尔成立全新独立运营的FPGA公司Altera

新思科技与英特尔深化合作加速先进芯片设计

英特尔旗下Altera正式独立运作,FPGA市场将迎来怎样的巨变?

英特尔FPGA收发器技术保持先进性

英特尔FPGA收发器技术保持先进性

评论