取某个信号的上升沿或下降沿信号

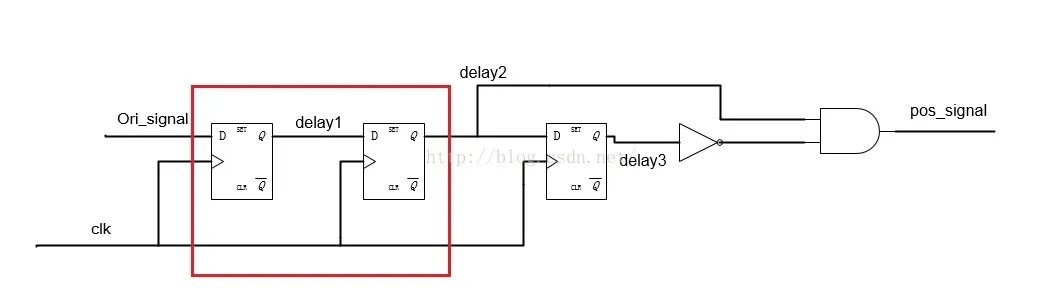

取一个信号的上升沿或下降沿信号,可以通过将信号delay后,然后将原信号和delay信号,通过不同的与非操作,获取上升沿信号或下降沿信号: 阶段一: reg delay; // delay信号 always @ ( posedge clk or negedge rstn ) if( !rstn ) delay <= 0; else delay <= orig; // orig是原信号 wire pos_signal = orig && ( ~delay ); // 原信号上升沿位置处产生的pulse信号 wire neg_signal = ( ~orig ) && delay; // 原信号下降沿位置处产生的pulse信号 阶段二: 上述操作会存在亚稳态问题,并且得到的上升沿信号pos_signal和下降沿信号neg_signal无法被原采样时钟clk采样。正确做法是,先将原信号用采样时钟delay 2次(打两拍),得到和采样时钟同时钟域的信号delay2,然后再按上述方法获取上升沿和下降沿信号,这时得到的上升沿或下降沿就可以被原采样时钟采样。 例句如下: reg ori_signal;// 需取上升沿或下降沿的原信号 reg delay1; reg delay2; always @ ( posedge clk or negedge rstn ) if( !rstn ) delay1 <= 0; else delay1 <= ori_signal; always @ ( posedge clk or negedge rstn ) if( !rstn ) delay2 <= 0; else delay2 <= delay1; // delay2 已与clk同域 reg delay3; always @ ( posedge clk or negedge rstn ) if( !rstn ) delay3 <= 0; else delay3 <= delay2; wire pos_signal = delay2 && ( ~delay3 ); // 原信号上升沿位置处产生的pulse信号 wire neg_signal = ( ~delay2 ) && delay3; // 原信号下降沿位置处产生的pulse信号 上升沿电路如下: 注意:前两个触发器的运用就是起同步作用,将某个信号同步到采样时钟域,以后要重点注意使用。

阶段三:

用阶段二的语句会比较繁琐,可以用下述语句简化:

reg[2:0] delay;

always @ ( posedge clk or negedge rstn )

if( !rstn )

delay <= 0;

else

delay <= { delay[1:0], ori_signal} ; // ori_signal是原信号

wire pos_signal = delay[1] && ( ~delay[2] ); // 原信号上升沿位置处产生的pulse信号

wire neg_signal = ( ~delay[1] ) && delay[2]; // 原信号下降沿位置处产生的pulse信号

注意:前两个触发器的运用就是起同步作用,将某个信号同步到采样时钟域,以后要重点注意使用。

阶段三:

用阶段二的语句会比较繁琐,可以用下述语句简化:

reg[2:0] delay;

always @ ( posedge clk or negedge rstn )

if( !rstn )

delay <= 0;

else

delay <= { delay[1:0], ori_signal} ; // ori_signal是原信号

wire pos_signal = delay[1] && ( ~delay[2] ); // 原信号上升沿位置处产生的pulse信号

wire neg_signal = ( ~delay[1] ) && delay[2]; // 原信号下降沿位置处产生的pulse信号

Verilog中clk为什么要用posedge,而不用negedge

posedge是上升沿,电平从低到高跳变

negedge是下降沿,电平从高到低跳变

对于典型的counter逻辑

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

counter <= 24'd0;//十进制0

else if(counter < led_time) begin

flag_counter = 1'b0;

counter <= counter + 1'b1;

end

else begin

counter <= 24'd0;

flag_counter = 1'b1;

end

end

clk为什么要用posedge,而不用negedge呢?

一般情况下,系统中统一用posedge,避免用negedge,降低设计的复杂度,可以减少出错。

在ModelSim仿真中,时钟是很严格的,但是在真实的晶振所产生的clock却是不严格的,比如高电平和低电平的时间跨度不一样,甚至非周期性的微小波动。如果只使用posedge,则整个系统的节拍都按照clock上升沿对齐,如果用到了negedge,则系统的节拍没有统一到一个点上。上升沿到上升沿肯定是一个时钟周期,但是上升沿到下降沿却很可能不是半个周期。这都会出现问题。

FPGA特有的东西:Global CLK。FPGA内部有专门的CLK“线”,和一般的逻辑门的走法不一样,目的是为了保证整个FPGA片内的时钟一致,这个东西就叫GlobalCLK

审核编辑 :李倩

-

Verilog

+关注

关注

28文章

1352浏览量

110513 -

触发器

+关注

关注

14文章

2019浏览量

61397 -

上升沿

+关注

关注

0文章

3浏览量

1803

原文标题:Verilog学习笔记

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Verilog中clk为什么要用posedge,而不用negedge

Verilog中clk为什么要用posedge,而不用negedge

评论