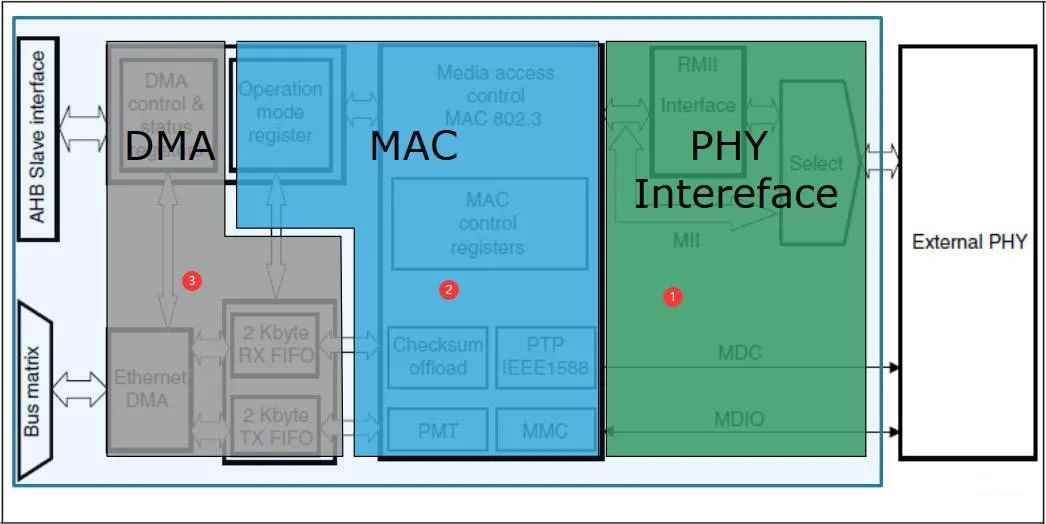

在之前的文章,我们讲解了STM32的网络外设部分。

文章有《STM32网络电路设计》《STM32网络之MAC控制器》《STM32网络之DMA控制器》《STM32网络之中断》。

STM32只有网络外设时不能进行网络通信的,因为STM32只提供了SMI接口,MII和RMII接口。我们还需要与之通信的外部网络芯片,简称PHY芯片。我熟悉的PHY型号有:RTL8201F,RTL8201E,RTL8201G,DP83848,YT8512C等,原计划讲解RTL8201F的,但是内容太多,先把PHY寄存器拿出来讲一下。

为什么STM32不集成PHY呢?

PHY(PortPhysical Layer),中文可称之为端口物理层。

1、PHY芯片是模拟芯片,需要将网线的差分信号转换成数字信号,如果集成,则芯片面积增加,如果要降低功耗,还要高的芯片制造工艺,这会直接将芯片成本拉高。

2、并不是所有的STM32使用者都需要使用到网络,集成PHY会增加成本。

所以,STM32不集成PHY不是技术问题,而是各方面考虑的结果。

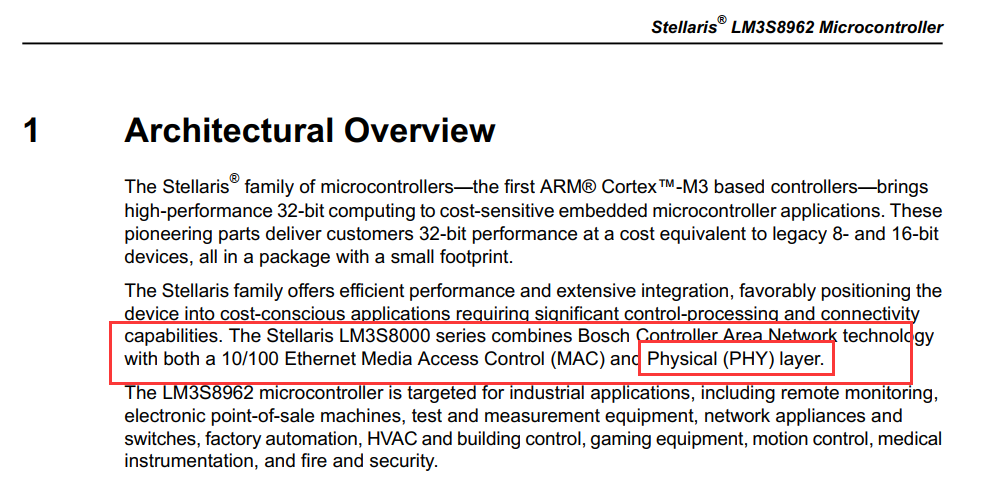

难道没有集成PHY的MCU吗?

有的,TI的LM3S8962。

我们说回PHY寄存器,外部PHY芯片寄存器分为3种类型

Basic:基础寄存器

Extended:扩展寄存器

Vendor-spcififc:厂商特殊寄存器

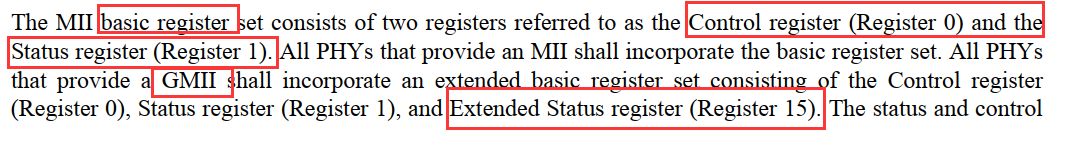

其中在802.3协议2012版中有如下说明。

不同的手册,对基础寄存器有不同的说明,按照802.3-2012上图的说明基础寄存器是控制器寄存器(寄存器0)和状态寄存器(寄存器1),在GMII(千兆网)接口中海油扩展状态寄存器(寄存器15)。

本文主要根据802.3-2012协议讲解PHY的基础寄存器,并不是根据某个具体芯片讲解的。

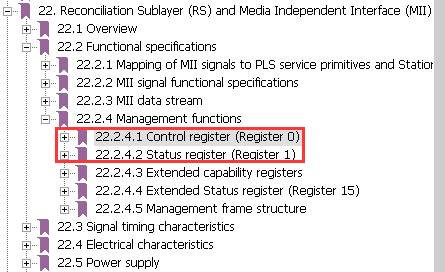

寄存器0和寄存器1在协议文档的中位置如下图

上面提到的802.3-2012协议大家可以到ieee官网下载

或者通过百度网盘下载

(提示:公众号不支持外链接,请复制链接到浏览器下载)

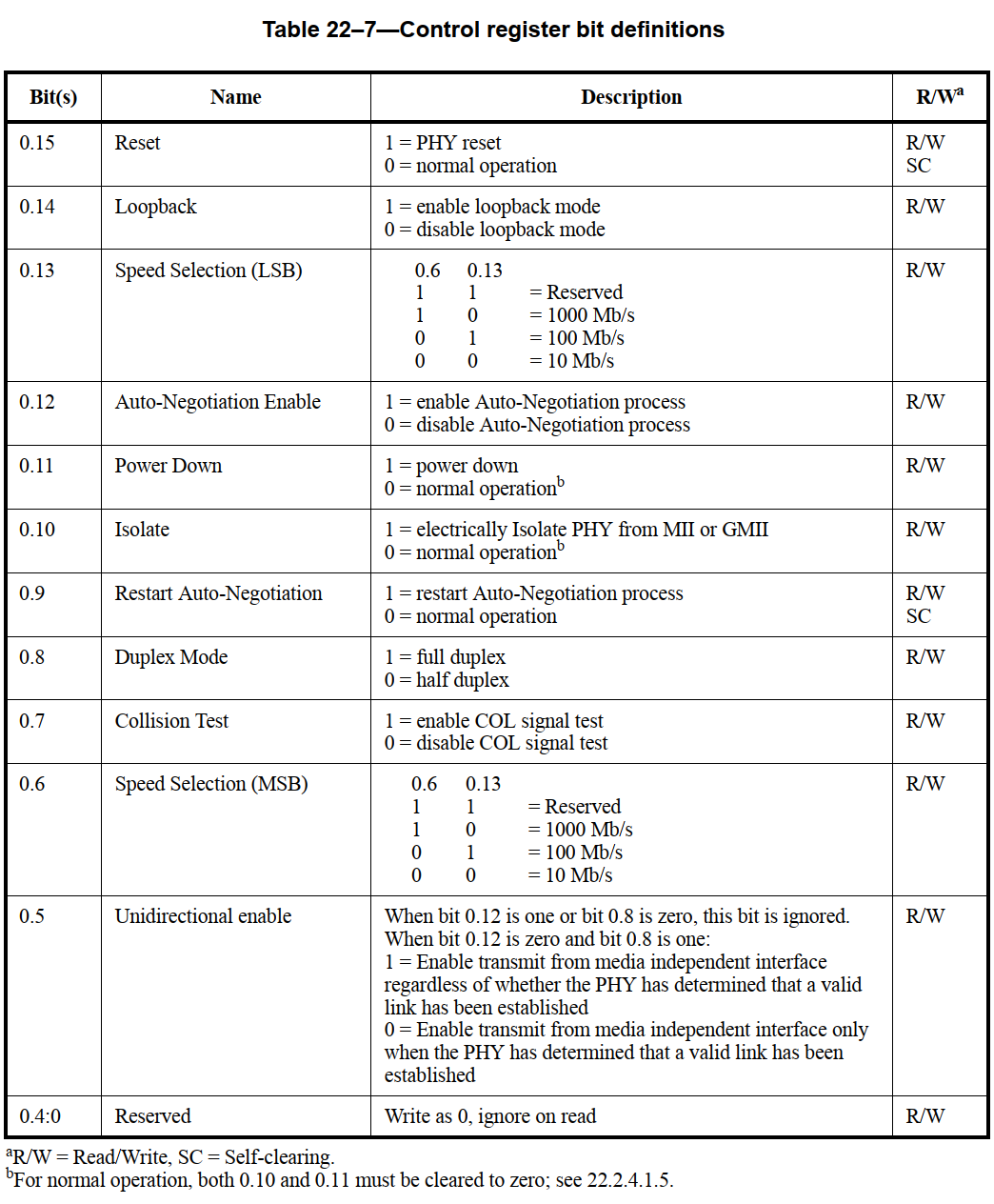

01 控制寄存器(寄存器0) 寄存器0是PHY控制寄存器,通过ControlRegister可以对PHY的主要工作状态进行设置

bit15 Rset

bit15为1时表示,PHY复位。Bit15控制的是PHY复位功能,在该位置写入1实现对PHY的复位操作。复位后该端口PHY的其他控制、状态寄存器将恢复到默认值,每次PHY复位应该在0.5s的时间内完成,复位过程中Bit15保持为1,复位完成之后该位应该自动清零。一般要改变端口的工作模式(如速率、双工、流控或协商信息等)时,在设置完相应位置的寄存器之后,需要通过Reset位复位PHY来使配置生效。

在复位过程完成之前,不需要PHY接受对控制寄存器的写事务,而在复位过程完成之前,对控制寄存器中除bit15以外的位的写操作可能无效。

bit14 Loopback

Loopback是一个调试以及故障诊断中常用的功能,Bit14置1之后,PHY和外部MDI的连接在逻辑上将被断开,从MAC经过MII/GMII(也可能是其他的MAC/PHY接口)发送过来的数据将不会被发送到MDI上,而是在PHY内部(一般在PCS)回环到本端口的MII/GMII接收通道上。

通过Loopback功能可以检查MII/GMII以及PHY接口部分是否工作正常,对于端口不通的情况可用于故障定位。需要注意的是,很多时候PHY设置Loopback后端口可能就Linkdown了,MAC无法向该端口发帧,这时就需要通过设置端口ForceLink up才能使用Loopback功能。

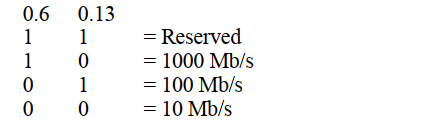

bit13 Speed Selection(LSB)

Bit13和Bit6两位联合实现对端口的速率控制功能,具体的对应关系详见下图

需要注意的是SpeedSelection只有在自动协商关闭的情况下才起作用,如果自动协商设置为Enable状态,则该设置不起作用;

并且,对SpeedSelection的修改设置,往往需要复位端口才能配置生效。因此在设置该位置的时候需要检查自动协商的设置并通过Bit15复位端口。

bit12 Auto-Negotiation Enable

自动协商(AN)开关。设置为1表示打开AN功能,端口的工作模式通过和连接对端进行自动协商来确定。如果设置为0则自动协商功能关闭,端口的工作模式通过ControlRegister相应位置的配置决定。必须注意的是,对于1000BASE-T接口,自动协商必须打开。

bit11 Power Down

端口工作开关:设置为1将使端口进入PowerDown(低功耗状态)模式,正常情况下PHY在PowerDown模式其MII和MDI均不会对外发送数据。PowerDown模式一般在软件shutdown端口的时候使用,需要注意的是端口从PowerDown模式恢复,需要复位端口以保证端口可靠的连接。

bit10 Isolate

隔离状态开关:改位置1将导致PHY和MII接口之间处于电气隔离状态,除了MDC/MDIO接口的信号外,其他MII引脚处于高阻态。IEEE802.3没有对Isolate时MDI接口的状态进行规范,此时MDI端可能还在正常运行。Isolate在实际应用中并没有用到。并且,值得注意的是,由于目前很多百兆的PHY芯片其MAC接口主流的都是SMII/S3MII,8个端口的接口是相互关联的,一个端口设置Isolate可能会影响其他端口的正常使用,因此在使用中注意不要随意更改bit10的状态。

bit9 Restart Auto-Negotiation

重新启动自动协商开关:Bit9置1将重新启动端口的自动协商进程,当然前提是Auto-NegotiationEnable是使能的。一般在修改端口的自动协商能力信息之后通过Bit9置1重新启动自动协商来使端口按照新的配置建立link。

bit8 Duplex Mode

双工模式设置:Bit8置1端口设置为全双工,置0则端设置为半双工,和SpeedSelection的设置一样,DuplexMode的设置只有在自动协商关闭的情况下才起作用,如果自动协商设置为Enable状态,则该设置不起作用,端口的双工模式根据AN结果来定。对DuplexMode的修改配置也需要复位端口才能生效。

bit7 Collision Test

冲突信号(COL)测试开关:在需要对COL信号进行测试时,可以通过Bit7置1,这时PHY将输出一个COL脉冲以供测试。实际测试操作中也可以将端口配置为半双工状态,通过发帧冲突来测试COL信号,因此该配置实用价值不大。

bit6 Speed Selection(MSB)

和Bit13两位联合实现对端口的速率控制功能。

bit5 Unidirectional enable

当第12位为1或第8位为0时,该位为忽略了。

当第12位为0且第8位为1:

1:从MII接口启用传输,不管PHY是否确定已建立有效链路

0:仅当PHY确定已建立有效链路时,才启用从MII接口传输

Bits 4:0 reserved

保留位,它们应写入为零,读取时应忽略;但是,PHY应返回这些位中的值零。

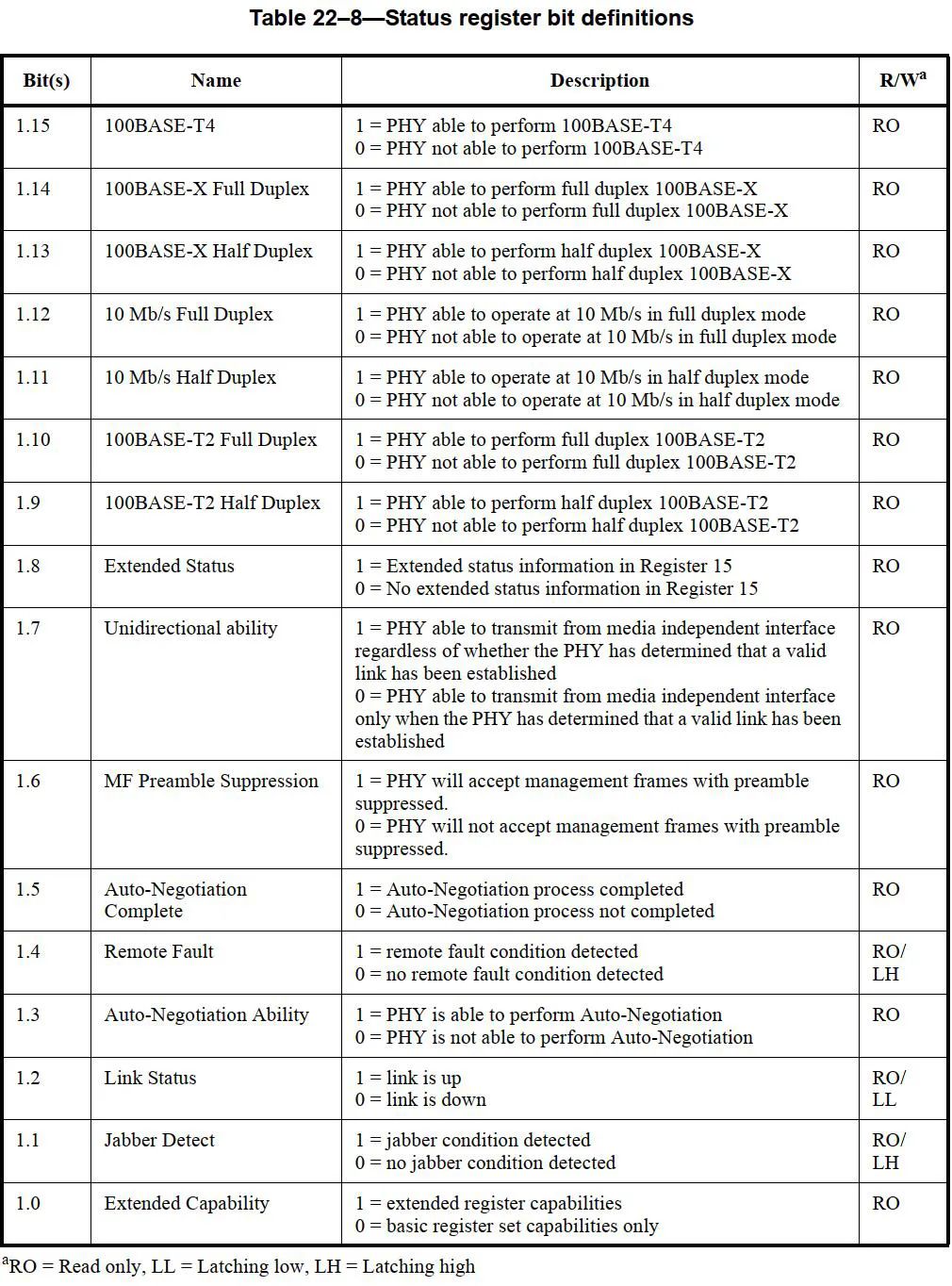

02 状态寄存器(寄存器1) 寄存器1是PHY状态寄存器,主要包含PHY的状态信息。

bit15 100BASE-T4

PHY使用100BASE-T4信令规范执行链路传输和接收的能力。1:具有能力;0:不具有能力。

bit14 100BASE-X Full Duplex

PHY使用100BASE-X信令规范执行全双工链路传输和接收的能力。1:具有能力;0:不具有能力。

bit13 100BASE-X Half Duplex

PHY使用100BASE-X信令规范执行半双工链路传输和接收的能力。1:具有能力;0:不具有能力。

bit12 10Mb/s Full Duplex

PHY具有以10Mb/s的速度运行时执行全双工链路传输和接收的能力。1:具有能力;0:不具有能力。

bit11 10Mb/s Half Duplex

PHY具有以10Mb/s的速度运行时执行半双工链路传输和接收的能力。1:具有能力;0:不具有能力。

bit10 100BASE-T2 Full Duplex

PHY具有使用100BASE-T2信令规范执行全双工链路传输和接收的能力。1:具有能力;0:不具有能力。

bit9 100BASE-T2 Half Duplex

PHY具有使用100BASE-T2信令规范执行半双工链路传输和接收的能力。1:具有能力;0:不具有能力。

bit8 Externded Status

1:使能寄存器15

0:不使能寄存器15

bit7 Unidirectional ability

1:PHY有能力编码和传输来自PHY的数据通过MII接口,而不管PHY是否已确定有效链路已被连接已建立。

0:仅当PHY确定已建立有效链路时,才启用从MII接口传输

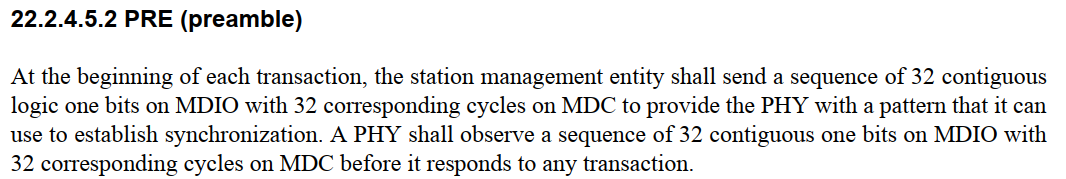

bit6 MF Preamble Suppression

1:PHY能够接受管理帧,而不管它们前面是否有前导码模式。

0:PHY不能接受管理帧,除非它们前面有前导码模式。

前导码模式。

在官方文档中22.2.4.5.2中有描述的。大家可以自行查看。

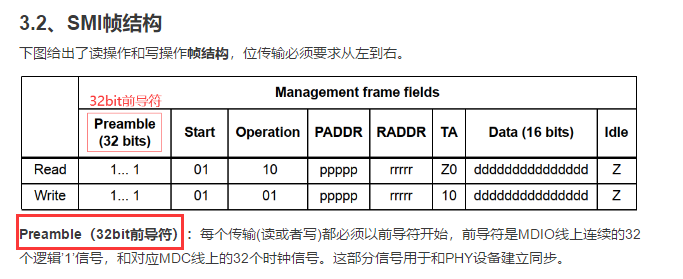

其实这个前导码我们在之前也是讲解到的,在文章《STM32网络之SMI接口》如下图,建议没有读过这篇文章的同学读一下。

bit5 Auto-Negotiation Complete

AN完成状态指示位:Bit5指示的是端口AN进程是否完成的状态位。在ANEnable的情况下,Bit5=1表示自动协商进程已经成功结束,此时PHY的其他和Link状态相关的寄存器才是正确可靠的。如果AN进程没有完成,则这些状态信息可能是错误的。在调试以及异常故障处理时,可以通过该位寄存器的状态判断AN是否成功,从而进一步的检查AN相关的设置是否正确,或者芯片的AN功能是否正常等。

bit4 Remote Fault

远端错误指示位:Bit4=1代表连接对端(LinkPartner)出错,至于出错的具体类型以及错误检测机制在规范中并没有定义,由PHY的制造商自由发挥,一般的厂商都会在其他的寄存器(Register16-31由厂商自行定义)指示比较详细的错误类型。在与端口相关的故障查证中,RemoteFault是一个重要的指示信息,通过互联双方的RemoteFault信息(可能要加上其他的具体错误指示),可以帮助定位故障原因。

bit3 Auto-Negotiation Ability

1:PHY使能自动协商

0:PHY不使能自动协商

bit2 Link Status

Link状态指示位:Bit2=1代表端口Linkup,0则代表端口Linkdown。实际应用中一般都是通过Bit2来判断端口的状态。而且,一般的MAC芯片也是通过轮询PHY的这个寄存器值来判断端口的Link状态的(这个过程可能有不同的名称,比如BCM叫做LinkScan,而Marvell叫做PHYPolling。)如前所述,在ANEnable的情况下,LinkStatus的信息只有在Auto-NegotiationComplete指示已经完成的情况下才是正确可靠的,否则有可能出错。

bit1 Jabber Detect

1:检测到抖动(戳刺)状态

0:没有检测到抖动(戳刺)状态

bit0 Extended Capability

1:PHY提供了扩展的功能集,可通过扩展的寄存器集进行访问。

0:没有提供扩展寄存器。

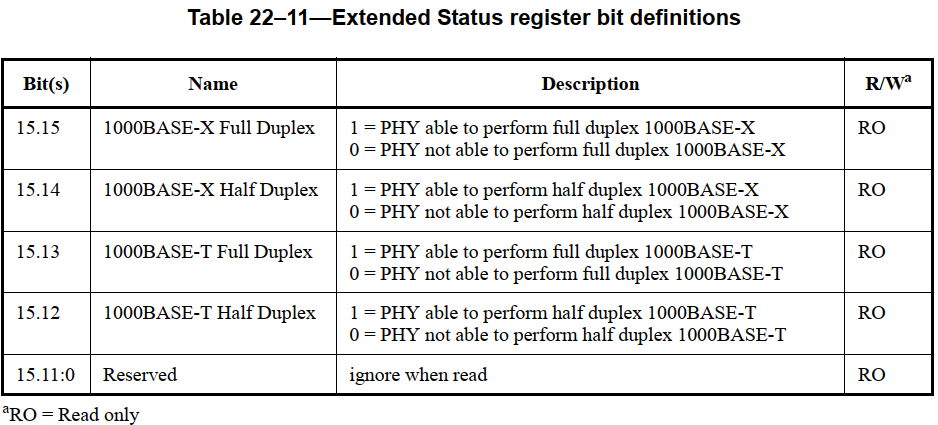

03 寄存器15 寄存器15主要模式千兆网模式下,PHY的状态。

如上图,寄存器15主要描述,千兆网模式下PHY的状态,具体含义和寄存器1的相关位差不多。

bit15 1000BASE-X Full Duplex

PHY使用1000BASE-X信令规范执行全双工链路传输和接收的能力。1:具有能力;0:不具有能力。

bit14 1000BASE-X Half Duplex

PHY使用100B0ASE-X信令规范执行半双工链路传输和接收的能力。1:具有能力;0:不具有能力。

bit13 1000BASE-T Full Duplex

PHY具有使用1000BASE-T信令规范执行全双工链路传输和接收的能力。1:具有能力;0:不具有能力。

bit12 1000BASE-T Half Duplex

PHY具有使用1000BASE-T信令规范执行半双工链路传输和接收的能力。1:具有能力;0:不具有能力。

Bits 11:0 reserved

保留位,读取的时候忽略。

04 其他寄存器 除去基础寄存器,802.3-2012协议也提到了其他寄存器,这里简单说明下,不做重点讲解。

寄存器2、3:芯片ID寄存器

寄存器2、3分别是PHYID寄存器,从内核代码知道,寄存器2(PHYID1)为高16位,而寄存器3(PHYID2)为低16位。它们作为PHY芯片的标识,一般被认为作用不大,以前有过同一主CPU搭配不同的PHY组合不同的板卡,使用同一份内核,这里就可以用PHYID来做区别。

寄存器4:自动协商通告寄存器

该寄存器保存着PHY本身具备的特性、能力。如PHY支持流控、百兆全双工/半双工、十兆全双工/半双工,等。

当设置为自动协商使能情况下通过FLP在MDI上进行通告。如果不使能,则此寄存器的配置无效。

寄存器5:自动协商对端能力通告寄存器

该寄存器和寄存器4类似,它表示对端(交换机或PC)具备的特性、能力。同样要注意是的只有在自动协商使能情况下该寄存器信息才有效。由于此寄存器表示的是对端的状态,所以一般情况下寄存器的值被设计为只读,但有的芯片如dm9000的流控位5.10FCS是可读写的。

该寄存器主要用来了解对端的情况,在出现问题时,可以了解对方的信息,从而大致定位范围。而不用一味地找自身原因。万一真的是对端的交换机出现故障,此寄存器就是有力的现场证据。

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5392浏览量

121907 -

STM32

+关注

关注

2276文章

10949浏览量

359175 -

PHY

+关注

关注

2文章

309浏览量

52058

原文标题:PHY寄存器

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

STM32和MCP2515通信,STM32这端还需要接CAN PHY吗?

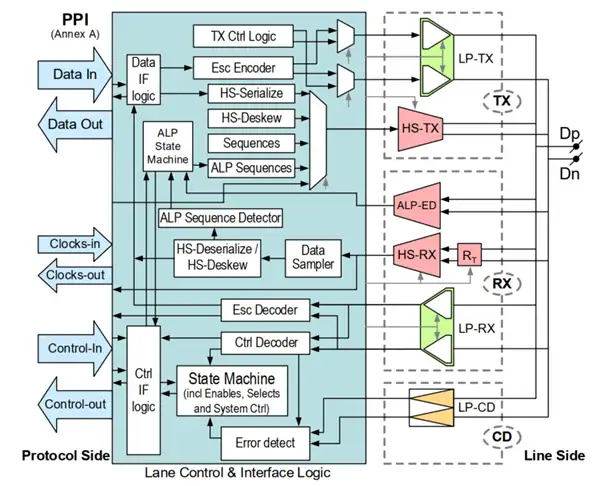

聚焦MIPI 系列之四:一文盘点D-PHY/C-PHY/M-PHY之架构与测试解决方案

TSB43AA82A/TSB43AA82AI集成PHY和链路层控制器数据表

STM32H743ZIT6想要实现千兆网口,需要外挂什么样的PHY芯片?

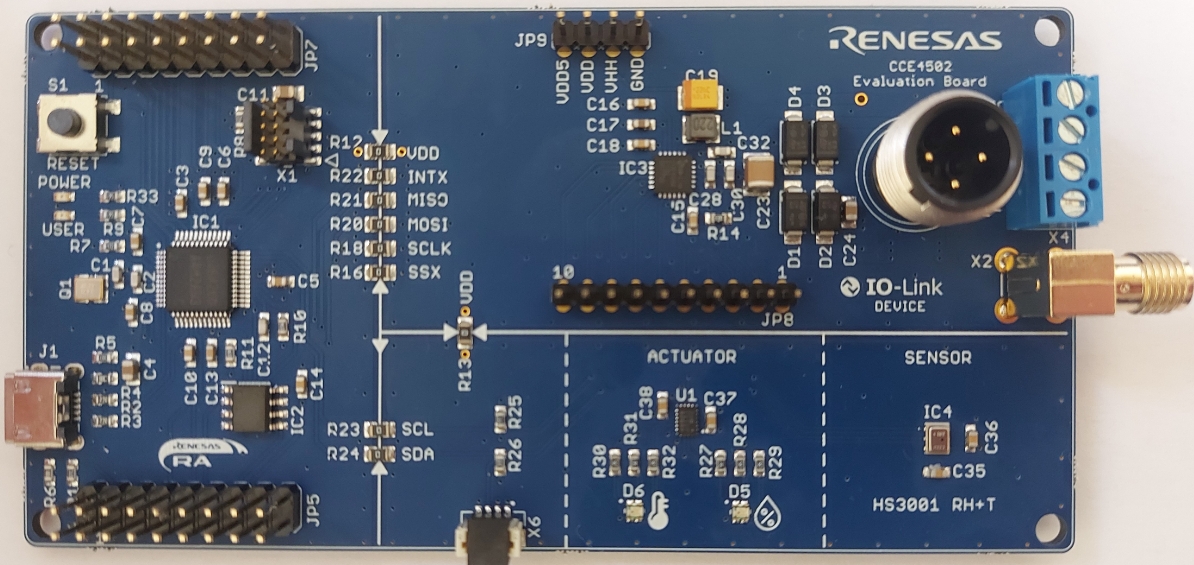

具有集成帧处理程序的IO-Link设备PHY评估板CCE4502-EVAL-V4数据手册

请问STM32F722和723系列芯片内置高速USB PHY 后高速USB速度能达到多少?

请问STM32F205的usb-otg-fs能否外接PHY使用HS模式?

stm32f730rbt6 cubemx配置内部USB HS PHY无法运行的原因?

STM32H743与STM32H745双核在外部电路上是否完全一样,是否可以不更换外部电路的情况下实现直接替换呢?

使用stm32F407外接LAN8720A时,CubeIDE进行Ethernet和LWIP进行配置,为什么不能设置PHY Address?

用STM32CubeIDE调试KZ8081网络PHY驱动,网络一直link不上的原因?

如何快速理解PHY芯片

为什么STM32不集成PHY呢?

为什么STM32不集成PHY呢?

评论