在刚刚结束的GTIC 2022全球AI芯片峰会存算一体专题论坛上,亿铸科技创始人、董事长兼CEO熊大鹏博士发表了题为“存算新动能——基于ReRAM的全数字化实现”的演讲,介绍了亿铸科技基于ReRAM的全数字化存算一体AI大算力芯片技术等深度内容,以下为演讲回顾。

AI芯片正在经历三个阶段:第一个阶段是通用CPU;第二个阶段是专用的加速芯片,其中比较有代表性的是GPU或者基于dataflow数据流、TPU这种以脉动阵列的方式对AI进行加速的芯片;而现在我们正在进入第三个阶段——存算一体芯片。从第一个阶段到第二个阶段的主要驱动力是计算工艺的提升,以加大计算能力;而第二个阶段到第三个阶段的转换我们认为主要是存储墙所导致的,大量的数据搬运带来的瓶颈使能耗增加、计算效率大大下降。

就像我们在深圳举行峰会,大家来自不同城市地区,从各自居住的地方乘坐各种交通工具来到会场,在行程住宿上花费的时间金钱精力远远超过了在会议本身上付出的成本。从某种意义上来说,这就类似于存算分离——居住的地方和会场是分开的。想象一下,如果大家都用网络视频参加本次峰会,时间金钱精力等成本就会大幅度降低,从这个角度来看,视频会议就像是存算一体——工作的地方就是居住的地方,居住的地方也是工作的地方。同样,由于存算分离,AI计算的数据搬运量非常大,会导致功耗大大增加,这就是存储墙。

此外,不管是传输还是计算工艺本身的限制,能效比已经接近极限。无论是20W,75W,150W的模组还是PCIe板卡,目前能支持的最高算力已经达到了天花板。以75W为例,不管是7nm工艺或将来会有的更高工艺,150TOPS到200TOPS已经基本封顶,这是存储墙带来的能耗墙导致的。

第三个问题我们称为编译墙或是生态墙,也可以说是可编程性,由于存算分离,数据搬运容易发生拥塞,尤其是在动态环境下,对数据进行调度和管理其实非常复杂,所以编译器无法在静态可预测的情况下对算子、函数、程序或者网络做整体的优化,只能手动、一个个或者一层层对程序进行优化,包括层与层之间的适配等,耗费了大量时间。传统架构的AI对像ResNet-50这种软件做优化通常需要几十个人花费几个月的时间,这就是存储墙带来的编译墙。

而存算一体架构可以打破传统的冯·诺依曼架构带来的这“三堵墙”。

硬件加速的基本定律叫做阿姆达尔定律,如同力学里面的牛顿定律。在这个公式中,大家可以看到一个F和一个α,F是计算所花的时间除以数据搬运加上计算时间的百分比,α取决于算力的堆叠或者工艺提升之后工作频率的提升。计算速度每年大概会提升40%,但是数据搬运的速度大概每年提高不到10%,使得两者之间的鸿沟越来越大,这个比例未来可能会小于0.8、0.5甚至更低。如果以F为0.5为例,以后无论使用多先进的工艺,性能的提升都不会超过两倍这个天花板,这也就解释了为什么基于冯·诺依曼架构AI芯片算力密度的天花板是不可避免的。

那么存算一体又为什么能突破天花板,达成线性上升呢?因为这里的F值约等于1,缓存数据搬运的时间非常小,基本上可以忽略不计,1-F接近0,这个公式在存算一体架构下,硬件加速和α呈线性关系,核数堆得越多或者工艺越先进,硬件加速的倍数就越高。这个公式就从理论上解释了存算一体可以打破传统冯·诺依曼架构算力密度、能效比等限制的天生优势。

就像其他演讲者提到的,用纯模拟的方式实现存算一体,会比传统存算分离架构下能效比提升几十甚至上百倍。忆阻器W相当于一个乘法器和加法器,在数字领域,做一个乘法器和加法器大概需要1700个晶体管左右,但在这里一个简单的忆阻器就可以代替乘法器和加法器,其系统设计的复杂性和功耗等将得到很大的优化。

当然,模拟的方式也有缺陷,比如精度问题和数模/模数转换导致的天花板问题。忆阻器是个可编程电阻,所以会受到工艺和工作环境的影响,在这些影响下,精度就会有漂移。尤其对于大算力的AI应用来说,精度期望往往是8位、16位,甚至更高。无论是人脸识别、自动驾驶还是语音识别,都有可能要求16位的整数或者浮点,而16位的精度误差不能超过百万分之一,从物理上来说,忆阻器无法达到这样的精度。

另外一个问题是模拟需要数模/模数转换,这个就带来了性能、能耗和晶圆面积过大等方面的瓶颈。所以忆阻器有优点,也有一些需要克服的挑战。要想解决这些问题,国内国外企业,包括我们自己,都尝试过数模混合的方式。也就是一部分采用数字化,另一部分采用模拟的方式实现存算一体,因为模拟和数字化各有各的好处。

这里举一个简单的例子。如果一个忆阻器表达8位或者16位的精度就会带来精度问题,那么我们仅仅用这个忆阻器表达4位的精度,如果需要做8位的计算,就用两个忆阻器来表达,算完之后得到两个结果:Y1(0)和Y1(1),通过外围的逻辑组合来完成一个完整的8位乘加。这种方式的好处就是解决了部分精度问题,因为4位精度相对来说比较容易做到,而且数模/模数转换对精度的要求不高。其不足在于不能绝对保证它的可靠性,而且数模/模数转换在性能方面还有限制,计算过程相对复杂也导致了能效比下降。

而亿铸科技采用的是全数字化存算一体,全数字化存算一体的好处就在于不管是8位、16位还是32位,不管是整数还是浮点,在整个计算过程中不受到工艺和工作环境的影响,没有精度损失,也没有数模/模数转换导致的性能低、能效比低或者晶圆面积过大等问题。能效比可以超过20TOPS/Watt,如果是在75Watt 的PCIe加速卡上做性能可以超过1POPS(1000TOPS),相对于当前主流的算力产品而言,我们用28nm工艺实现8-10倍能效比。

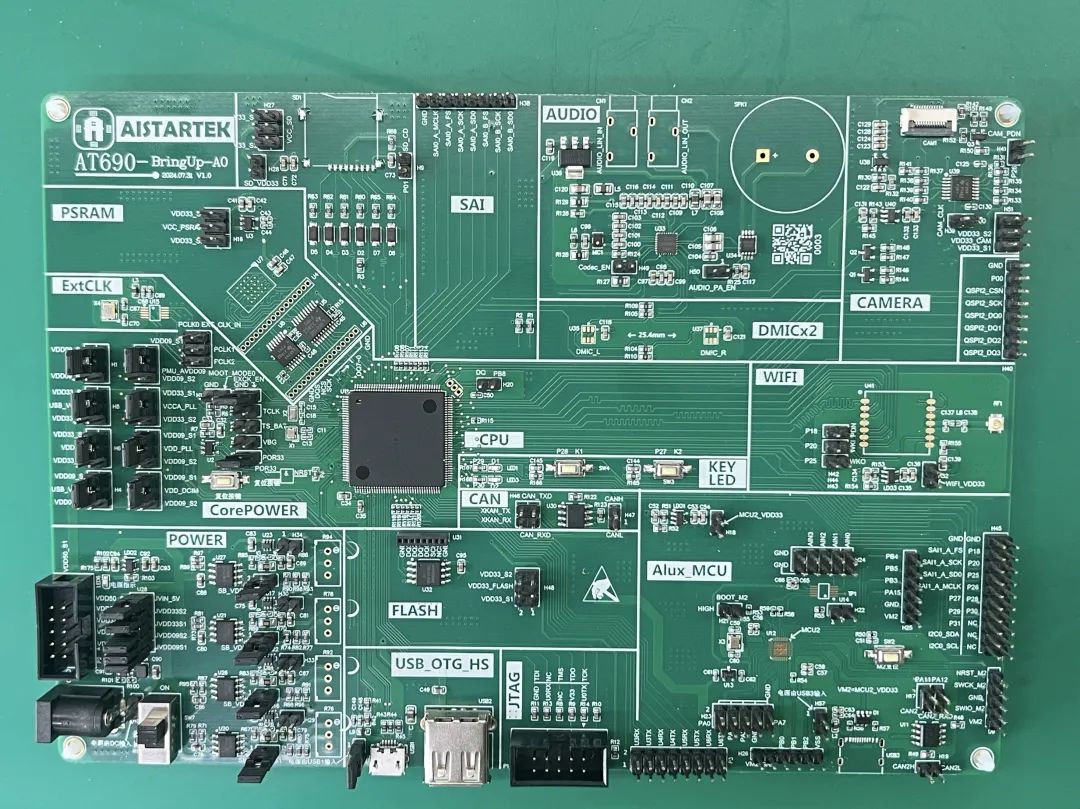

亿铸科技将存算一体作为一个IP,整体设计还包括CPU、SIMD、对外接口、ISP、Video Codec、NoC片内通讯等等,组成了一个比较完整的芯片。相比当前主流的算力产品,在同样的功耗下,能效比可以达到8-10倍的提升。另外作为整体解决方案,因为我们在AI的部分不需要外接的高性能DDR,更不需要HBM/GDDR,所以成本大概只有目前主流板卡的1/3-1/6。

说到软件和软件生态,图中左边这部分对于所有开发者来说都是公开的,下面是传统架构的AI芯片,右边和传统不同的是有后端编译优化器。存算一体有天生优势,软件开发难度相对较低,并且编译器可以自动优化,避免了每个算子、每个函数、每层的手动优化的过程。

比如,要把整个网络ResNet-50映射到ReRAM阵列里,为了对资源进行合理地优化分配,在静态的情况下采用非线性动态优化的策略,设定从frame进去到出来处理的整体时长最短为优化目标。它带来的好处非常明显——在算子库和函数库里有一些基本的素材,依赖编译器提供的工具来自动优化执行程序,可以指数级地减少程序开发员的工作。另外一个好处是,芯片落地后,终端用户部署所花费的时间、人力、物力成本也将大大减少。

最后介绍一下亿铸科技对存储介质选择的考量。存算一体有不同的介质选择:有传统存储器Flash、SRAM,也有新型存储器ReRAM、PCRAM、MRAM等等。在不同的应用环境下,每个介质都有自身的优缺点,但对于AI大算力这个特殊的细分领域来说,从成本、密度、功耗、性能稳定性等各方面综合考虑,我们选择了ReRAM,也认为ReRAM是目前最适合存算一体AI大算力的存储介质。

另外ReRAM还有很多其他优势,比如亿铸选择的忆阻器高阻值和低阻值之间的平均差异能够达到一千倍以上,带来了稳定可靠的优势,也使电路设计更加简单。另外,ReRAM可以兼容CMOS常规的工艺。

2021年被称为ReRAM的元年,从去年开始ReRAM已经商用落地、规模量产,未来的成长空间非常大。比如ReRAM可以往密度、性能两方面快速发展。从密度来说,一个是MLC多模态形式,另一个是可以往上3D堆叠,所以从迭代的潜力来看ReRAM也有十分独特的优势。

目前在28nm的工艺上,昕原半导体在去年已经开始量产ReRAM,TSMC也开始可以提供量产的能力,二者良率都在90%以上。低端工艺上也有其他厂家可以支持,例如采用Panasonic技术的UMC。

今天是存算一体专场,亿铸科技希望能够和上下游伙伴们携手打造存算一体生态,制定中国自己的标准,无论是指令集、SDK、还是开发工具等,打造我们中国自己的生态。我们相信,在存算一体这个领域上,中国和其他国家之间的技术差距非常小,甚至在某些方面还领先于世界。我们相信,只要大家齐心合力一起打造存算一体生态,一定能迎来非常光明的未来。

-

gpu

+关注

关注

28文章

4828浏览量

129719 -

芯片技术

+关注

关注

1文章

162浏览量

17711 -

AI

+关注

关注

87文章

32327浏览量

271409 -

数字化

+关注

关注

8文章

8946浏览量

62457

原文标题:亿科技 | 存算一体新动能——基于ReRAM的全数字化技术

文章出处:【微信号:亿铸科技,微信公众号:亿铸科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

济南市中区存算一体化智算中心上线DeepSeek

亿铸科技熊大鹏探讨AI大算力芯片的挑战与解决策略

存算一体架构创新助力国产大算力AI芯片腾飞

科技新突破:首款支持多模态存算一体AI芯片成功问世

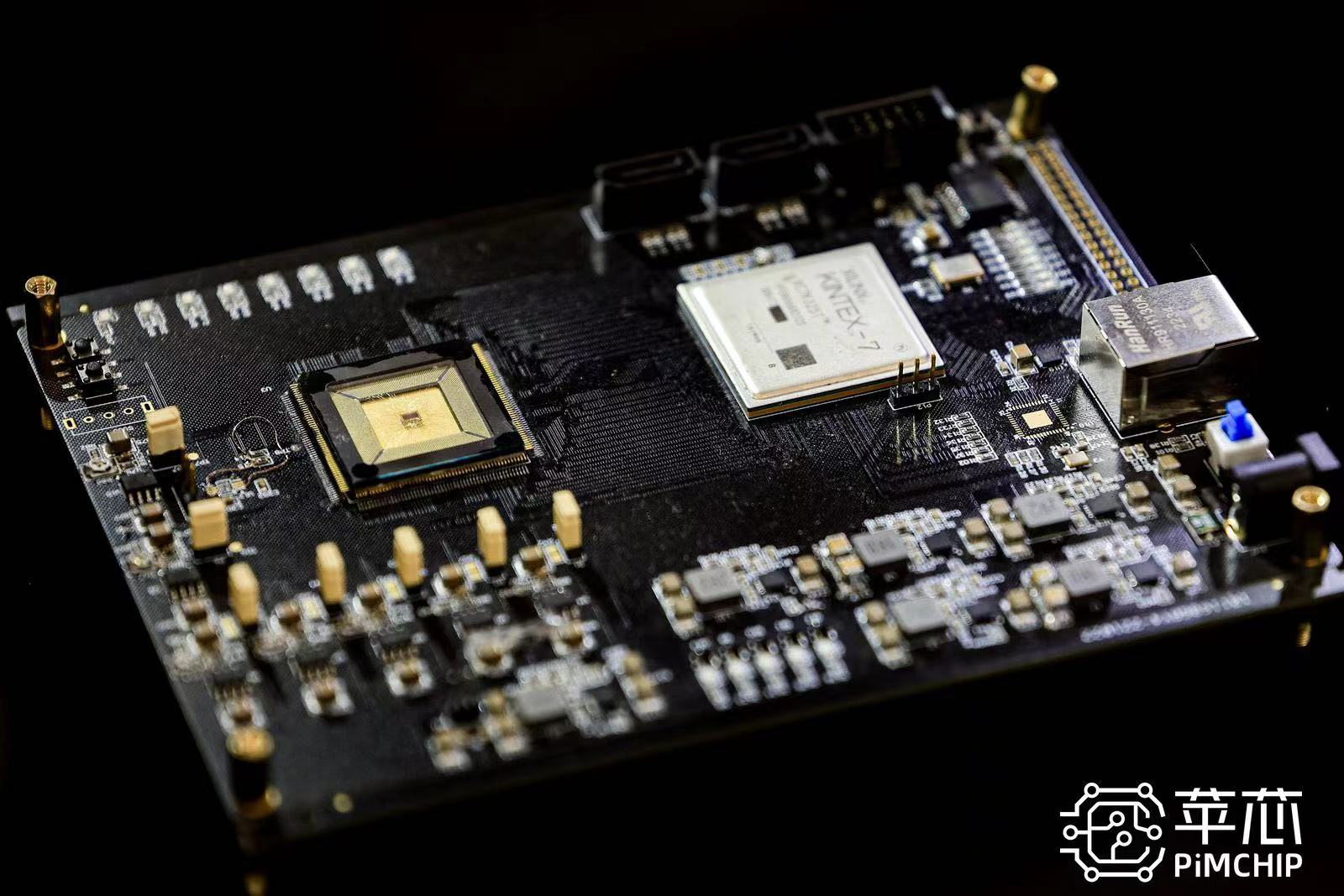

苹芯科技引领存算一体技术革新 PIMCHIP系列芯片重塑AI计算新格局

亿铸科技发布基于ReRAM的全数字化存算一体AI大算力芯片技术

亿铸科技发布基于ReRAM的全数字化存算一体AI大算力芯片技术

评论