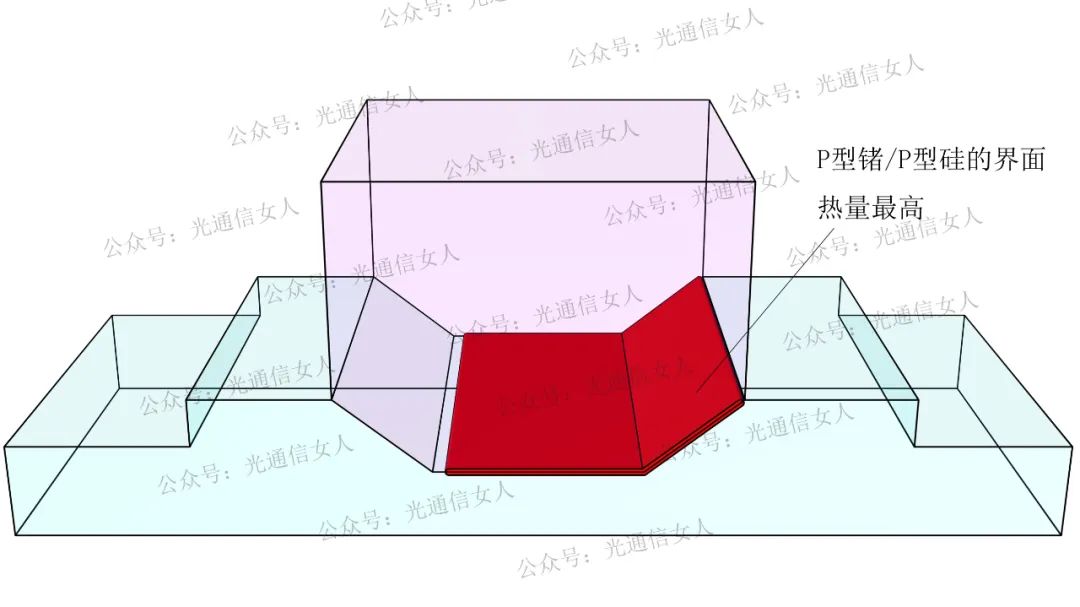

在2020合集第154页,有IMEC对锗硅电吸收调制器,锗硅探测器的一个可靠性分析,给出的内部温度分布和失效界面。

这里有个疑问,“锗和硅的界面,为什么只是在右侧温度高导致失效,而不是全部的锗硅界面?”

额~~~,这个疑问在我看起来好像不需要解释,像人每天都要呼吸空气一样,P型半导体的电阻大,所以更热。

既然聊到这里,今天略写几句。

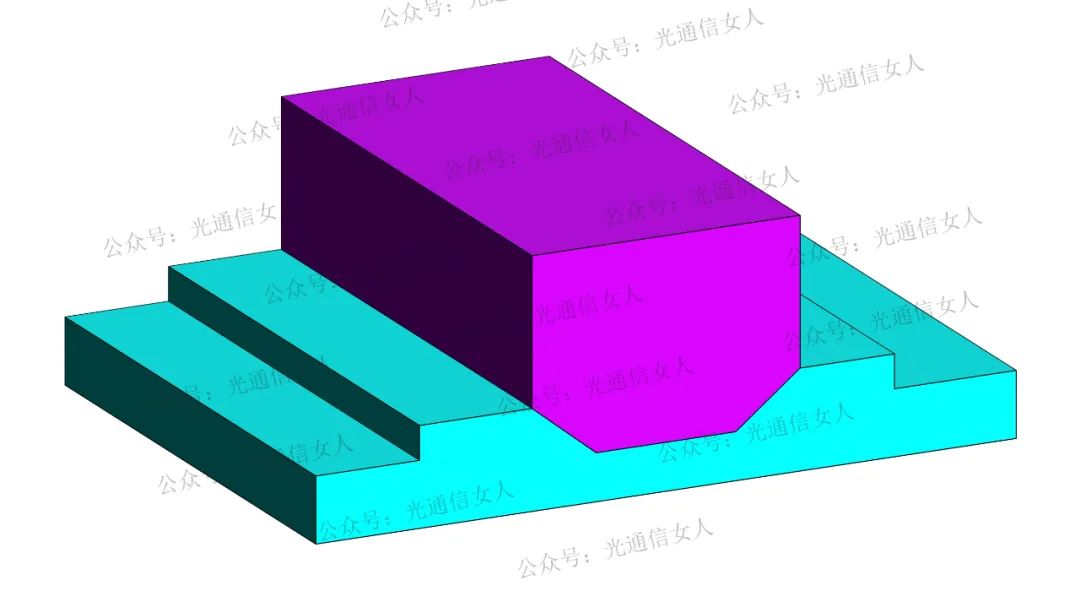

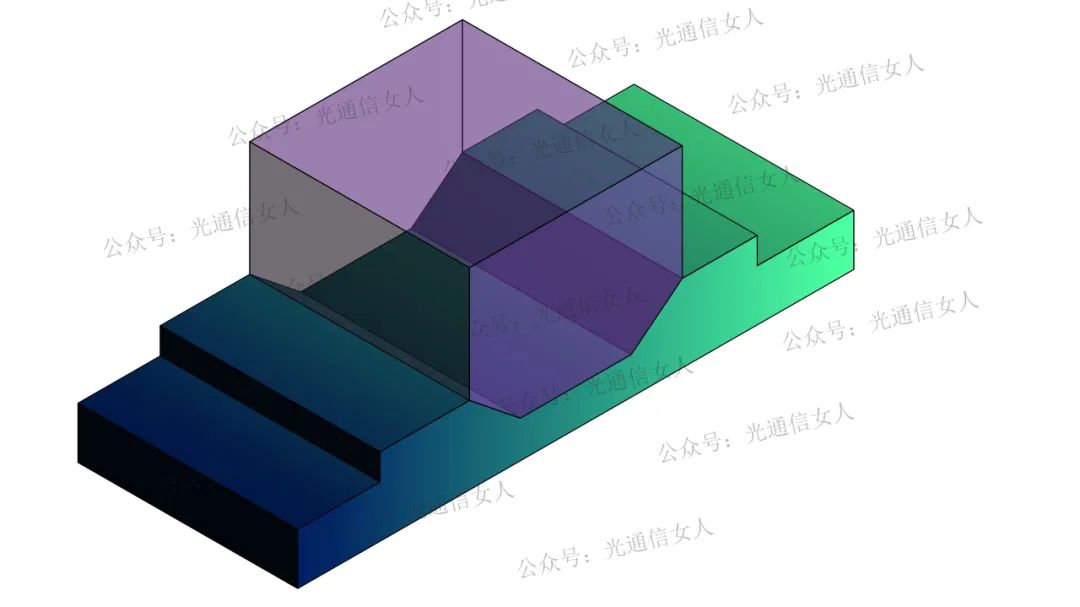

在硅波导(蓝色)上,放置锗单晶层,如下所示的紫色区域。有纵向PIN,也有横向PIN,(因为分类较多,可参考行业报告-用于光模块的硅光集成芯片技术与市场中的相关章节)。

合集中154页,IMEC是横向PIN结构,无锗接触,我用这个来解释

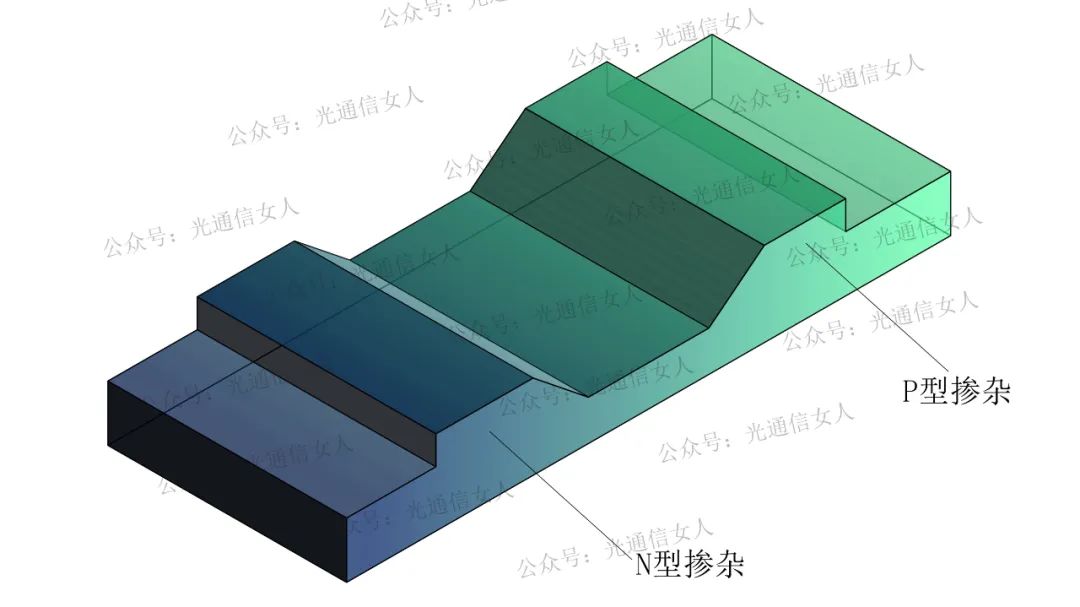

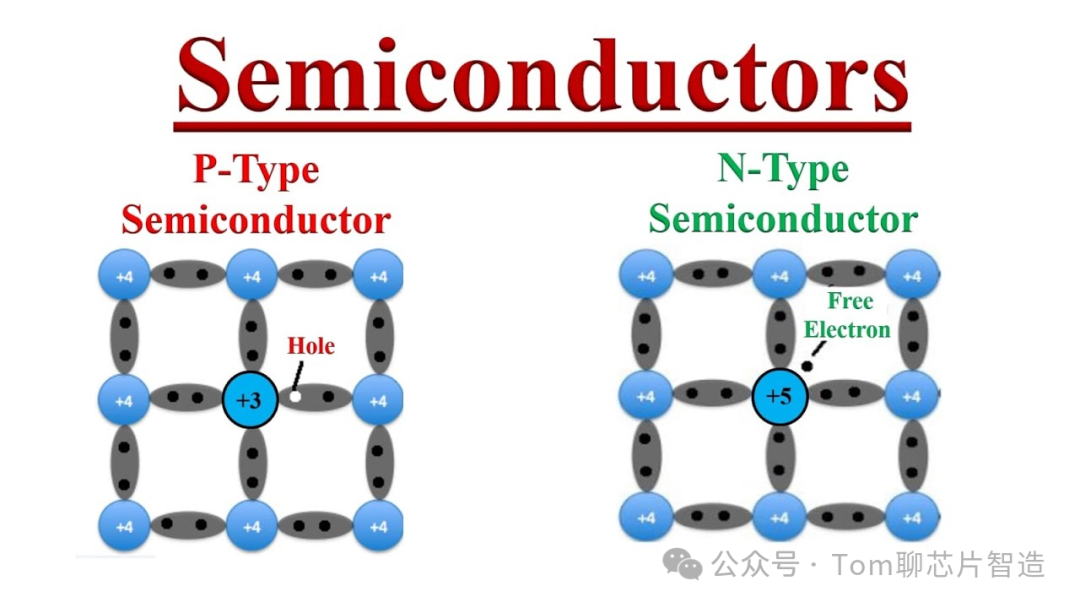

首先硅刻蚀相应的形状,且后期做杂质掺入,形成P型半导体和N型半导体,

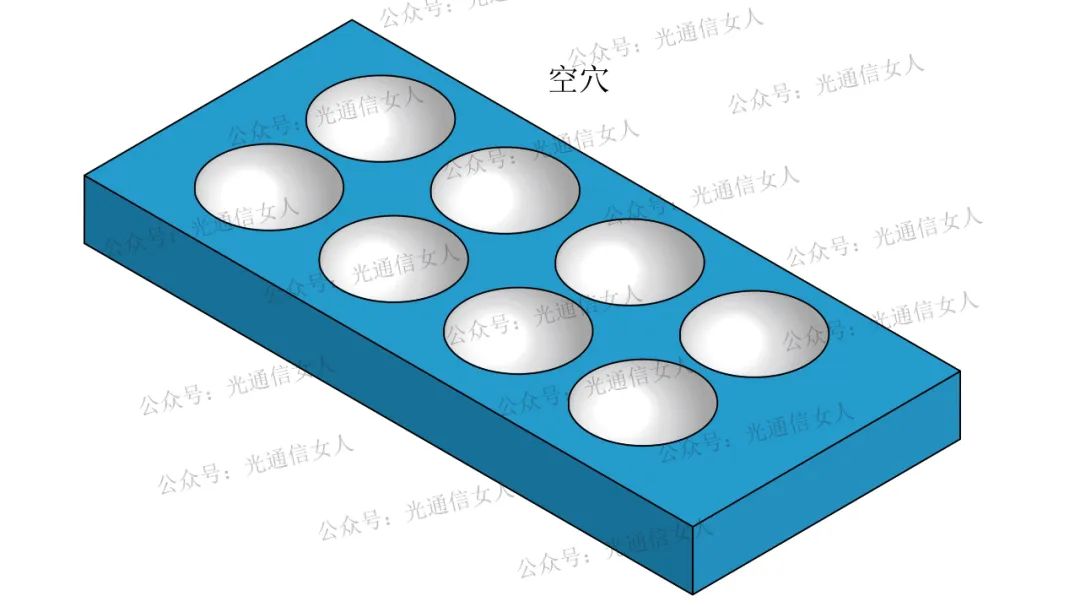

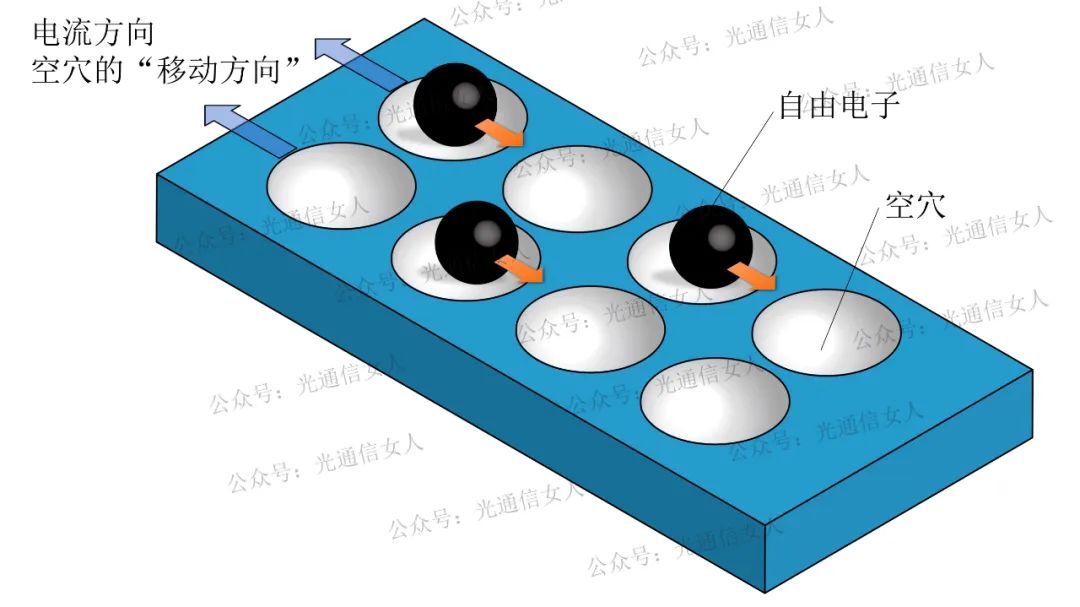

P型半导体中,原子共价键不满,形成了部分“空穴”

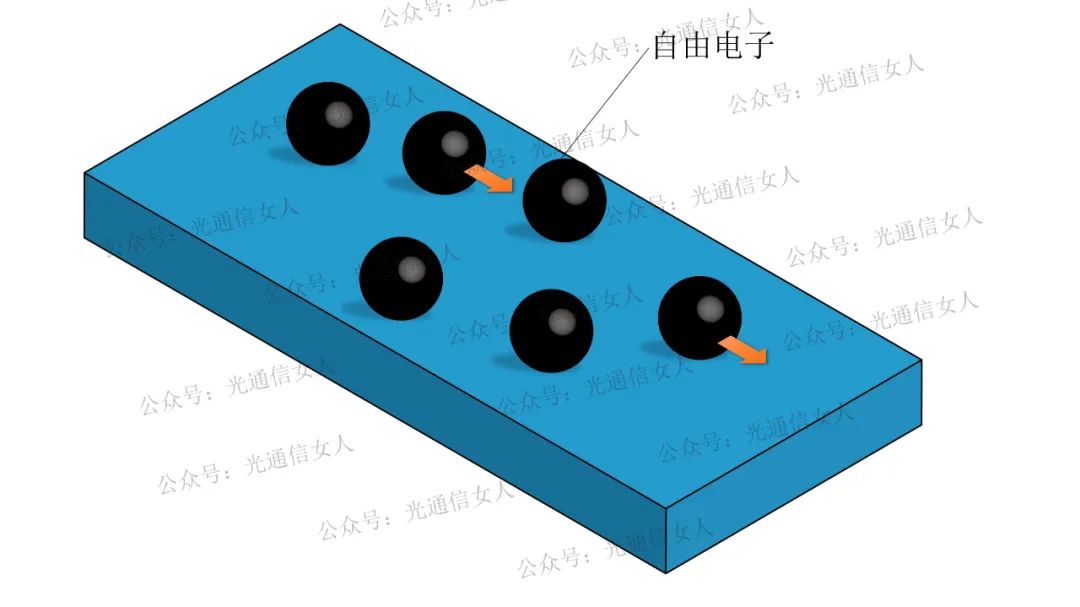

N型半导体,则是有多余的自由电子。

当锗吸收了光的能量,价电子被光从原子核外层击落,形成自由电子,原子核留下了“空穴”,这些载流子们在外加电场的作用下,被收集形成电流。

无论是P型半导体,还是N型半导体,电流的形成都是由“电子”移动形成的。

N型半导体中的电子流动,是直接形成的流动。

而空穴实际上是不动的,它就是“缺”外层价电子的一个“空洞”而已,空穴的移动是等效移动,本质依然是自由电子在电场的作用下移动,宏观上好像“空穴”在反向移动。

N型半导体,是自由电子直接移动

P型半导体,是空穴间接移动,所以迁移率不如N型半导体那么好。

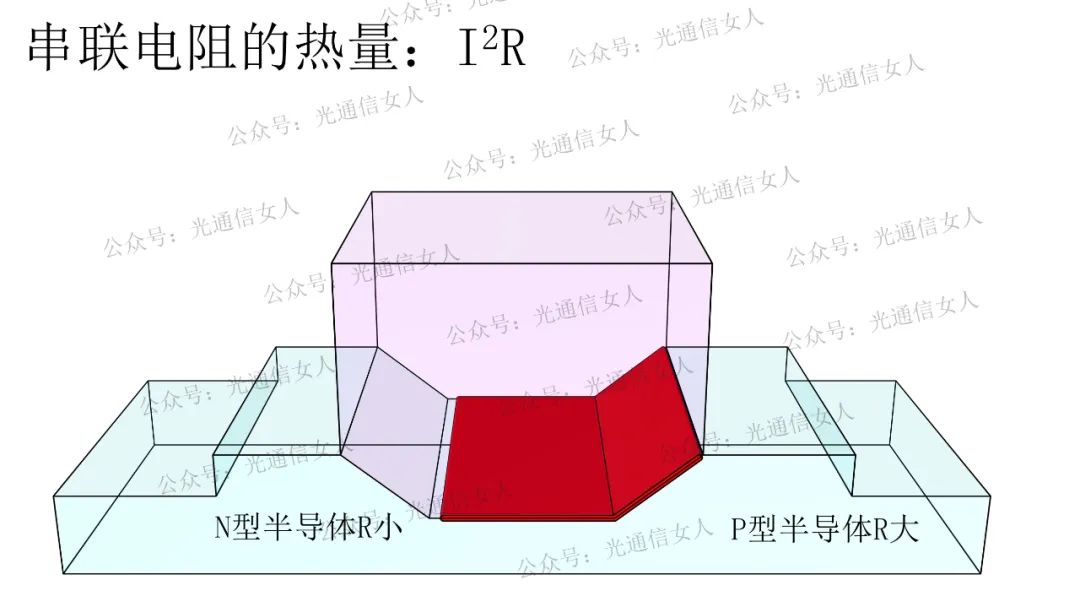

同样的掺杂浓度,P型半导体电阻比N型半导体更大。串联电阻产生的热量与电流与串联电阻有关,电流一样,电阻有差异,串联电阻产生的热量就有了分布不均匀的现象。

在P型半导体的电流路径中,也就是右侧,电流在锗和硅的界面,二者晶格不适配,出现暗点/暗线,这个界面在内热的状态下,更容易裂开,接触电阻更大,热量更集中,热熔融就极易发生在这里。

审核编辑 :李倩

-

电流

+关注

关注

40文章

7229浏览量

141684 -

半导体

+关注

关注

339文章

31316浏览量

266955 -

探测器

+关注

关注

15文章

2774浏览量

76076

原文标题:Y8T248 为何硅光集成探测器的失效界面在P型界面

文章出处:【微信号:光通信女人,微信公众号:光通信女人】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

探测器革命

[VirtualLab] 光波导系统的均匀性探测器

【封装技术】几种常用硅光芯片光纤耦合方案

烧结银膏在硅光技术和EML技术的应用

商业航天级抗辐照MCU与电源芯片在硅微条探测器系统中的应用分析

基于新兴光响应材料的光电探测器

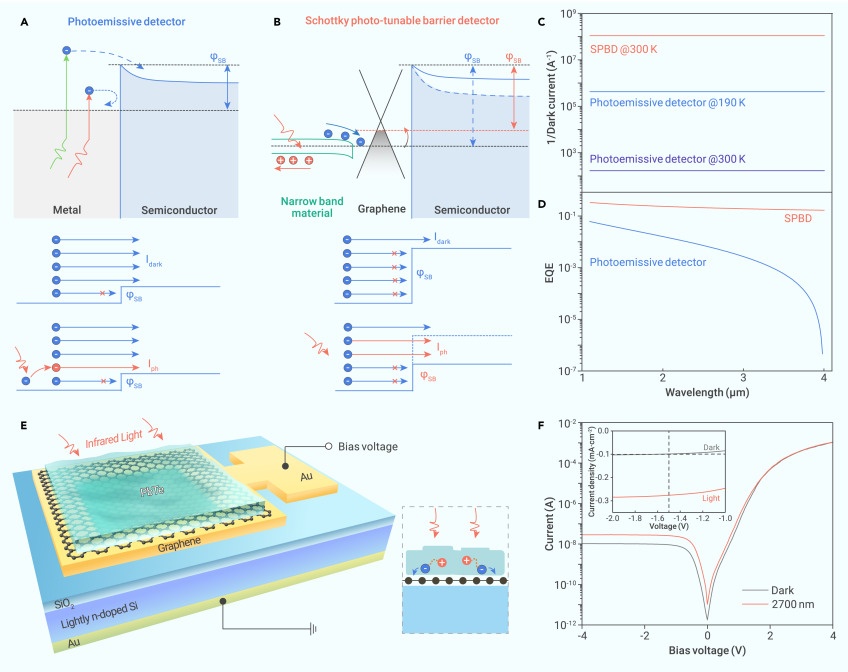

中科院重庆研究院在势垒可光调谐的新型肖特基红外探测器研究中获进展

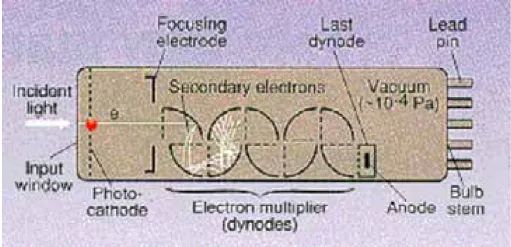

光电探测器PMT、APD、CCD、CMos、ICCD、EMCCD

表面贴装, 0201 零偏置硅肖特基探测器二极管 skyworksinc

零偏置硅肖特基势垒探测器二极管 skyworksinc

为何硅光集成探测器的失效界面在P型界面

为何硅光集成探测器的失效界面在P型界面

评论