前言

单片机其本质上还是一个计算机,当前一条指令执行完毕,CPU再根据PC取出下一条指令的地址,并再得到再下条指令地址,依次执行每一条指令。这听着不错,所有的任务在有条不紊的按照顺序执行,作为一个单核处理器的单片机,需要等待上一个任务结束才能进行下一个任务,但外界或内部发生更加重要的事情,我们不能再去等着上一个任务去执行完毕,单片机需要马上去运行相应的程序以保证实时性,如当延时时间太长时(比如10s),相应的按键检测便会失灵。但在大多数的控制场合,需要单片机立即做出反应,保证可靠性。通过引入中断机制,使CPU具有对外界紧急事件的实时处理能力。

中断这个概念可以说是所有微机的基础,甚至可以说微机就是一条条执行指令+中断。

中断

当CPU正在处理某件事的时候外界发生了紧急事件请求,要求CPU暂停当前的工作,转而去处理这个紧急事件,处理完以后,再回到原来被中断的地方,继续原来的工作,这样的过程称为中断。

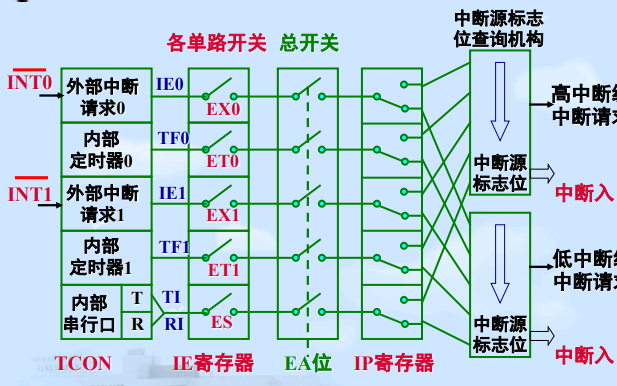

实现这种功能的部件称为中断系统,请示CPU中断的请求源称为中断源。中断系统一般允许多个中断源,当几个中断源同时向CPU请求中断,存在CPU优先响应哪一个中断源请求的问题。通常规定每一个中断源有一个优先级别。CPU总是先响应优先级别最高的中断请求。

而中断存在中断嵌套的问题,当处理低优先级中断时发生高优先级中断,系统也会保存低优先级的状态,去执行高优先级的程序,处理完以后,再回到原来被中断的地方,继续原来的工作。这样的过程称为中断嵌套,不能嵌套的称为单级中断系统,反之为高级中断系统。

STC89C51RCRD+系列单片机

IP寄存器和IE寄存器都可以支持位寻址,即可以单独配置相应位的值如

EA = 1;

EX0 = 1;

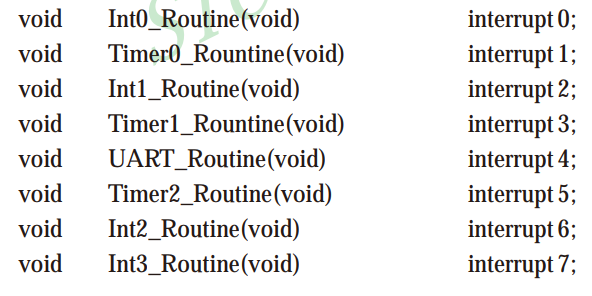

STC89C51RCRD+系列单片机提供了8个中断请求源,它们分别是:

中断优先级 IP(B8H)

STC89C51RCRD+系列所有的中断都具有4个中断优先级,传统的8051则只有两个中断优先级,这里我们按照两个配置,不配置按照默认中断查询顺序号查询。配置方法为配置IP寄存器,八位寄存器,“1”表示高级中断,“0”表示低级中断。四级中断可查看STC89C51RCRD+系列单片机数据手册。

| IP(B8H) |

| 说明 |

| 位地址 |

高优先级的中断请求可以打断低优先级的中断,反之,低优先级的中断请求不可以打断高优先级及同优先级的中断。当两个相同优先级的中断同时产生时,将由查询次序来决定系统先响应哪个中断。下图为中断查询次序表。

中断允许 IE(A8H)

通过软件设置IE寄存器的值可以去屏蔽一些中断和运行中断,只有中断运行被打开才能发生中断。更像是中断的开关,为1可以中断。复位后IE中各中断位均被清“0”,禁止所有中断。

各个中断除相应的中断允许位,还有个“总闸”EA。

| IE(A8H) |

| 说明 |

| 位地址 |

其他中断

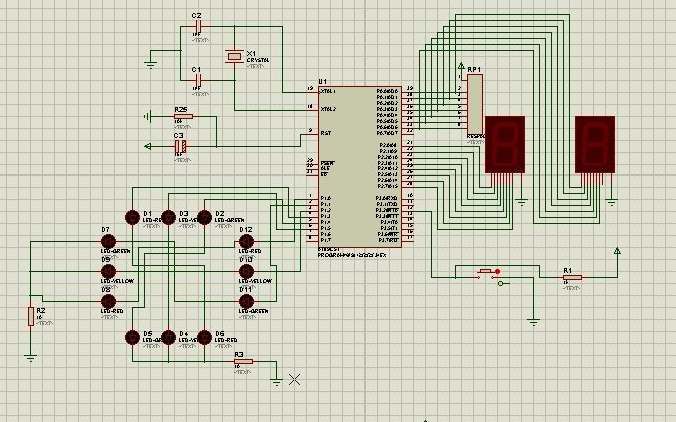

其具体的中断需要查看配置相应的寄存器,下面以外部中断为例进行配置,在学习单片机,嵌入式的路上,如果有元器件购买需求,可以去唯样商城,学生还有优惠。

外部中断

先对优先级及中断运行配置

EA=1;

EX0=1;

//不配置优先级按照默认中断查询次序

其次对外部中断的东西进行配置,比如说当外部中断0引脚收到下降沿时,就触发中断。相应的配置(定时器/计数器及外部中断控制寄存器 TCON)

| TCON |

我们只用到了IE0,IT0两位,而IE0更多的时候去读取,而不是写。因此IT0才是主要位置。当IT0=0,为低电平触发方式;当IT0=1,为下降沿触发方式。

因此我们配置

IT0 = 1;

至于低电平中断和下降沿中断的区别,在数据手册中写道

由于系统每个时钟对外部中断引脚采样1次,所以为了确保被检测到,输入信号应该至少维持2个系统时钟。如果外部中断是仅下降沿触发,要求必须在相应的引脚维持高电平至少1个系统时钟,而且低电平也要持续至少一个系统时钟,才能确保该下降沿被CPU检测到。同样,如果外部中断是低电平可触发,则要求必须在相应的引脚维持低电平至少2个系统时钟,这样才能确保CPU能够检测到该低电平信号。

个人感觉就是低电平中断更慢一些。

这样我们就可以在中断函数中写相应的控制逻辑。

void exint0() interrupt0{

//控制逻辑

}

ps:中断十分好用!!!

审核编辑:汤梓红

-

单片机

+关注

关注

6039文章

44583浏览量

636649 -

cpu

+关注

关注

68文章

10882浏览量

212293 -

中断

+关注

关注

5文章

899浏览量

41568

发布评论请先 登录

相关推荐

51单片机定时器中断_51单片机中断系统_51单片机扩展中断的四种方法

51单片机入门之中断

51单片机入门之中断

评论