前言:

CXL的全名是Compute eXpressLink。CXL是Intel在2019年提出的,希望用CXL来实现计算、内存、存储和网络的解耦,并在CXL总线上提供持久内存。

CXL发展到现在已经有几十家的会员。目前CXL协议共有个版本,分别是1.0,1.1,2.0和刚刚发布的3.0,协议规范可以在官网上下载(https://www.computeexpresslink.org/)。关于CXL,协议里面是这样说的“CXL is alow-latency, high-bandwidth link that supports dynamic protocol muxing ofcoherency, memory access, and IO protocols, thus enabling attachment ofcoherent accelerators or memory devices”。从协议给出的定义可以看出,CXL是一种低延时,高带宽的连接技术,主要支持一致性缓存,内存和IO扩展。

CXL是基于PCIe 5.0实现的连接技术,复用了很多PCIe协议的东西,这一点上与CCIX比较像,但又不完全一样。说起CCIX和CXL,难免要相互对比。其实与其说是两种技术对比,不如说是ARM和Intel两大阵营的对抗。Intel具有一定的技术优势(至少在PCIe上);但是ARM如日中天,客户群体巨大。本文旨在一窥CXL协议,无意探讨CCIX和CXL的路线之争。相信大家经过学习,会对两种技术有自己的认识。孰优孰劣,谁会笑到最后,那是大佬们的事情。

沧海一声笑,滔滔两岸潮

浮沉随浪,只记今朝

苍天笑,纷纷世上潮

谁负谁胜出,天知晓

扯完闲话,书归正传。接下来的内容是基于CXL 2.0协议的学习笔记。由于是第一次刷CXL协议,就还是按照协议的章节来。内容主要是三方面,一是对协议的翻译,由于英语水平和技术水平都有限,有些地方会不通顺;二是自己的理解,直白说就是中翻中,把不通顺的或者难懂的描述转成大白话,这里可能会有一些不太准确;三是一些基础知识的补充,前面提到,CXL是在PCIe的基础上发展而来,因此有不少复用PCIe协议的地方,但是CXL协议里面又不会阐述这些。我把暂时看不懂或者不太关心的部分都略过了,尤其是后半部分章节,日后如果有需要,二刷三刷的时候再补上。

背景知识之PCIe:

既然CXL是以PCIe 5.0为基础,我们还是有必要先简单了解一下PCIe协议。

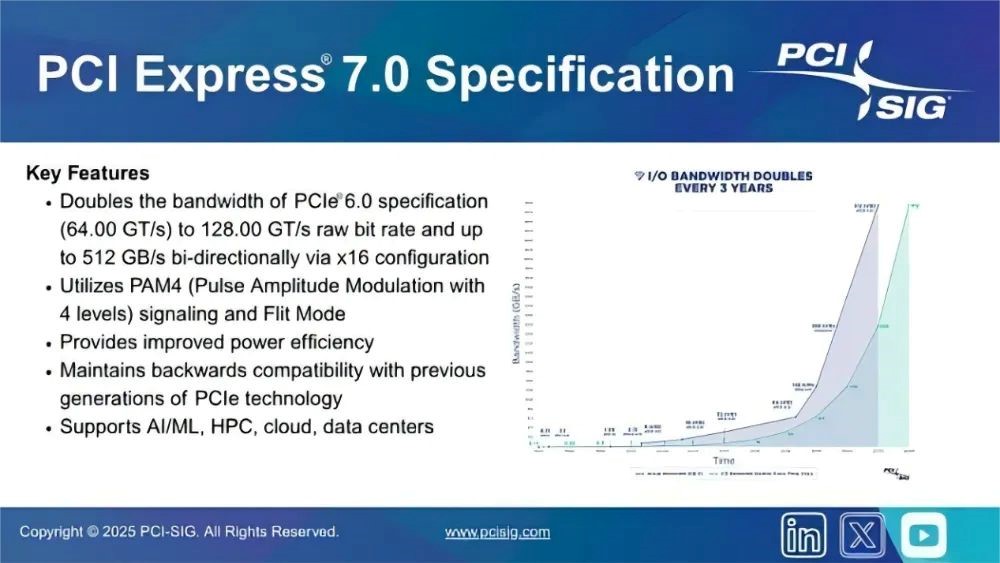

PCIe是点到点的传输,采用的是低压差分技术,一条通道(Lane)在发送(TX)和接收(RX)方向上共有四条信号线。PCIe 5.0的最大传输速率是32GT/s,也就是说单通道的最大速率是32Gb/s。如果想要提高PCIe的带宽,就需要多条通道,就像高速公路要提高交通流量就需要扩展更多的车道。所以经常会看到x32,x16,x8这些描述,后面的数字就代表通道数。通道数不是随意的,PCIe 5.0支持x1,x2,x4,x8,x12,x16和x32。简单计算可以得知,PCIe5.0最大的带宽是32*32/8=128GB/s,但这只是理论值,实际应用中需要考虑编码,数据包头等开销,有效带宽肯定要小于理论值。

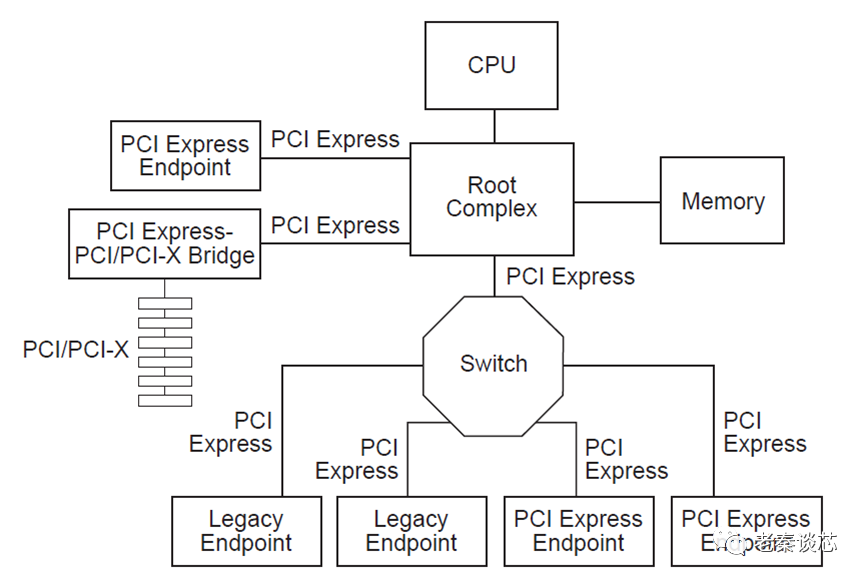

PCIe的拓扑结构如下图。

Rootcomplex:简称RC,root complex主要负责PCIe报文的解析和生成。RC接受来自CPU的IO指令,生成对应的PCIe报文,或者接受来自设备的PCIe TLP报文,解析数据传输给CPU或者内存。

Endpoint:简称EP,PCIe终端设备,是PCIe树形结构的叶子节点。EP可以分为三类,legacy endpoint,PCI Express endpoint和Root Complex IntegratedEndpoints (RCiEPs)。

Switch:PCIe的转接器设备,提供扩展或聚合能力,并允许更多的设备连接到一个PCle端口。它们充当包路由器,根据地址或其他路由信息识别给定包需要走哪条路径。

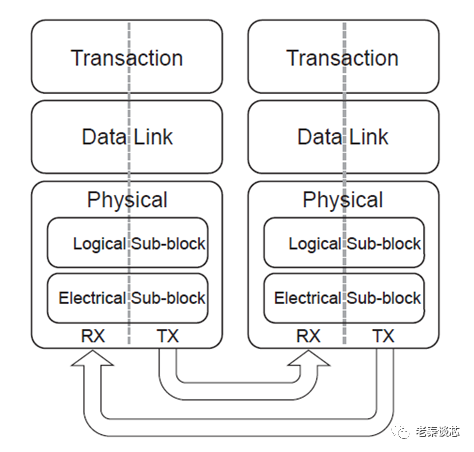

PCIe可以分为三个独立的逻辑层:事务层(TransactionLayer),数据链路层(Data Link Layer)和物理层(Physical Layer)。

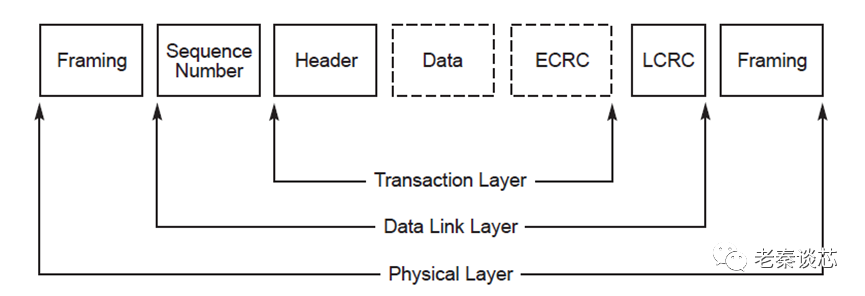

在发送端,PCIe传输的数据从上到下,都是以数据包(packet)的形式传输的,每个都是有其固定的格式的。事务层负责创建TLP(Transaction Layer packet);数据链路层接收事务层发来的TLP并创建DLLP(Data LinkLayer packet);物理层接收DLLP,然后加上帧头和帧尾,把数据分发到各个Lane传输。在接收端,物理层接收Lane上传输的数据,去掉帧头和帧尾信息,发给数据链路层;数据链路层提取出TLP发给事务层;事务层解析TLP,取出有效负载数据。

这些是PCIe最基本的知识,后面用到啥再介绍。

第一章 介绍 1.1– 1.2 略。

1.3参考文档

PCI Express Base Specification Revision 5.0 or later

ACPI Specification 6.3 or later

UEFI Specification 2.8 or later

PCI Firmware Specification 3.2 or later

MCTP Base Specification (DSP0236) 1.3.1 or later

Security Protocol and Data Model Specification 1.1.0 or later

1.4 概述 1.4.1 CXL

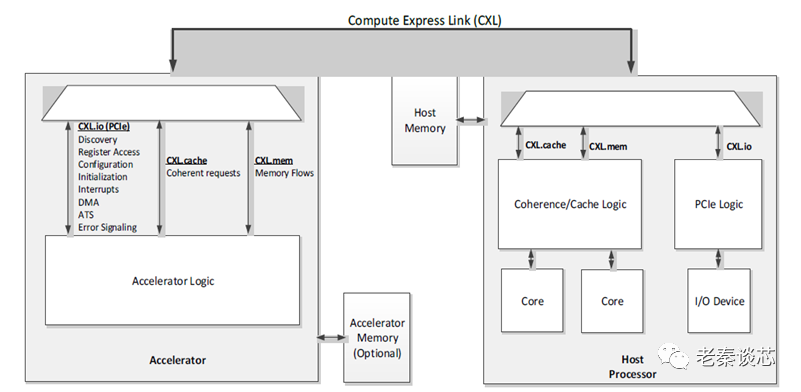

CXL在PCIe 5.0的基础上复用三种类型的协议,分别 CXL.io,CXL.cache,CXL.memory。CXL.io用来发现,配置,寄存器访问、错误报告,主机物理地址(Host Physical Address,HPA)查找,中断等。CXL.cache用来扩展系统缓存。CXL.memory 用来扩展系统存储。其中CXL.cache和CXL.memory是备选的。三种 CXL 协议分别对应一个接口。

如上图中,右侧的主机可以通过CXL连接左侧的加速芯片,其中CXL.io扩展外部I/O设备,CXL.cache扩展缓存,CXL.memory扩展存储。

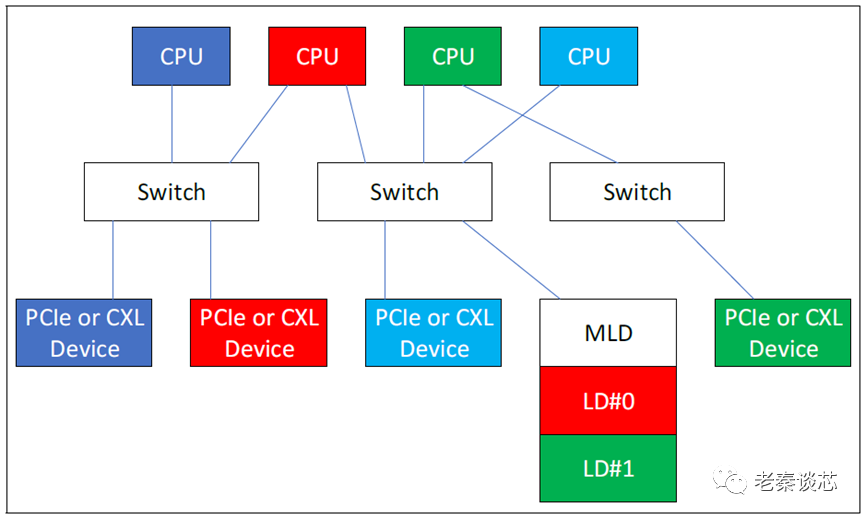

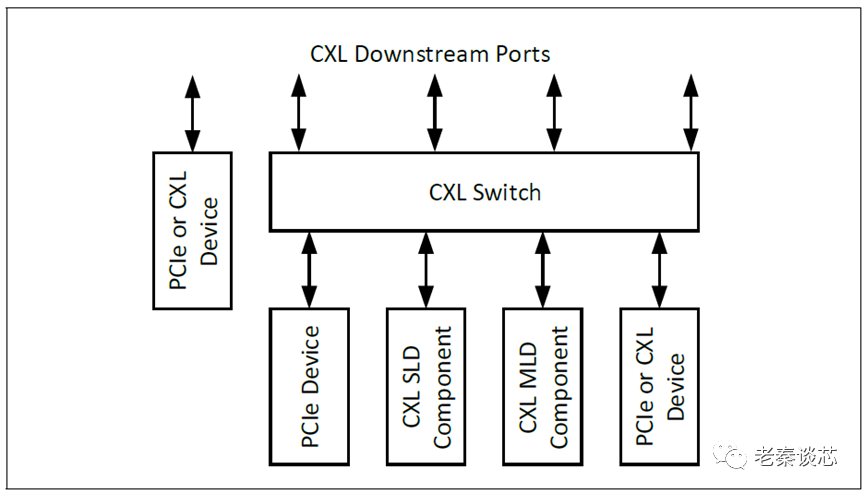

CXL2.0支持热插拔、安全增强、持久内存支持、内存错误报告和遥测。CXL 2.0还支持多扇出(Fan-out)单级交换,以及跨多个虚拟层次结构共享设备的能力,包括对内存设备的多域支持。如下图,每种颜色标识一个虚拟层次结构。其中的MLD是多逻辑设备(Multi-Logic Device),是一个Type 3的设备,后面会讲什么是Type 3设备。

1.4.2Flex Bus

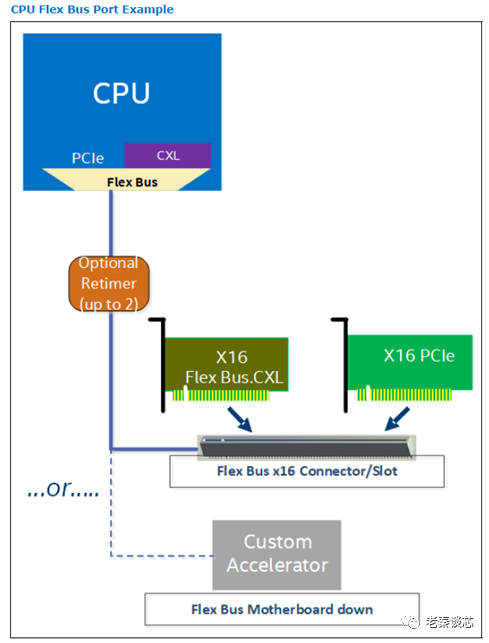

关于Flex Bus,协议里面的原话是这样说的“A Flex Bus port allowsdesigns to choose between providing native PCIe protocol or CXL over ahigh-bandwidth, off-package link; the selection happens during link trainingvia alternate protocol negotiation and depends on the device that is pluggedinto the slot.“

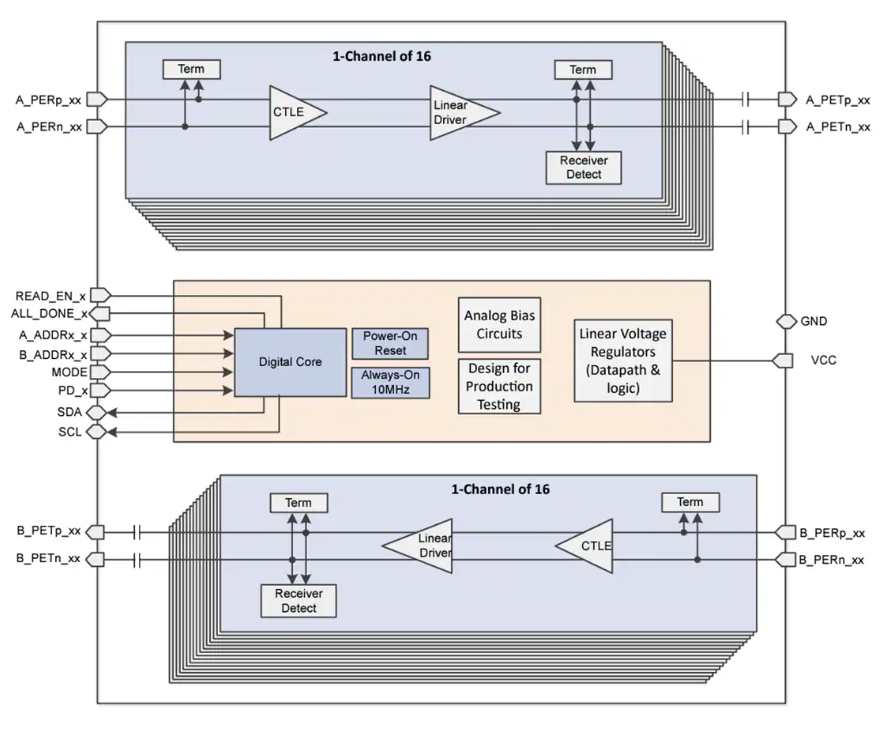

CXL也采用的是PCIe的物理层,所以对于同一个插槽上的设备,到底是CXL设备还是传统PCIe设备呢?在上电启动时,主机识别出是PCIe设备还是CXL设备,之后FlexBus就像是一个二选一,选择采用哪个协议。这样插槽就可以兼容CXL卡或是PCIe卡。在CPU和设备之间可以插入一个或两个可选的重定时器(Retimer),以延长通道长度。下图是Flex Bus的示意电路。

插播一句,关于PCIe Retimer。随着PCIe协议的不断升级,频率越来越高,对数据在线路中的传输长度提出了强烈挑战。为了解决这一问题,PCIe协议在4.0版本中提出了Retimer。Retimer实际上是一种协议感知设备,能更好地将信号传输到更远。

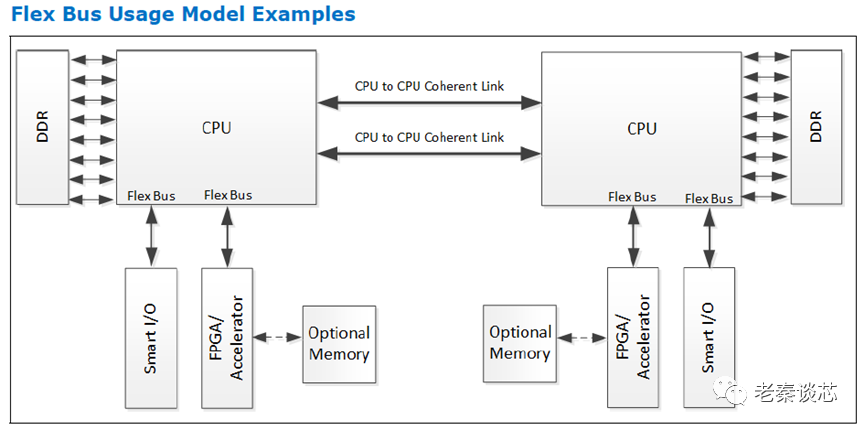

下图中显示,通过此端口可将一致性加速器或智能I/O设备连接到主机处理器。

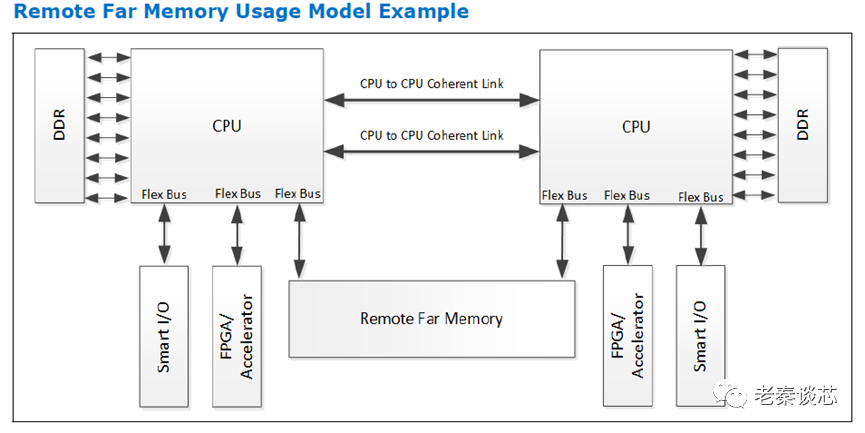

下图显示了如何通过Flex Bus.CXL来扩展内存系统。

下图显示了CXL下游端口(Downstream Port)支持的连接。

1.5 Flex Bus链接功能

FlexBus提供了一种点对点互连,可以传输原始PCIe协议或动态多协议CXL,以支持I/O、缓存和内存协议。主要的链接属性包括对以下功能的支持:

原始的PCIe模式,支持PCIe协议的全部功能

CXL模式

PCIe或CXL配置

信号速率32GT/s,降级速率16GT/s和8GT/s(CXL模式)

CXL链路宽度x16,x8,x4,x2(降级模式)和x1(降级模式)

CXL模式下对x4的分叉支持

1.6 Flex Bus 分层概述

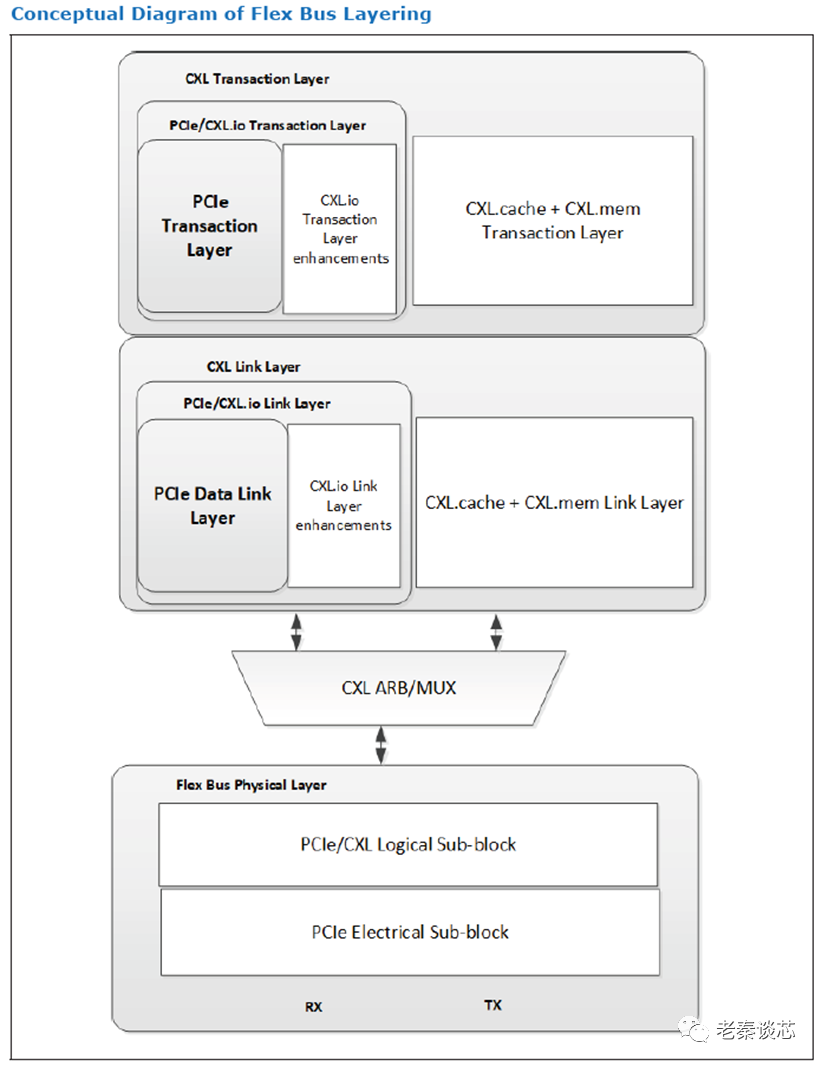

CXL事务(协议)层分为两个部分:处理CXL.io的逻辑和处理CXL.cahce和CXL.mem的逻辑。CXL链路层以相同的方式细分。如下图所示,CXL.io近似PCIe协议的事务层和链路层,但是CXL.cache和CXL.mem走的是自己单独的事务层与链路层(这是CXL延迟低的原因之一)。CXL ARB/MUX接口将来自两个通路的流量交织。

此外,CXL可以选择是否实现PCIe事务层和数据链路层,如果实现,则允许分别与CXL.io事务层和链路层聚合。作为链路training过程的结果,事务层和链路层被配置为在PCIe模式或CXL模式下运行。

1.7 文档范围 略。

本章总结:这一章介绍了CXL的基本概念,CXL协议可以分为三个部分,分别是CXL.io,CXL.cache和CXL.mem。从Flex Bus分层结构能够看出来,CXL也是在PCIe的分层架构上做了扩展。但是和CCIX不同,CXL为CXL.cache和CXL.mem增添了新的事务层(Transaction Layer)和链路层(Link Layer),所以也可以认为CXL.cache和CXL.mem是两个全新的协议。

【待续】

审核编辑 :李倩

-

总线

+关注

关注

10文章

3061浏览量

91882 -

PCIe

+关注

关注

16文章

1483浏览量

88952

原文标题:技术分享 | CXL学习(一)

文章出处:【微信号:Ithingedu,微信公众号:安芯教育科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

澜起科技发布PCIe 6.x/CXL 3.x AEC解决方案

【MCP】同时支持stdio,streamableHttpless和sse三种协议的MCP服务框架

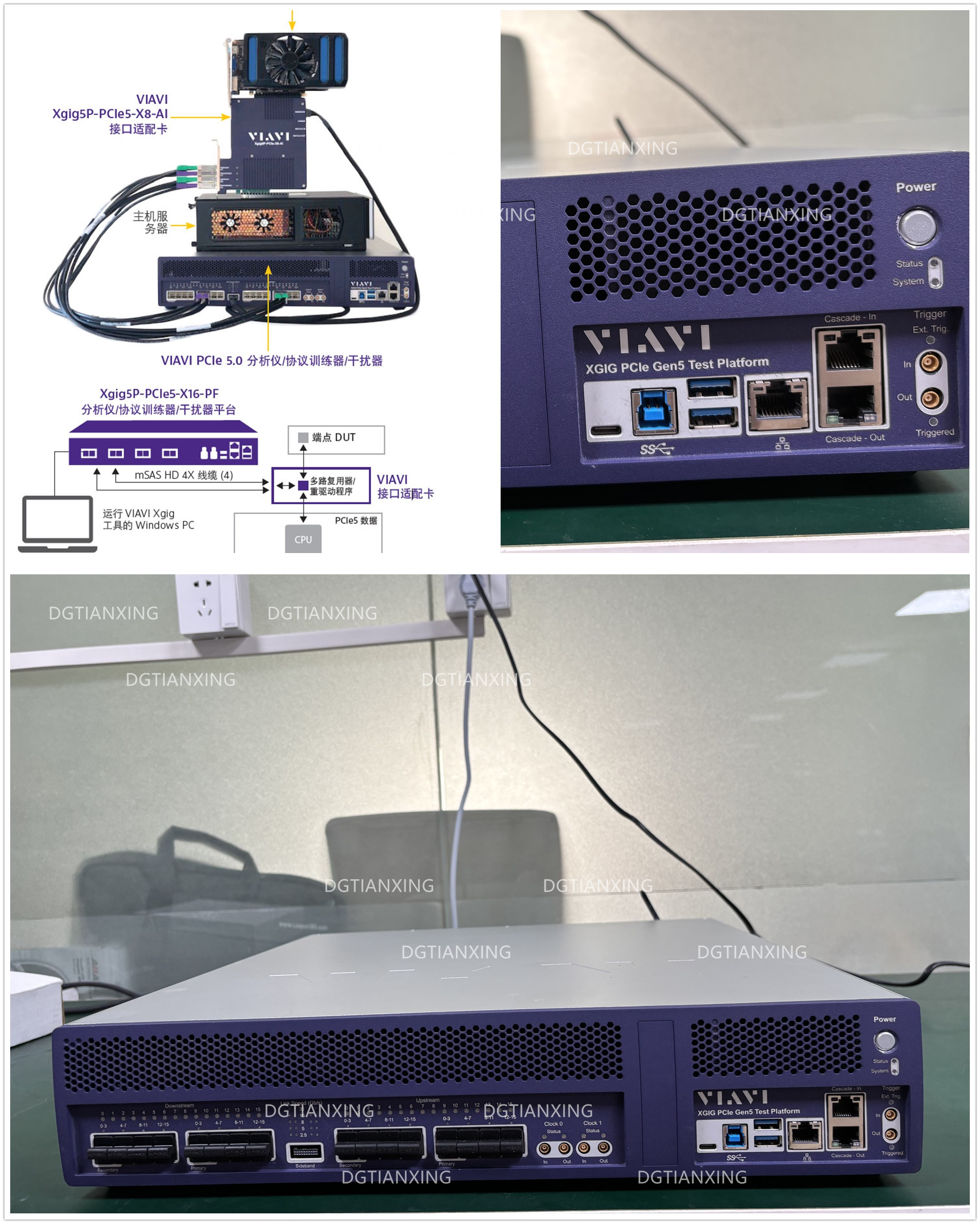

VIAVI Xgig 5P16推出全新功能,完善PCIe5.0测试需求

解析DS320PR822:PCIe 5.0和CXL 1.1的高性能线性转接驱动器

DS320PR410:支持PCIe™ 5.0、CXL 2.0的四通道线性转接驱动器

三种类型内存的使用

PCIe 5.0 8TB SSD挺进消费级市场

【干货】一文带你了解CAN、Modbus与LoRa三种通信协议的区别

DS320PR1601 PCIe 5.0 32Gbps线性转接驱动器技术解析与应用指南

Xgig E3 EDSFF 16通道内插器

PCIe协议分析仪能测试哪些设备?

PCIe 4.0/5.0仍是主流!三家SSD企业抢滩高性能存储市场,新品相继亮相

HarmonyOS基础组件:Button三种类型的使用

CXL在PCIe 5.0的基础上复用三种类型的协议

CXL在PCIe 5.0的基础上复用三种类型的协议

评论