移位寄存器的功能和电路形式较多,按移位方向分有左移、右移、和双向移位寄存器;按接收数据方式分为串行输入和并行输入;按输出方向分为串行输出和并行输出。

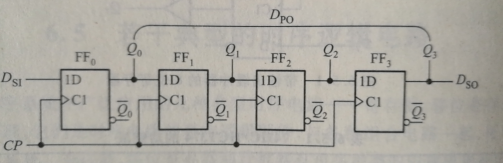

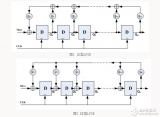

如果将若干个触发器级联成如下图所示电路,则构成基本的移位寄存器。图中是一个4位移位寄存器,串行二进制数据从输入端Dsi输入,左边触发器的输出作为右邻触发器的数据输入。若将串行数码D3D2D1D0从高位(D3)至低位(D0)按时钟脉冲间隔依次送到Dsi端,经过第一个时钟脉冲后,Q0=D3。由于跟随D3后面的是D2,因此经过第二个时钟脉冲后,触发器FF0的状态移入触发器FF1而FF0转变为新的状态,即Q1=D3,Q0=D2。以此类推,输入数码依次由左侧触发器移到右侧触发器。经过4个时钟脉冲后,4个触发器的输出状态Q3Q2Q1Q0与输入数码D3D2D1D0相对应。这样,就将串行输人数据转换为并行输出数据Dpo。

一般来说,N位移位寄存器要由N个触发器构成,需要N·Tcp来完成串行到并行的数据转换,同样也需要N・Tcp来实现并行到串行的数据输出。这里,Tcp为时钟周期。从上述操作可以看出,移位寄存器只能用脉冲边沿敏感的触发器,而不能用电平敏感的锁存器来构成,因为在时钟脉冲高电平期间,锁存器输出跟随输入变化的特性将使移位操作失去控制。显然,移位寄存器属于同步时序电路。

1.基本移位

首先说明“由于国家标准规定,逻辑图中最低有效位(LSB)到最高有效位(MSB)的电路排列顺序应从上到下,从左到右。因此定义移位寄存器中的数据从低位触发器移向高位为右移,反之则为左移。这一点与通常计算机程序中规定相反,后者从自然二进制数的排列考虑,将数据移向高位定义为左移,反之为右移。”此内容摘自《电子技术基础-数字部分》康华光主编教材。

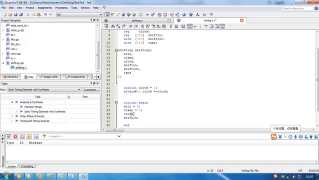

module shifter( din, clk, rst, dout,done);

input din, clk, rst;

output [7:0] dout;

output reg done; //完成移位

reg [7:0] dout;

reg [3:0] cnt;

always @(posedge clk)

begin

if(rst) //清零

dout <= 8’b0;

else if(cnt<=4’d7)

begin

dout<=dout>>1; //左移

dout[7]<=din;

/*dout <= dout<<1;

dout[0] <= din; */ //右移

end

else

dout<=dout;

end

always@(posedge clk)

begin

if(rst)

begin

cnt<=4'd0;

done<=1'b0;

end

else if(cnt==4'd7)

begin

cnt<=4'd0;

done<=1'b1;

end

else begin

cnt<=cnt+1'b1;

done<=1'b0;

end

end

endmodule

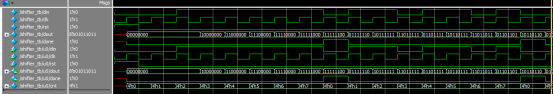

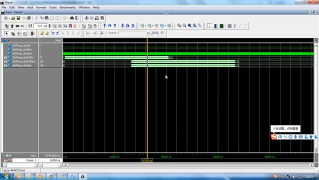

仿真结果图

2.双向移位

双向移位实现数据保持、右移、左移、并行置数、并行输出。

module two_way(

input clk,

input rst,

input s0,s1, //选择输入端口

input din1,din2, //串行数据输入

input [3:0] d, //并行数据输入

output reg [3:0] q //输出端口

);

always@(posedge clk or negedge rst)

begin

if(!rst)

q<=4'd0;

else begin

case({s1,s0})

2'b00: q<=q; //输出保持不变

2'b01: q<={q[2:0],din1}; //右移

2'b10: q<={din2,q[3:1]}; //左移

2'b11: q<=d; //并行置数

endcase

end

end

endmodule

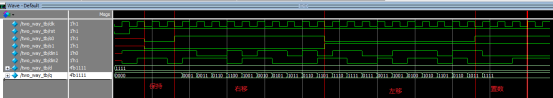

仿真结果图

总结一般掌握左移、右移方法即可,并根据实际需求加以应用,串并转换也适用。

-

Verilog

+关注

关注

28文章

1351浏览量

110346 -

移位寄存器

+关注

关注

3文章

259浏览量

22334 -

触发器

+关注

关注

14文章

2003浏览量

61322

原文标题:移位寄存器(左移、右移、双向)的Verilog实现

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

用labview模拟掷骰子次数,只能用一个移位寄存器实现

Matlab移位寄存器的实现

一维数组自动在末尾添加元素,不使用移位寄存器怎么实现

线性反馈移位寄存器原理与实现

用移位寄存器实现边沿检测的技巧

基于线性反馈移位寄存器实现CMOS电路的低功耗设计

移位寄存器的设计与实现

移位寄存器的设计与实现

评论