随着设计复杂度和调用 IP 丰富度的增加,在调试时序约束的过程中,用户常常会对除了顶层约束外所涉及的繁杂的时序约束感到困惑而无从下手。举个例子,用户在 XDC 里面并没有指定 set_false_path,为什么有些路径在分析时忽略了?那怎么去定位这些约束是哪里设定的?

事实上,Vivado 集成设计环境提供了很多辅助工具来协助用户完成时序约束的分析。

本文阐述了如何结合 Timing Constraints 窗口对设计中的约束进行查看及分析,希望为用户的设计调试提供一些思路和方向。

Timing Constraints 窗口的开启

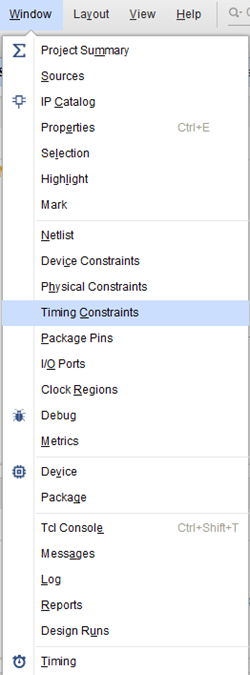

Timing Constraints窗口仅对Synthesized Design或Implemented Design适用。您可以通过以下三种方式之一找到其入口:

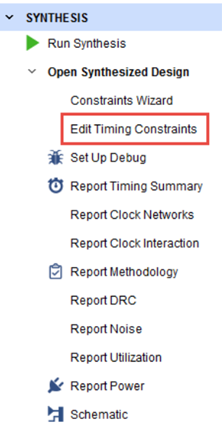

1. Open Synthesized/Implemented Design,选择菜单Windows > Timing Constraints

2. Open Synthesized Design,选择Flow Navigator里Synthesized Design 部分的 Edit Timing Constraints

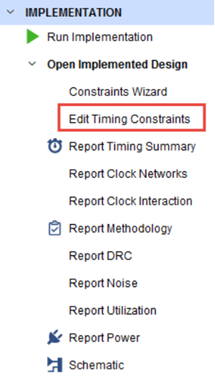

3. Open Implemented Design,选择Flow Navigator里Implemented Design 部分的 Edit Timing Constraints

Timing Constraints 窗口一览

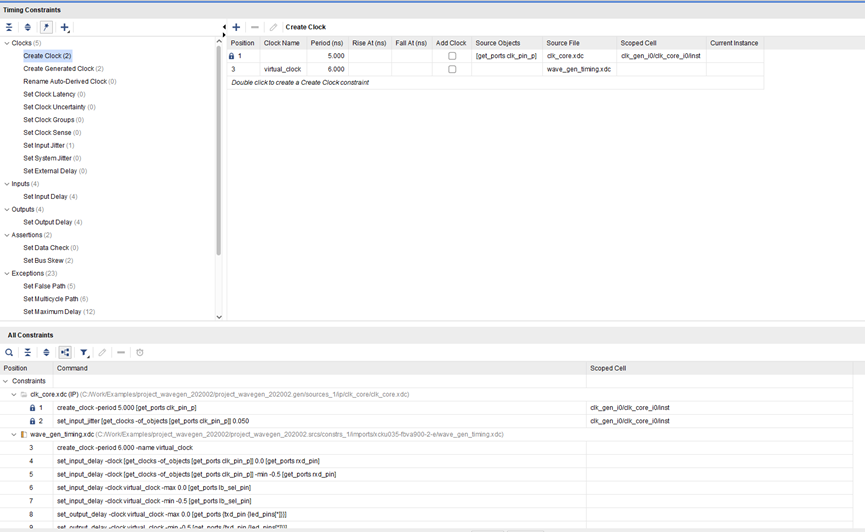

Timing Constraints 窗口可以以图示的方式直观显示当前导入的设计中所存储的时序约束,以分类组织的架构,用户可以方便地定位约束创建的顺序及来源。

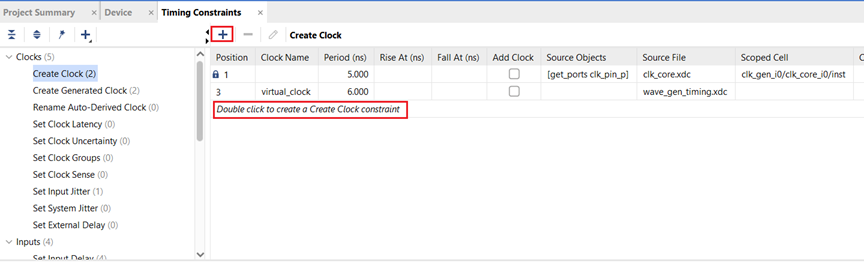

打开后的窗口整体如下图所示:

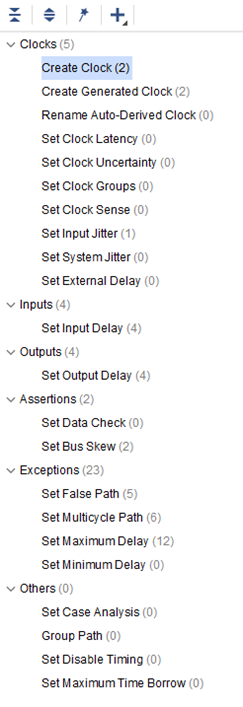

左上部分子窗口将约束做了分类,括号里是每一类约束的数量。

当选定某一类约束后,设计中所有这类约束信息会以电子表格的形式显示在右上部分子窗口。

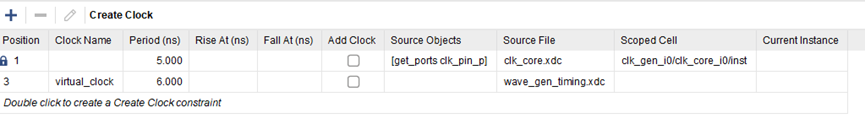

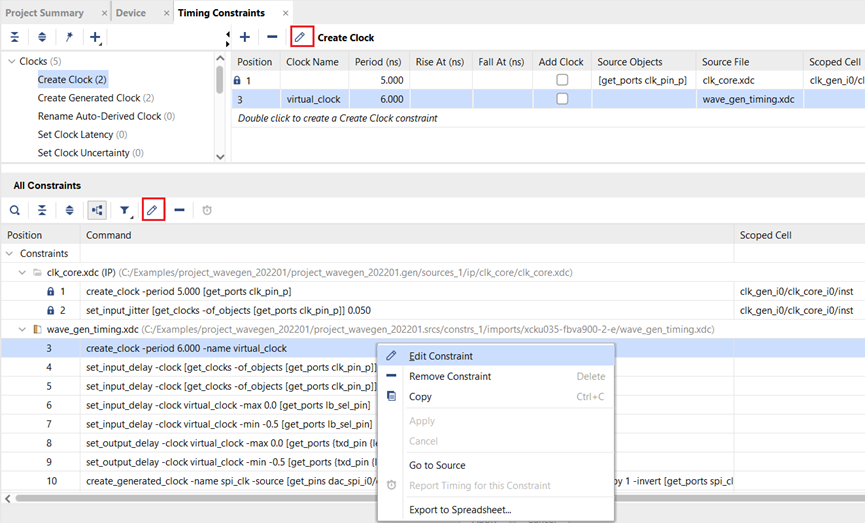

以 Create Clock 约束为例:

Position 列是约束的位置信息,跟约束的读入顺序对应。前面带锁图标表明此约束无法在表格上直接编辑,通常是 IP 自带的约束。

Source File 列显示了约束来源于哪个 XDC 或 Tcl 文件。

Scoped Cell 列显示了约束的作用范围,是全局还是某一个实例,通常此列显示的名称对应于自带特定约束的 IP 实例名。

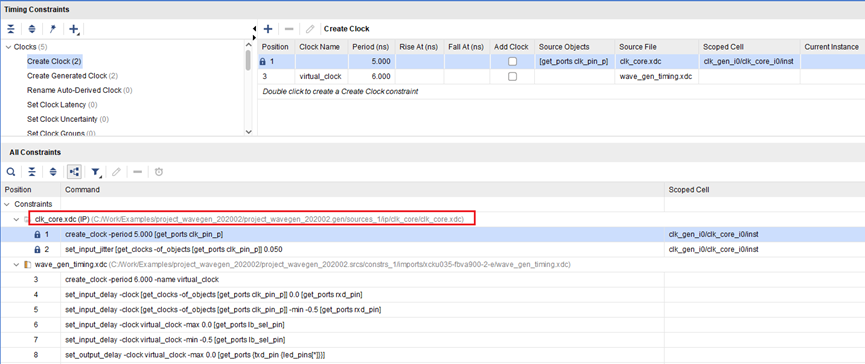

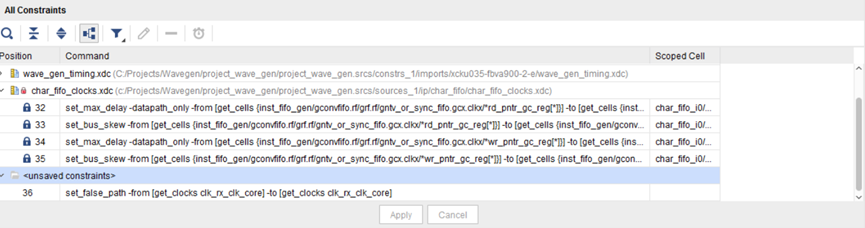

当点击某一行选中约束后,同时在下方的 All Constraints 子窗口会高亮此约束语句

用户可以快速看到原始约束语句以及其来源 XDC 的具体文件位置。

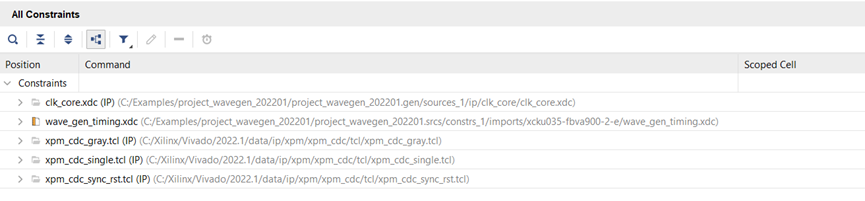

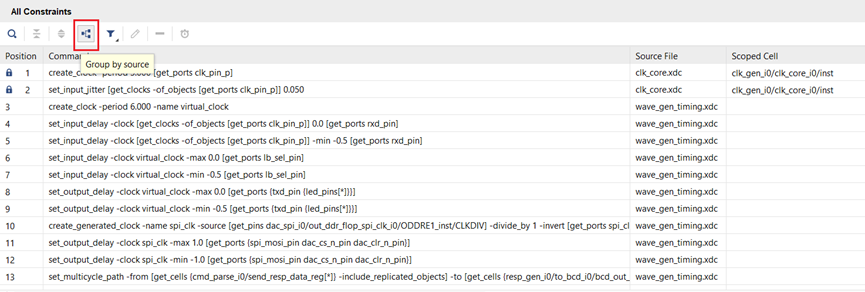

All Constraints 子窗口显示加载到内存中的约束的完整列表,其顺序与应用它们的顺序相同。 约束根据它们所源自的 XDC file 或 Tcl 脚本进行分组,根据查看需要可切换多种视图。

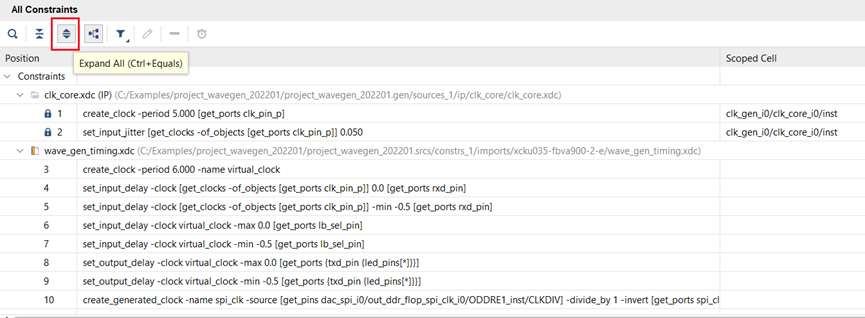

您可以点击 expand 或 collapse 图标展开或折叠每个约束文件的约束,如下图所示:

展开约束:

折叠约束:

此时点击 Constraints 旁的箭头可以看到所有关联的约束文件,进一步可以点击某个约束文件旁的箭头进行逐一查看。

您也可以取消选择 Group by Source 图标,将视图切换到一个表格,按序显示设计中的所有时序约束,其中source constraint 文件和 Scoped Cell 信息显示在右侧的两列中。

在 Timing Constraints 窗口进行约束编辑

除了在表格中查看已有约束,还可以对已有约束进行删减、修改或者添加新的约束,改动结果也会实时反映在下方的All Constraints 窗口并应用在当前的 in-memory 设计,方便用户在不重新跑综合实现的前提下进行多角度的时序分析试验。

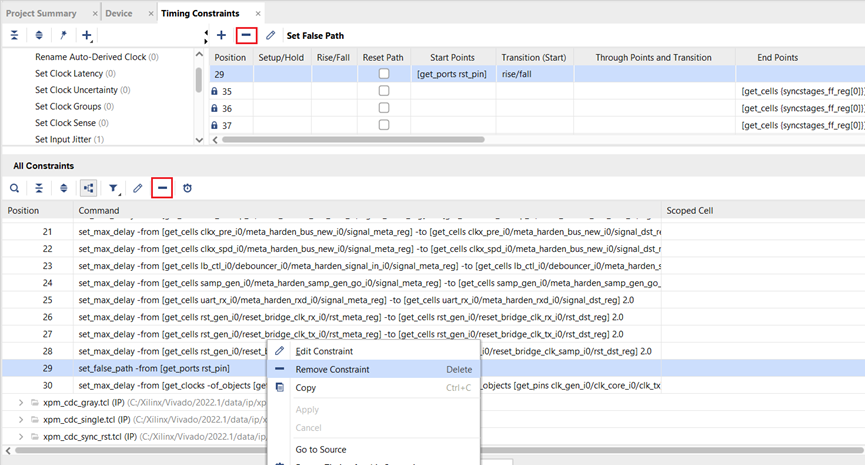

要删除某一条约束,可以从任一子窗口选中此约束,右键选Remove Constraint,或者点击-图标,并点击窗口下方的Apply 按键以刷新内存中的约束。

要编辑某一条约束(注意只能修改非只读,即约束前没有带锁标志的),可以选中此约束,右键选 Edit Constraint,或者点击编辑图标。

在随后打开的约束编辑对话框中完成修改,并点击窗口下方的Apply 按键以刷新内存中的约束。

要添加新的约束,可以点击分类表格子窗口的+图标,或者在某一类约束的空白处双击,在随后打开的对话框中将约束信息补充完整。

也可以在 Tcl Console 敲入新的约束进行添加。

新约束出现在名为的组中的列表末尾。

约束修改后可以直接在 in-memory 设计上生效,由此展开更新后的时序分析,在当前布局布线的结果上评估修改后的时序。

评估完成后,如果需要保存所作的修改,可以在 Close Design的时候选择 Save Constraints,工具会自动选择标记为 Target的 XDC 文件进行保存。如果并不想改动原始约束或者并不需要保存全部改动,可以在退出设计时忽略 Save Constraints,之后再手动修改设计中的约束文件,加入想要的改动。

总结

以上内容对 Vivado IDE 中的Timing Constraints 窗口做了介绍,与 write_xdc 命令相比,其最大的优势是能直观显示设计中所有约束的分组及来源,为时序约束的查看、验证及假设分析提供了比较方便的接口,与其他调试手段结合,可以提升设计效率。

-

接口

+关注

关注

33文章

8778浏览量

152421 -

时序

+关注

关注

5文章

392浏览量

37533 -

Vivado

+关注

关注

19文章

819浏览量

67306

原文标题:开发者分享|读懂用好 Timing Constraints 窗口

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

玩转Vivado之Timing Constraints

vivado约束参考文档

Vivado 2014.1工具流程结果不可重复

vivado挂在place_design

使用VIVADO IDE设计的最有效方法是什么?

Global Timing Constraints

Timing Groups and OFFSET Const

Achieving Timing Closure

具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束

通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束

Vivado进行时序约束的两种方式

Vivado IDE全面了解XDC文件的约束顺序

Vivado设计套件用户:使用Vivado IDE的指南

Vivado IDE 中的Timing Constraints窗口介绍

Vivado IDE 中的Timing Constraints窗口介绍

评论