本文作者:张倩忆,沈龙

Cadence 公司 DSG Product Engineering Group

先进工艺制程使得设计工程师们一次又一次突破了芯片性能、功耗和面积的极限。为了可以继续速度更快、功能更强、造价更省的追求,摩尔人依然在孜孜不倦地寻找新的方法。3D-IC 即是其中之一:通过封装和互联技术的更新使得多个裸片(die)可以集成在同一片晶片(chip)中,这样片内的高速互联就替代了之前片外的低速互联。这一新维度为未来芯片的性能提升创造了无限可能,从今年 5 月起我们(查看文末往期内容)已经连续 5 期详细揭秘了 Cadence 系统平台如何为 3D 设计者提供帮助。现在我们来看一下这其中涉及的新的互联方式和工艺集成对寄生参数和时序分析又带来了哪些挑战,以及我们如何先前一步为芯片签核人员做好准备。

uBUMP 和 TSV 的寄生如何抽取

静态时序分析的集成与扩容

如何应对 PVT 分析 corner 的爆炸式增长

设计案例

01uBUMP 和 TSV 的寄生如何抽取

首先介绍下什么是 uBUMP 和 TSV。

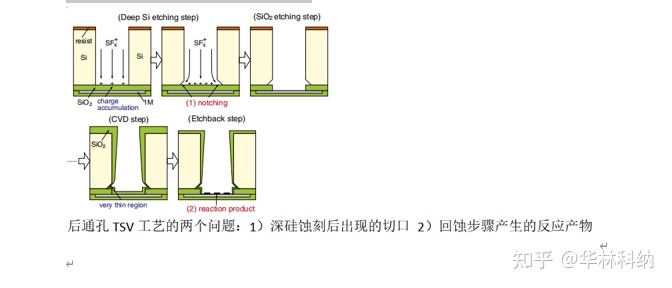

uBUMP 通常是用来连接上下两个裸片堆叠的,需要用 IPF(Inter-Process-File)文件来定义。通孔(VIA)是定义在两个相邻绕线层之间的。TSV(Through Silicon Via)是指定义在 3D-IC 工艺中连接背面第一层金属和正面第一层的通孔。还有一种 Long TSV 是指连接背面第一层金属和正面第一层以上某一层金属之间的通孔。

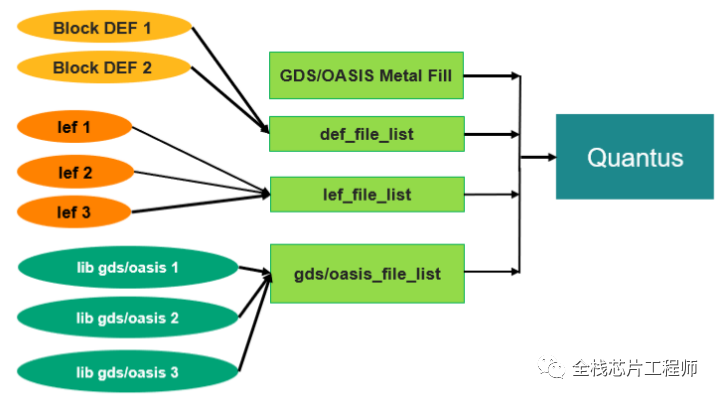

Quantus 在寄生参数抽取时对于 uBUMP 和 TSV 有两种计算方式。一种是通常在 ICT 文件中用模型语句来描述,另一种是通过定义一个额外的 TSV 模型文件(.subckt)在整体寄生参数抽取时进行标注。目前 Quantus 对于用 TSV 模型语句的方式可以支持电阻和对地电容的抽取,这些电阻电容值和普通的寄生参数抽取一样是写在输出网表中。

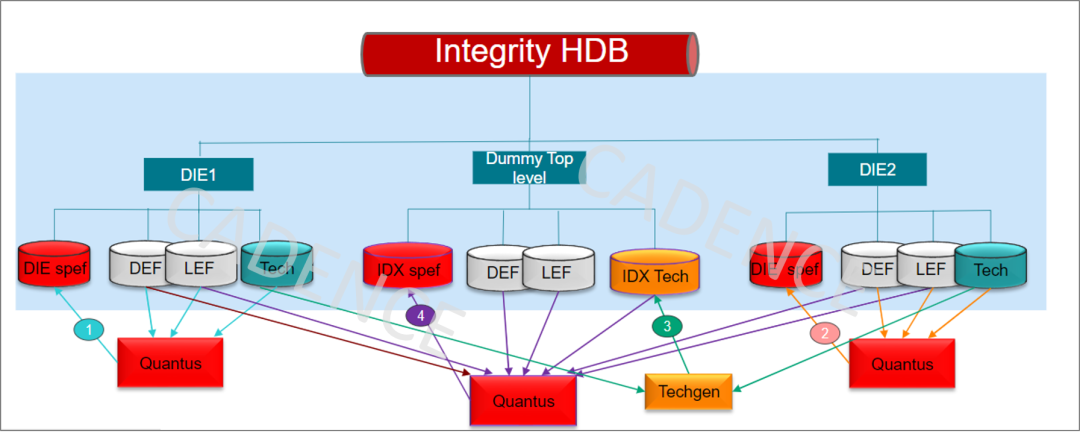

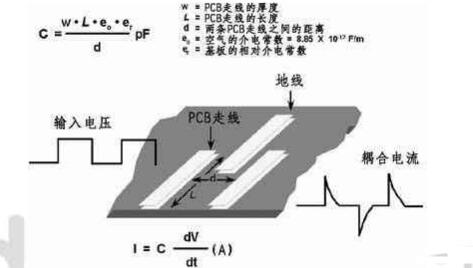

02中介层之间出现的耦合电容亟待考虑吗

基本的 3D-IC 的寄生参数抽取包括 TSV、uBUMP 还有芯片背面金属层的抽取。然而随着工艺的进步,两个 DIE 之间的距离更靠近,所以两者绕线之间的电容就变得不容忽视了。Quantus 目前可以支持 IDX 电容抽取了。IDX 是 3D-IC 中两个 DIE 之间形成的新的耦合电容,利用两个 DIE 之间的耦合电容可以做更精准的系统级静态时序分析,这两个 DIE 可以是相同或者不同制造工艺。IDX 寄生抽取支持 Cadence Integrated 3D-IC 中的 iHDB 输入,并且可以把输出结果存入 iHDB 以便后续的 Tempus 进行时序分析。

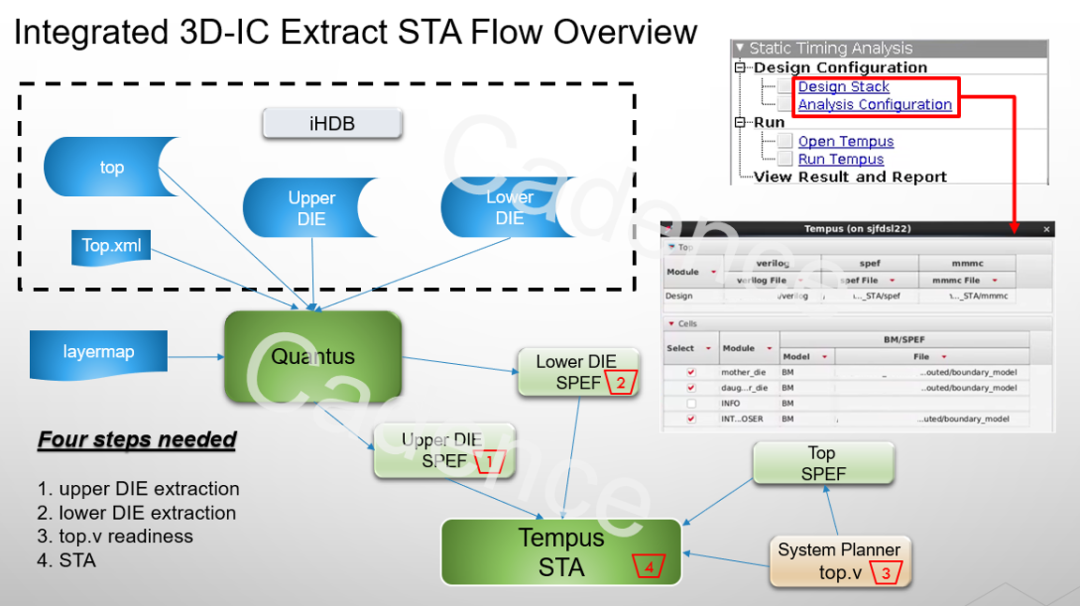

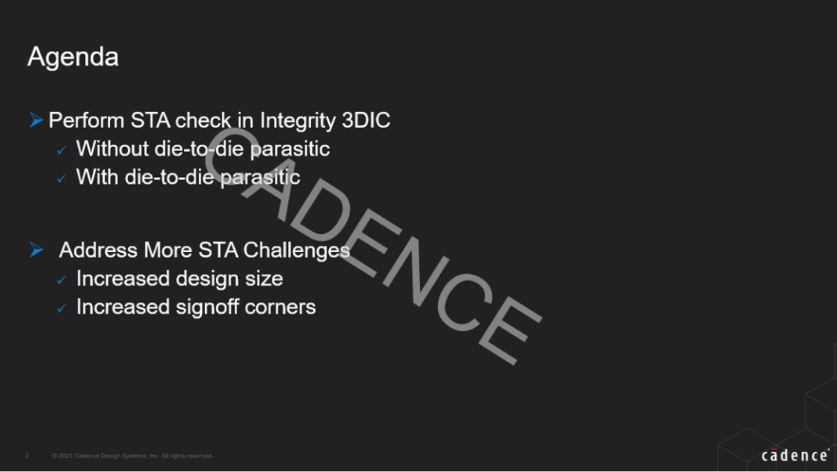

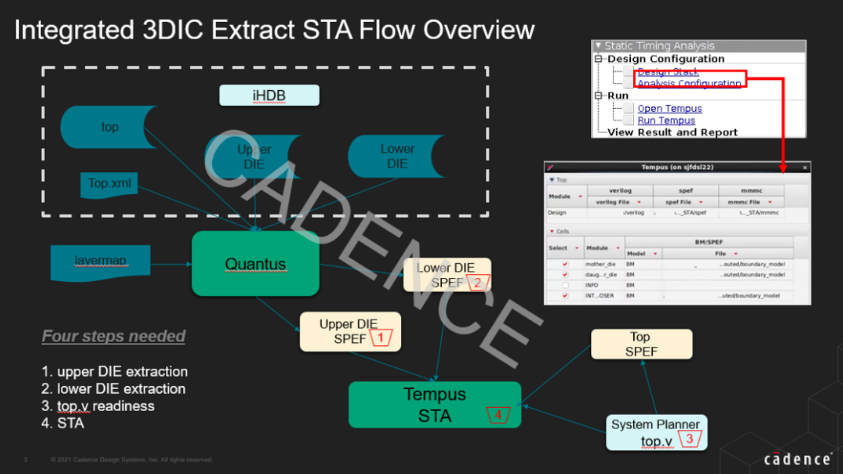

03静态时序分析的集成与扩容

静态时序分析(STA)一直是芯片签核工程师关注的重点。Integrity 3D-IC 平台自然是不能少了 STA 的功能集成。除了命令行和脚本的输入,平台的用户界面也添加了用户交互界面的支持,比如一直很受 Tempus 和 Innovus 使用者喜爱的 Global Timing Debug (GTD),该功能可以协助分析关键路径的时序违例原因。

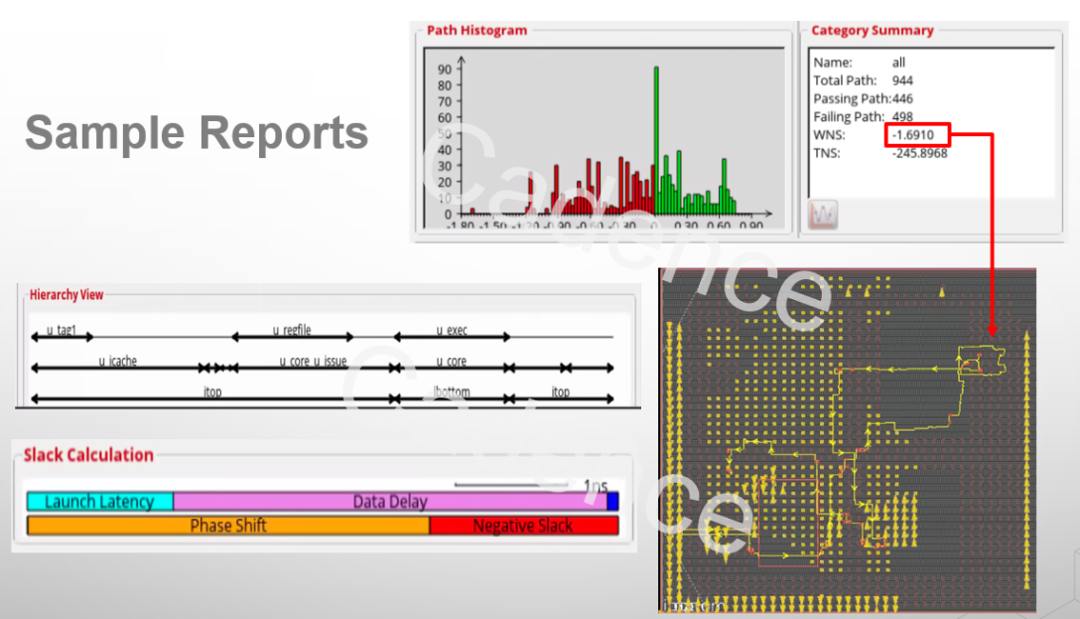

如下图所示,STA 产生报告之后,GTD 为设计工程师显示 Path Histogram、Path Layout、Hierarchy、Slack Calculation 和其他许多很有价值的分析报告和视图。具体使用描述详见 Cadence support 官网上的Global Timing Debug(GTD)using Tempus or Innovus, version 18.1(cadence.com)(请扫描下方二维码登录 Cadence Support 查看)

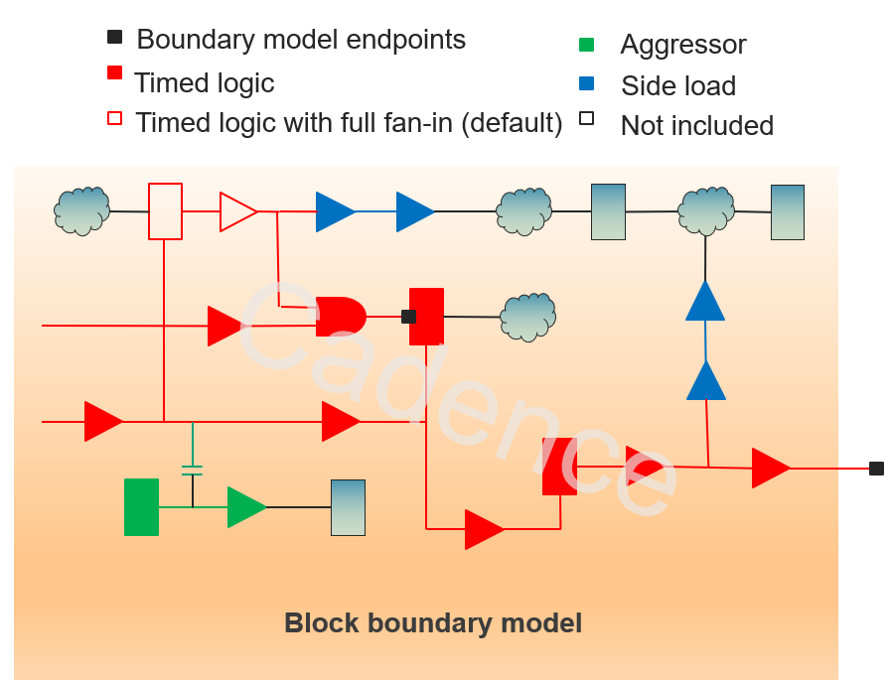

芯片的复杂度可以无限增加了,设计规模自然也随之上升。当 flatten 的全芯片分析时间过长或者内存用量过大时,就需要考虑通过抽取简化模型进行层次化时序分析。在 Tempus 里这一解决方案叫做边界模型(Boundary Mode)。如下图左所示这个模型去除了 block 内部 reg->reg 的 path 仅保留 block 对外互联以及相关联的部分,包括:

所有的 input ports 的 fan-out 逻辑和 output ports 的 fan-in 逻辑

所有对保留逻辑有 SI 影响的电路

所有保留逻辑的边负荷电路(side load)

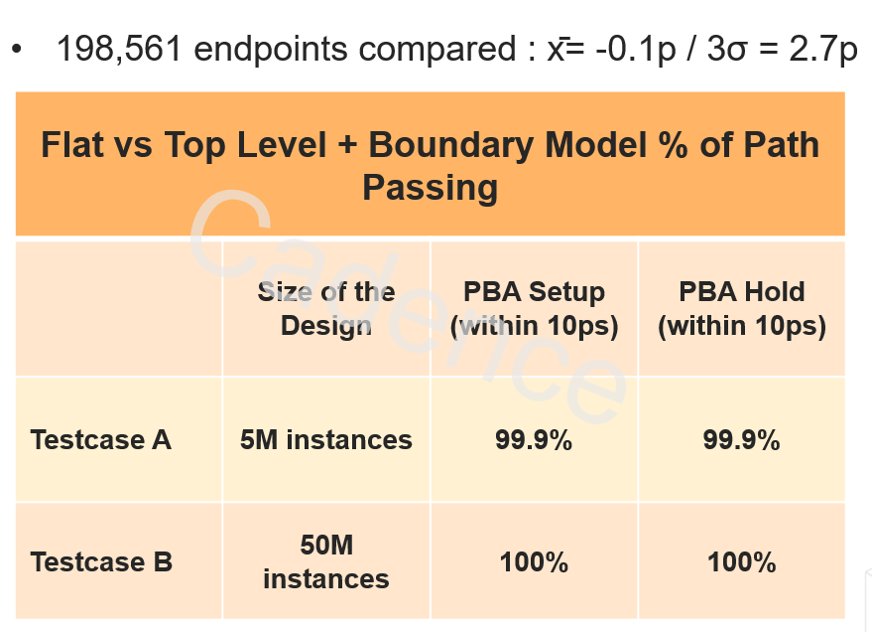

通过对每个 die 做 Boundary Model 的抽取,整体网表的缩减率可以达到 90%,而 setup slack 的平均差异控制在 0.1ps,99.73% 的路径在 2.7ps 以内。

04如何应对PVT分析corner的爆炸式增长

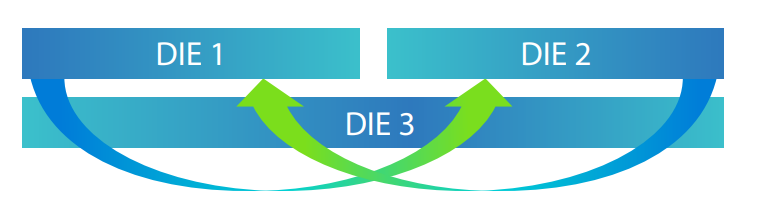

从性能的角度上来看,3D-IC 一个很强大的功能就是支持了本地的、高速的 Die 之间的同步通讯。然而这一新功能也给静态时序签核(STA)增加了大量的分析 corner。现今的设计只有一个 Die 在做全局 STA,每条时序路径都是在一组给定的 PVT 参数下做分析。在 3D-IC 设计中,多个 Die 是同时工作在不同的 PVT 参数下。设想当你有一条同步的时序路径从 Bottom Die 开始出发(startpoint),经过 Middle Die,最后抵达 Top Die(endpoint),这条 path 就会经历三种不同的 PVT 条件,好像我们从北半球旅行到南半球会穿越不同地理环境和气候。

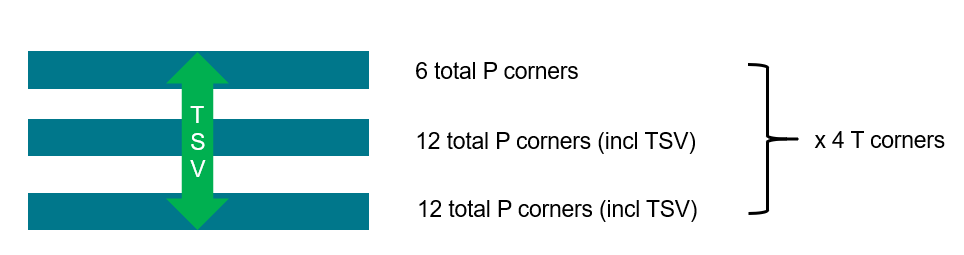

因为 3D 设计允许每个 Die 可以有独自的 PVT corner,这样 STA 签核就必须涵盖所有的可能出现的组合情况。以上图里三个 Die 的典型设计为例,如果 Die1 和 Die2 的 process corner 都是 12 个,Die3 是 6 个;三个 Die 的 Voltage corner 和 Temperature corner 都只考虑 2 个相同的,那么总共需要分析的 corner 数量就已经达到(12x12x6)x 2 x 2 = 3456 个。

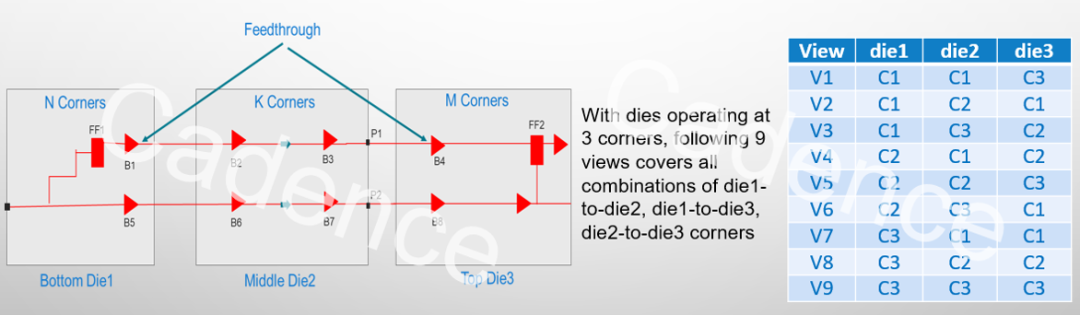

针对这个 3D 设计中 corner 爆炸式增长的挑战,Tempus 开发了一个新的 Rapid Automated Inter-Die(RAID)技术,可以在分析这些 feed through paths 时巧妙地大量缩减 corner 数量,同时保证计算精度。下图是一个非常简化的 3 层 Die 的例子,假设每层都只有 3 个 corner(N=K=M=3),那么全组合需要分析的 corner 数量就是 27 个(N*K*M)。Feed through 的部分通过 represent delay 和 adjustment 替换,K 最大就可以 reduce 到 1,这样在这个 case 里 corner 就减小到了 9 个,corner 的缩减率是 3X。对于中间 Die 超过 10 个 corner 的设计,reduction ratio 将会超过 10X;对于更多层堆叠的 3D 设计,缩减率就更为可观!

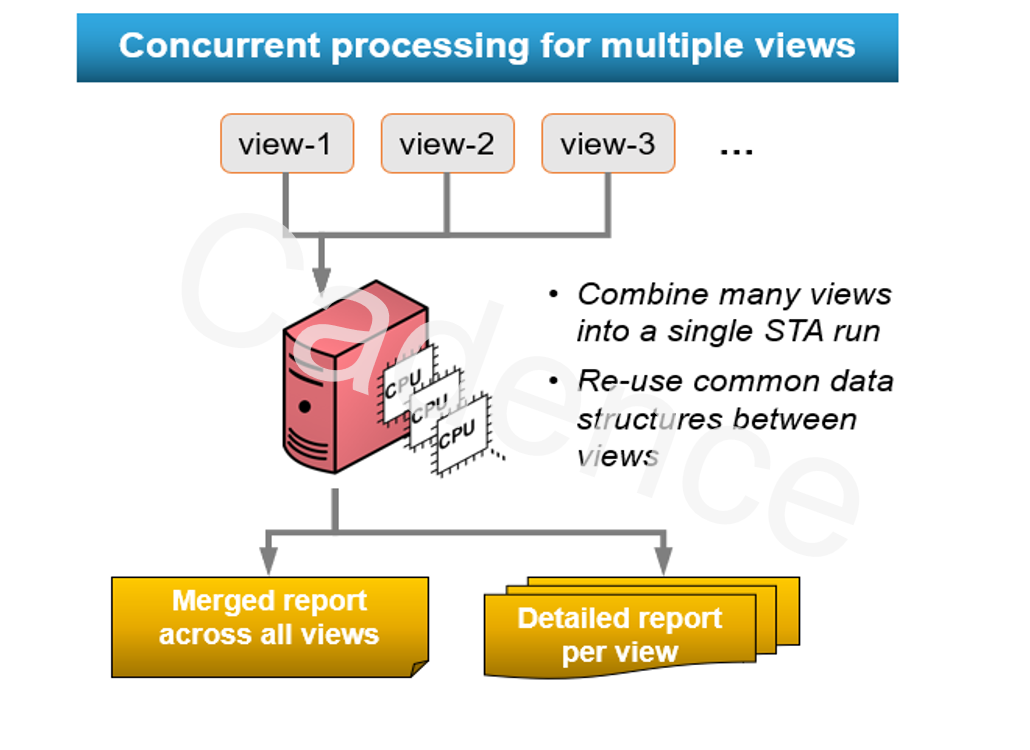

对于没有 feed through 的一般 path 分析,corner 增长的数量不会如此庞大,但是仍然会对机器的需求量随着设计的复杂度增加不断攀升。Cadence 另一现有的强大并行分析引擎 concurrent multi-mode multi-corner(C-MMMC)就为此提供了第二个维度的解决方案。该功能通过高效复用多个 corner 的相同的 DB 数据,储存有效减轻计算量的中间数据和提高 CPU 的并行使用率,从而大幅降低了对机器和硬盘的使用需求。对于相同 delay corner 不同 constraint corner的 STA 分析,运行时间和内存使用的增加量都只有 20% 左右,相对于串行分析 CMMMC 的 runtime reduction 通常可以达到 4-5X。

05设计案例

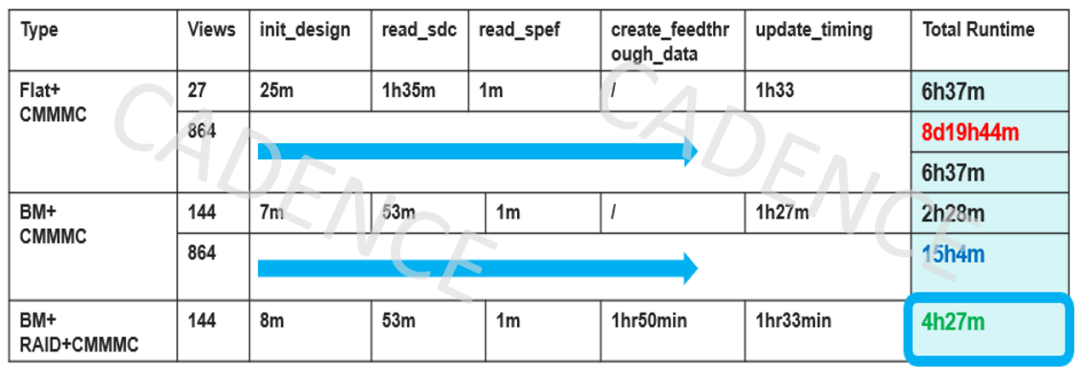

最后让我们看一个 5nm 的实际 3D 设计案例,该设计包含一个 logic die 有 6 个 process corner,和 2 个 SRAM 的 die 分别有 12 个 process corner。如果使用传统的 STA 分析,即使是在 CMMMC 模式下完成所有 864(6*12*12)个 process corner 的组合分析也需要 8-9 天(多线程使用 32 个 CPU,@2.6GHZ 主频)。使用 Boundary Model 技术之后时间可以极大缩短至 15 个小时;继续使用 RAID 技术之后,签核 corner 的个数降低至 144 个,完成相同的时序分析仅仅使用了惊人的 4 小时 27 分钟!加上产生 Boundary Model 所需要的最长时间(6 小时 50 分钟),速度提升仍然接近 40X!

Cadence Integrity 3D-IC 平台是业界首个全面的整体 3D-IC 设计规划,实现和分析平台。该平台以全系统的视角,集成了 Cadence 公司的多个强势分析工具和优化引擎,对芯片的性能、功耗、散热和面积做了全面的评估和优化。其中寄生参数提取工具 Quantus 准确计算 3D 通孔和中阶层之间的电阻电容效应;静态时序分析工具 Tempus 极大地提高了多工艺组合 STA 分析的效率,把之前需要以周记的分析速度减少以小时计算。强大准确的算力为高带宽高数据吞吐量的机器学习、高性能存储设备、云端计算等 3D-IC 应用保驾护航。

如您需了解更多这部分的内容,请点击“阅读原文”注册申请我们的 Integrity 3D-IC 资料包:

- Cadence Integrity 3D-IC 平台产品手册

- Cadence 3D-IC Extraction & STA Solutions PPT 介绍

注册成功且通过 Cadence 审核的用户可获得完整版 PPT 资料。

注:审核通过后 Cadence 会将 PPT 发送至您的邮箱,提供您的公司邮箱地址通过审核的几率更大哦!

Cadence Integrity 3D-IC 平台提供了一个高效的解决方案,用于部署 3D 设计和分析流程,以实现强大的硅堆叠设计。该平台是 Cadence 数字和签核产品组合的一部分,支持 Cadence 公司的智能系统设计战略(Intelligent System Design),旨在实现系统驱动的卓越 SoC 芯片设计。

关于 Cadence

Cadence 在计算软件领域拥有超过 30 年的专业经验,是电子系统设计产业的关键领导者。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计从概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续八年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站 cadence.com。

2022 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

-

芯片

+关注

关注

458文章

51386浏览量

428432 -

Cadence

+关注

关注

65文章

932浏览量

142580 -

TSV

+关注

关注

4文章

115浏览量

81593

原文标题:3D-IC 设计之寄生抽取和静态时序分析

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TSV工艺流程与电学特性研究

请问有TSV6390AIDT和/或TSV6290AIDT的SPICE型号吗?

硅通孔(TSV)电镀

通用输入/输出轨到轨低功耗操作放大器TSV321/TSV358/TSV324/TSV321A/TSV358A/TSV324A

微(60µ一)宽的带宽(2.4 MHz)的CMOS运算放大器TSV6390/TSV6390A/TSV6391/TSV6391A

高功因数(1.15兆赫为45微米)cmos运算放大器TSV521/TSV522/TSV524/TSV521A/TSV522A/TSV524A

轨到轨输入/输出60µ880千赫5V CMOS运算放大器TSV630/TSV630A/TSV631/TSV631A

轨到轨输入/输出,29µ,420 kHz的CMOS运算放大器TSV62x,TSV62xA

轨到轨输入/输出29µ420 kHz的CMOS运算放大器TSV620,TSV620A,TSV621,TSV621A

寄生电感怎么产生的_寄生电感产生原因是什么

什么是TSV封装?TSV封装有哪些应用领域?

抽取式摘要方法中如何合理设置抽取单元?

TSV阵列建模流程详细说明

什么是硅或TSV通路?使用TSV的应用和优势

uBUMP和TSV的寄生如何抽取

uBUMP和TSV的寄生如何抽取

评论