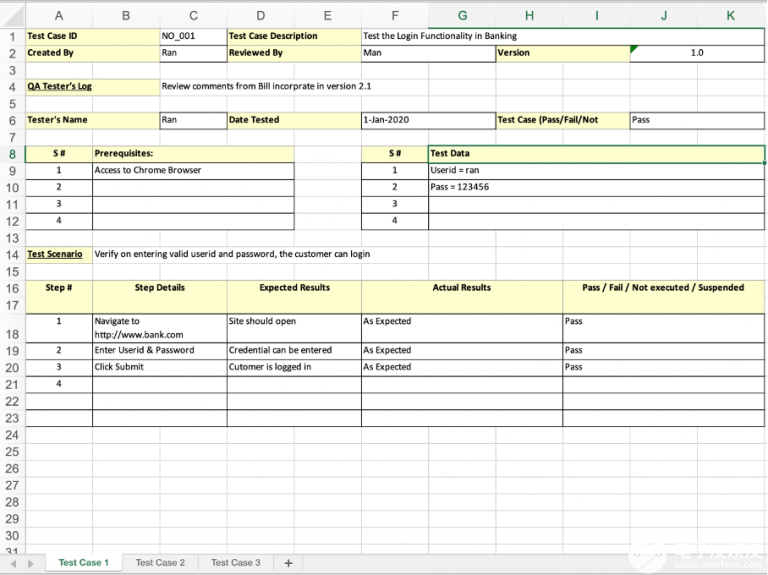

在设计仿真用例时,有限制条件的激励相比漫无目的的仿真更加有效的找出RTL的bug。因此,同一份测试方案,不同的sequence往往代表着不同的test_case。真正的测试用例都是基于base_test派生的一个类。

第一,在这么多不同的case下,我们可以设置一个base_case,base_case将环境env,cfg等一些东西包进去;

第二,需要几个不同的sequence就写几个sequence,sequence之间没有联系,继承于uvm_sequence;

第三,在每个具体的执行case下,可以用asserte插入具体的配置参数,并且每个case设置自己独立的default_sequence;

第四,在终端指定不同的case_name跑不同的case;

文件:src/base_test.svclass base_test extends uvm_test;my_envenv;functionnew(stringname="base_test",uvm_componentparent=null);super.new(name,parent);endfunction externvirtualfunctionvoidbuild_phase(uvm_phasephase);externvirtualfunctionvoidreport_phase(uvm_phasephase);`uvm_component_utils(base_test) //使用uvm_component_utils宏来注册到factory中endclass //在build_phase中实例化my_env,并设置sequencer的default_sequence来启动my_sequencefunctionvoidbase_test::build_phase(uvm_phasephase);super.build_phase(phase);env=my_env::create("env",this);uvm_config_db#(uvm_object_wrapper)::set(this,"env.i_agt.sqr.main_phase","default_sequence",my_sequence::get());endfunction//根据UVM_ERROR的数量来打印不同的信息,一些日志分析工具functionvoidbase_test::report_phase(uvm_phasephase);uvm_report_serverserver;interr_num;super.report_phase(phase);server=get_report_server();err_num=server.get_severity_count(UVM_ERROR);if(err_num!=0)begin$display("TESTCASEFAILED");endelsebegin$display("TESTCASEPASSED");endendfunction

代码中的super.new(name,parent)是继承基类的构造函数的写法,包括下面的 super.build_phase(phase)也是继承基类的表现。

除了上述操作外,还通常在base_test中做如下事情:

第一,设置整个验证平台的超时退出时间;

第二,通过config_db设置验证平台中某些参数的值。这些根据不同的验证平台及不同的公司而不同,没有统一的答案

下面介绍基于上面定义的basetest如何来构造测试用例呢

首先构造用例case0的激励sequence

然后基于base case构造自己的case来启动自己的激励sequence

文件:src/my_case0.sv class case0_sequence extends uvm_sequence #(my_transaction); my_transaction m_trans; …virtual task body();if(starting_phase != null)starting_phase.raise_objection(this);//启动仿真repeat (10) begin `uvm_do(m_trans)//发送此transaction。 end #100; if(starting_phase != null) starting_phase.drop_objection(this);//仿真结束 endtask … endclass class my_case0 extends base_test; function new(string name = "my_case0", uvm_component parent = null); super.new(name,parent); endfunction extern virtual function void build_phase(uvm_phase phase); `uvm_component_utils(my_case0) endclass //通过设置默认sequence来启动case0_sequence function void my_case0::build_phase(uvm_phase phase); super.build_phase(phase);uvm_config_db#(uvm_object_wrapper)::set(this,"env.i_agt.sqr.main_phase","default_sequence",case0_sequence::get());endfunction

UVM会利用UVM_TEST_NAME从命令行中寻找测试用例的名字,创建它的实例并运行

… +UVM_TEST_NAME=my_case0

-

FPGA

+关注

关注

1635文章

21837浏览量

608326 -

仿真

+关注

关注

50文章

4155浏览量

134479 -

终端

+关注

关注

1文章

1169浏览量

30198

原文标题:仿真验证之base test

文章出处:【微信号:FPGA学姐,微信公众号:FPGA学姐】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于pCTL的循环优化测试用例自动生成方法

如何编写测试用例

修改自测试用例run_test遇到的问题求解

基于跨平台系统中测试用例复用的解决方法

基于DSEA的弱变异测试用例集生成方法

测试用例的管理 介绍测试用例的几种管理方法

用例篇 | 单元测试用例复用到集成测试?Testlet Library来助力!(上)

基于base test如何来构造测试用例

基于base test如何来构造测试用例

评论