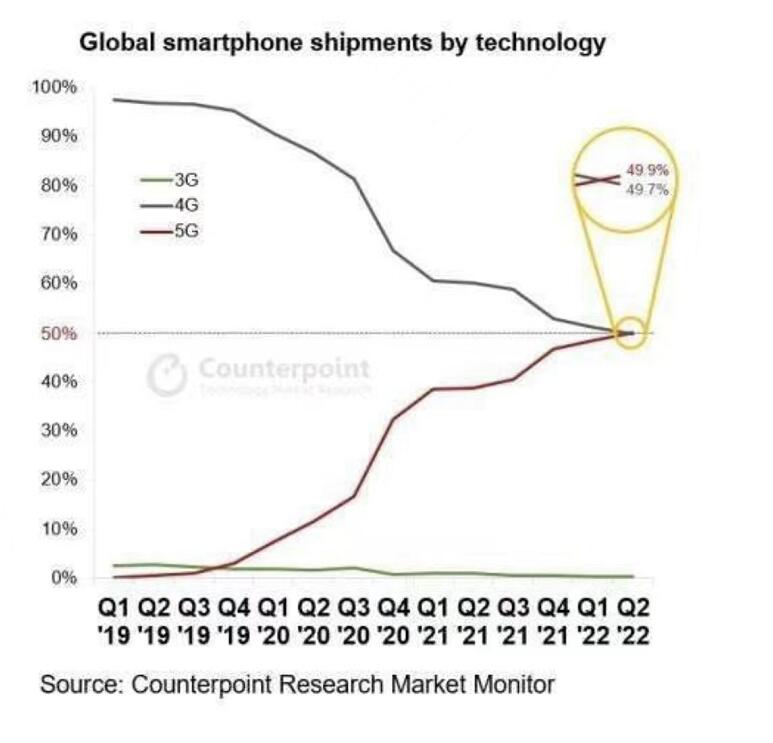

5G手机SoC芯片领域,苹果自研A15芯片,高通骁龙芯片,联发科天玑系列芯片,海思麒麟芯片都是市场的主要参与者。台积电作为全球最大晶圆代工厂,在先进制程领域对于手机SoC的支持也是相当到位。

台积电(中国)有限公司技术总监陈敏表示,台积的5纳米已经量产超过3年,累计出货超过200万片,产品广泛应用在大家的智能手机、AI,还有HPC的产品。台积电的3纳米产品研发进展非常顺利,将在今年下半年实现量产,而2纳米产品的量产预计会在2025年实现。

陈敏说:“5纳米的家族,台积电将提供了N4、N4P和N4X,这是5纳米的新成员,通过新成员的增加使得客户在5纳米家族的产品可以获得更好的PPA的表现。TSMC 3D Fabric先进封装技术涵盖 2.5D 和垂直芯片堆叠产,是台积电过去10年以来对于3D IC的不断完善和开发。客户采用台积3D Fabric所生产的产品取得的整个系统效能的提升,都有非常良好的表现。”

就3D Fabric在HPC上、手机上的应用发展。台积电技术人员表示,wafer level 3D封装并非在基板上实现,而是通过制造手段实现。这是Chiplet的典型方案,当芯片过于大时,需要将其切割成小芯片。台积电的SoIC是由三颗Chiplet的小方案组成的。

3D Fabric 在HPC中的应用 HPC的高性能运算主要指网络产品、网络通讯产品、CPU、GPU以及使用AI的芯片产品,都属于HPC的范畴。

这其中会用到一些比较大的芯片。正常芯片最大尺寸是800平方毫米,但GPU和AI芯片需要无限增大时,需要切割。 在HPC中,台积电会用到3D Chip Stacking。这种流程包括两种方式,一种方式是 Chip on wafer,就是将切割后的Chip直接放在晶圆上;另一种方式是wafer on wafer,就是直接将晶圆和晶圆对接。

台积电的3D封装分为三个类型:一,如果是高密度的互连。芯片需要和基板相连则会使用silicon imterposer,直接使用晶圆作为中介层,进行高密度的连接。二,如果两个Die之间并非高密度互连,可能使用CoWoS-R或者InFo-2D的RDL。三、CoWoS-L处于以上两种情况中间,在Die和Die之间高密度互联区域中存在一个Local silicon。

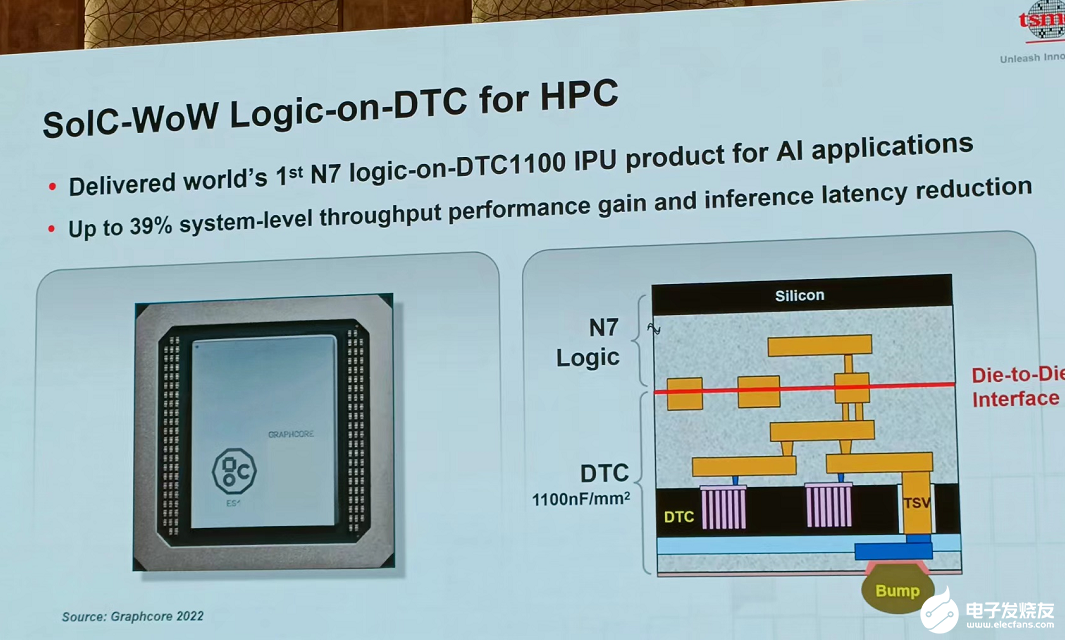

在逻辑制程上,台积电2022年已经达到3nm节点。 SoIC-CoW可以做到Top Die和Bondom Die达到7nm,bondingpitch达到9个micron,未来的技术指标将做到5nm和5nm的堆叠,6 micron的尺寸。 SoIC-WoW,达到7nm、0.13DTC。AMD发布的EPYC Processor中,将最占面积的缓存进行了3层的堆叠。 其他的封装方案还有,CoWoS和InFo。 CoWoS方案上,台积电推出了三种方式,CoWoS-S、CoWoS-R、CoWoS-L。CoWoS-S是CoWoS中台积电能够提供的最成熟技术。

3D Fabric的制造及生态链进展

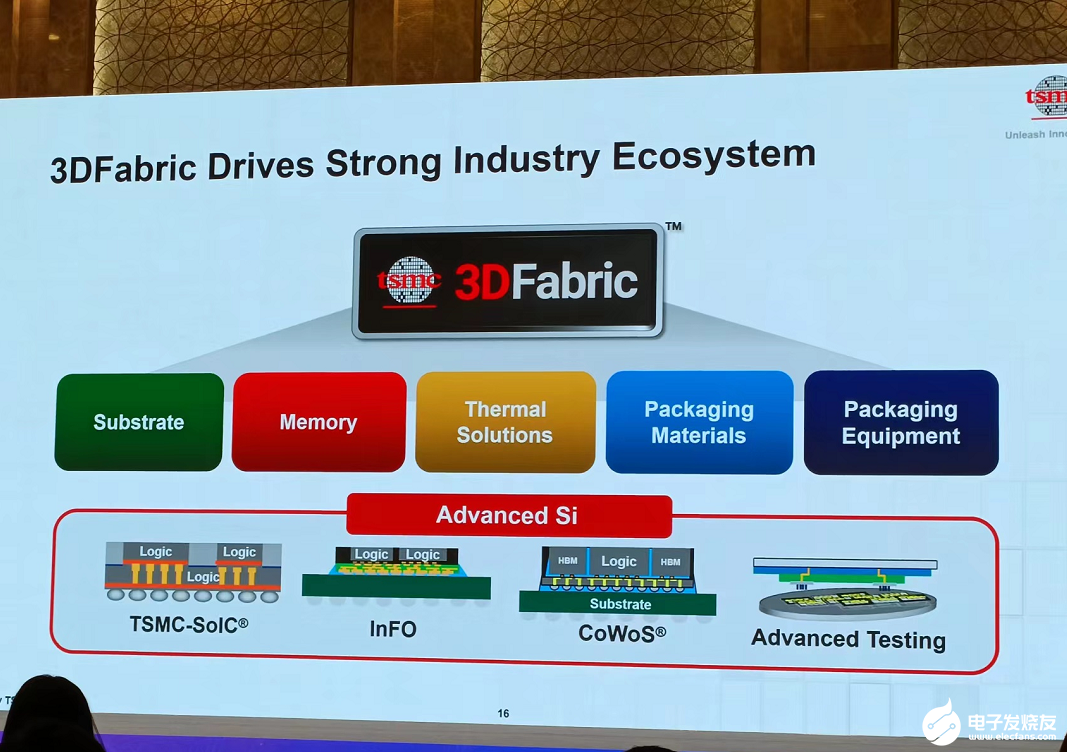

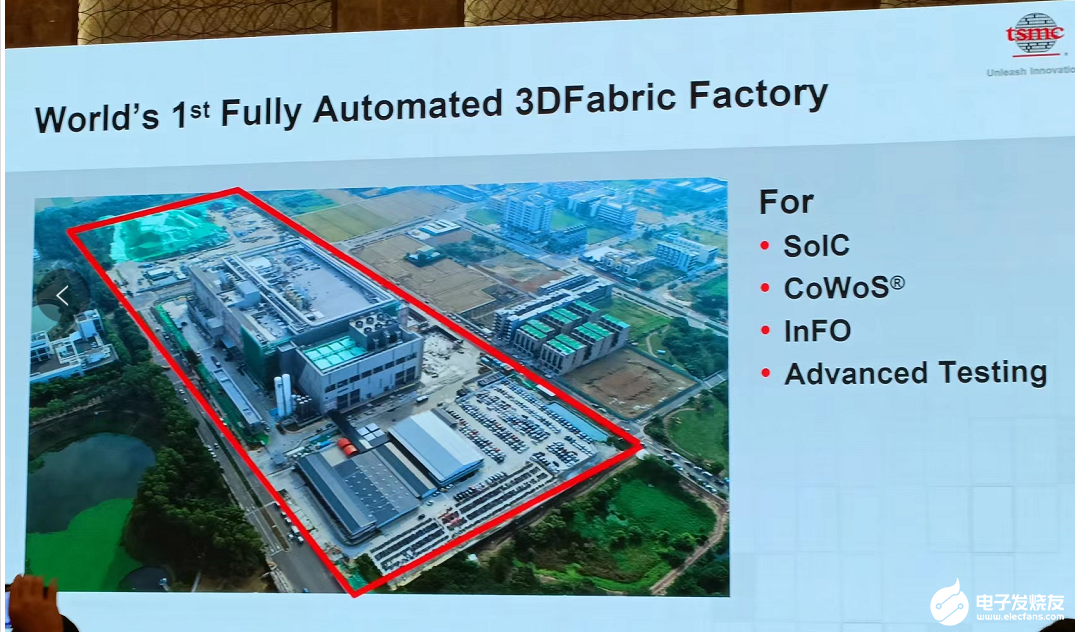

目前,台积电已经建成了全球第一个全自动化3D Fabric工厂,可以提供:SoIC、CoWoS、InFO、先进测试的服务。

台积电技术人员表示,3D Fabric仍然面临着很大挑战,对此台积电也在努力推动工业的生态链建设,包括基板、存储、散热、封装材料、设备的合作协同。

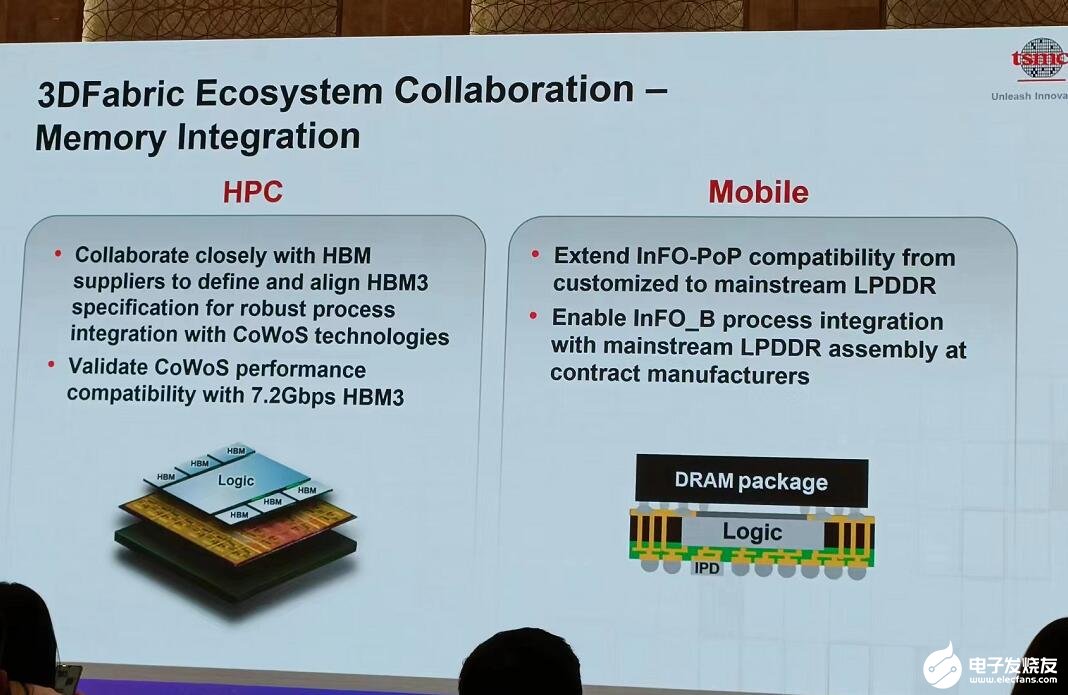

基板的尺寸大多停留在70*70mm的尺寸,但随着芯片的逐渐增大,需要的基板尺寸也更大。如何驱动基板厂商与台积电一起进一步改进,是其中一个问题。 在HPC方面,台积电将与HBM供应商密切合作,定义和调整HBM3规范,以实现与CoWoS技术的强大工艺集成。在手机领域,将InFo-POP兼容性从定制扩展到主流LPDDR,实现InFO-B工艺与LPDDR组件的集成。 3D Fabric将释放下一代创新力量。

本文由电子发烧友原创,转载请注明以上来源。微信号zy1052625525。需入群交流,请添加微信elecfans999,投稿爆料采访需求,请发邮箱zhangying@elecfans.com。

-

台积电

+关注

关注

44文章

5719浏览量

167900 -

HPC

+关注

关注

0文章

331浏览量

24002 -

5G手机

+关注

关注

7文章

1356浏览量

51477

发布评论请先 登录

相关推荐

5G手机全球出货量首次超过4G手机 台积电3D Fabric技术如何助力手机和HPC芯片

5G手机全球出货量首次超过4G手机 台积电3D Fabric技术如何助力手机和HPC芯片

评论