随着FPGA的功能越来越强大,并且有SOC等异构的架构不断演进,硬件设计也有更多的时钟要求,例如:

A. PCIe 系统要求HSTL 100Mhz的时钟;

B. DDR有推荐时钟,7系列上常用200Mhz 差分时钟;UltraScale和UltraScale Plus上常用300Mhz时钟;

C. Zynq或者Zynq UltraScale,PS常用33.3333Mhz1.8V单端时钟;

D. UltraScale接USB的话,常用26Mhz LVDS时钟,SATA需要125Mhz或者150Mhz时钟;

E. 收发器的频率比较多,125Mhz、156.25Mhz、161.1328Mhz,148.5Mhz等等;

F. FPGA的PL有时候备一个SYSCLK,50Mhz,100Mhz或者200Mhz都比较常见,作为系统工作时钟,有单端的,也有用差分的;

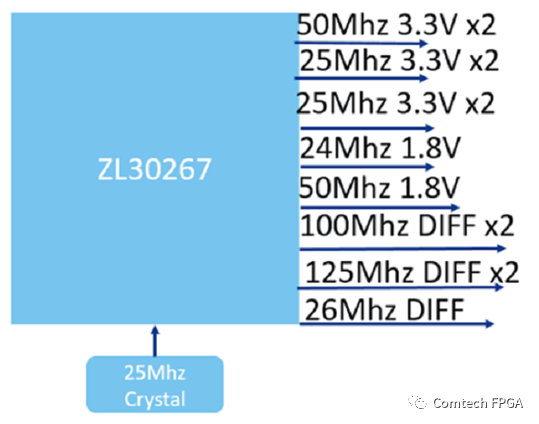

一个板子下来,3-6种时钟需求常见,不同的频率,不同的电平标准。硬件工程师做设计,不同板卡,各种设计混合在一块,库房有10多种晶振,时钟驱动芯片,时钟PLL芯片,琳琅满目。针对FPGA的设计,Microchip有一块芯片,ZL30265/7,单芯片解决方案。

ZL30265/7概要介绍

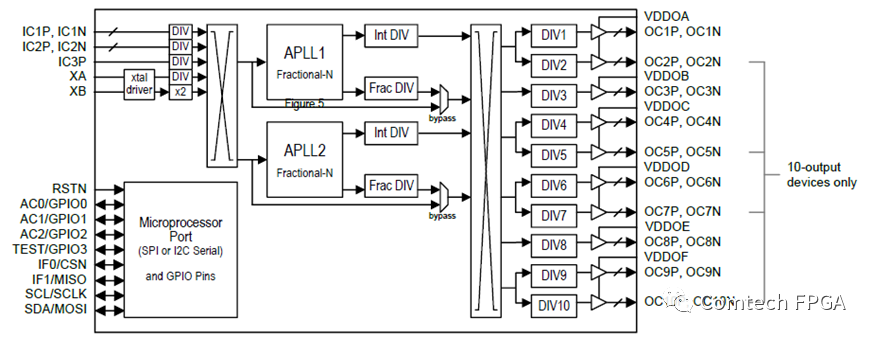

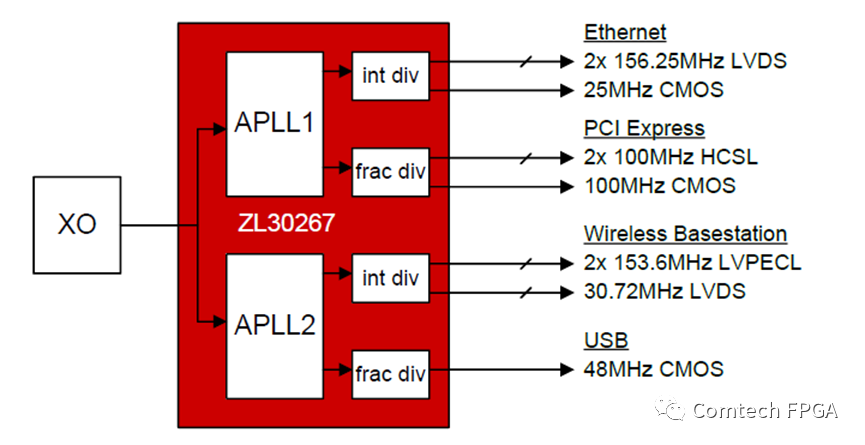

ZL30265/7内部配置有任意倍数的乘法器以及两个同时具有分数和整数能力的模拟锁相环,可以生成4个独立的频率系列,进一步的可以输出多达6路或10路的任意频点任意输出类型的超低抖动的时钟信号。ZL30265/7在输入仅为一颗晶体的情况下,依靠其出色的性能,创建了完整的时钟树,替换了多个晶体晶振和外围时序简化了设计,降低了BOM成本,节省了PCB空间,并提高了设计的可靠性。

ZL30265/7的特性

A. 内置两个具有分数分频和整数分频功能的APLL,构成四个独立的频率族;

B. 四路输入时钟可以灵活配置,分别是:一个晶体/CMOS、两个差分/CMOS、一个单端/CMOS;

C. 输入频率可以是9.72MHz至1.25GHz中的任意值(CMOS最大300MHz);

D. 每个APLL的四个输入(IC1,IC2,IC3,XA)均有一个输入监视器,当检测到输入出现异常时,支持自动或手动切换至其他输入;切换方式包括GPIO Pin、寄存器、输入监视器;

E. 6路任意频率、任意格式的输出,输出频率为1Hz至1045MHz中的任意值;

F. 整数乘法器和除法器的输出抖动低至0.17ps RMS(12kHz-20MHz);

G. 分数分频器的输出抖动典型标称值<1ps RMS,实际应用中大多数情况<0.5ps RMS;

H. 每个输出都有一个独立的分频器,并且每个输出均可配置为LVDS、LVPECL、HCSL、2xCMOS或HSTL;

I. 在2xCMOS模式下,P和N可以输出不同的频率(例如125MHz和25MHz),CMOS输出电压可调,范围是 1.5V至3.3V;

J. 各路时钟输出可以进行精确校准,并且输出相位可调整;

K. 各路时钟输出可以独立的启用或者禁用,并且支持glitch-less启动和停止;

L. ZL30265/7内部集成有EEPROM,可以存储8组配置,上电时可以选择其中一组自动配置;

N. 扩频调制模式;

O. 生成符合PCIe 1、2、3、4、5的时钟;

Q. 核心电源电压有多种选项:仅2.5V、仅3.3V、1.8V+2.5V或1.8V+3.3V;

R. 封装为8x8mm QFN56(0.5mm间距),节省PCB空间;

ZL30265/7的配置方式

ZL30265/7内部集成有EEPROM,可以存储8组不同的配置。EEPROM写入配置数据后,每次RST时将会根据GPIO自动加载一组配置数据;

写EEPROM时的硬件连接:TEST=1,AC[2:0]=000, IF[1:0]=11

通讯方式:SPI

烧写器:standard industry SPI EEPROMprogrammers,购买途径也很方便,在淘宝就能买到,不到百元;

烧写软件:Microchip提供免费的GUI,可以按需求进行配置,生成EEPROM IMAGE,然后用烧写器烧录;

案例集锦一:

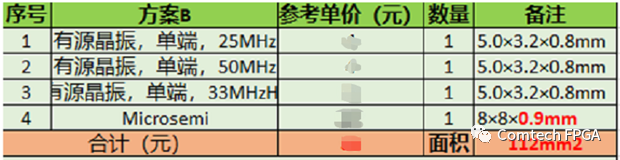

某客户的产品最初用分立时钟方案(方案A),后来用Microchip的ZL30267(方案B)进行了优化,并进行了对比,得出两个结论:

A. 方案B的BOM成本比方案A低大约30%;并且物料种类减少,方便采购备货;

B. 方案B的PCB占用面积是方案A的一半;

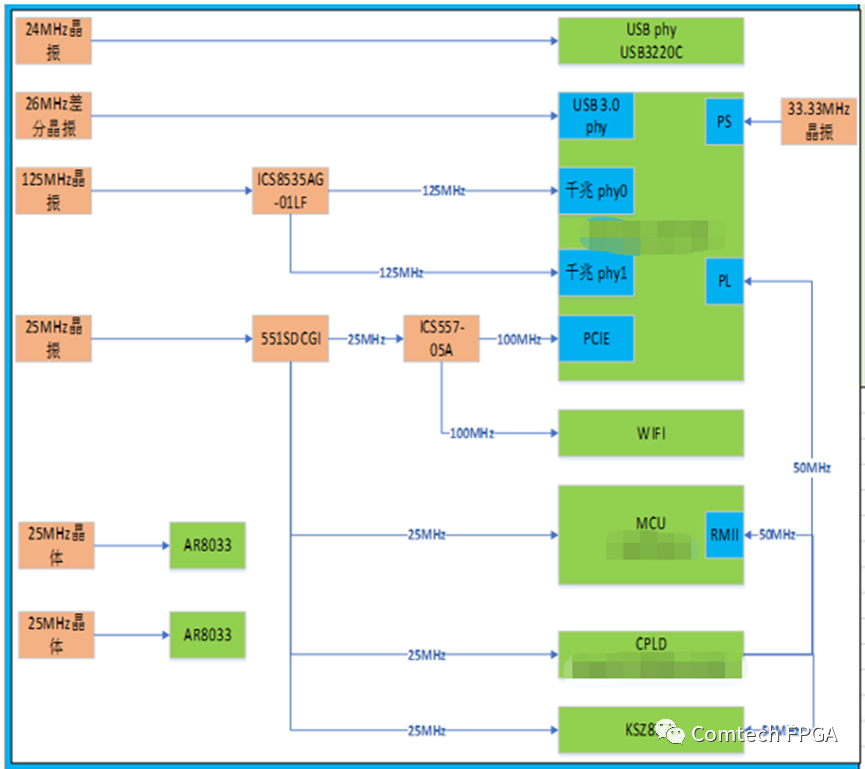

时钟树框图如下:

案例集锦二

结语:

ZL30265/7隶属于ZL3026x产品家族,其家族成员具有相同的封装、相同的Pin脚定义,在当前缺芯的大环境下,能带给您更多的选择空间。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21736浏览量

603248 -

microchip

+关注

关注

52文章

1506浏览量

117575 -

Xilinx

+关注

关注

71文章

2167浏览量

121384 -

时钟芯片

+关注

关注

2文章

249浏览量

39883

原文标题:一种适配Xilinx FPGA的时钟芯片--Microchip ZL30265/7

文章出处:【微信号:Comtech FPGA,微信公众号:Comtech FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ZL30265/7概要介绍、特性及配置方式

ZL30265/7概要介绍、特性及配置方式

评论