在硬件设计过程中,当原理图设计完成后需要提交EDA团队进行PCB的绘制,其中传输线阻抗的控制是重要的一项内容。在提交PCB设计说明书时,需要对线宽/线间距做出要求;在PCB设计过程中,需要与EDA设计人员进行沟通,可能会对线宽/线间距、相邻层厚度做适当调整;在提交PCB制版后,厂家会结合实际生产条件进行阻抗调整,这也需要硬件开发人员进行确认。因此,作为硬件开发人员,需要对传输线阻抗的原理和计算方法有所了解。传输线阻抗控制主要有两种:单端阻抗和差分阻抗。单端阻抗的阻值一般控制在50欧姆左右,差分阻抗一般控制在100欧姆左右。接下来介绍传输线特征阻抗的等效模型,并结合具体单板PCB设计,介绍如何利用Polar Si9000工具进行特征阻抗的计算。

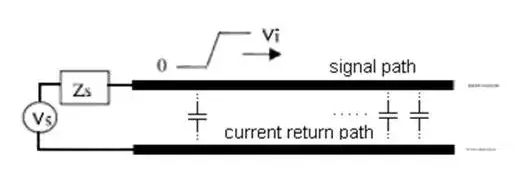

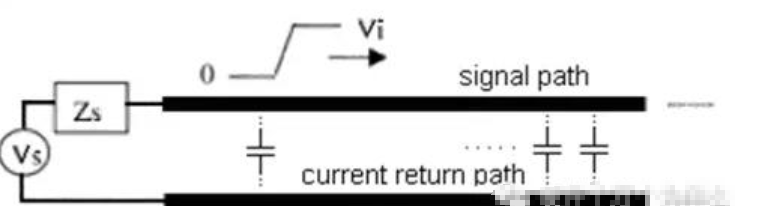

一、传输线的等效模型

1. 等效模型及参数

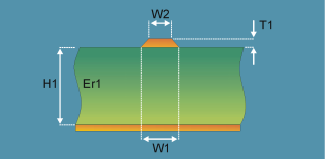

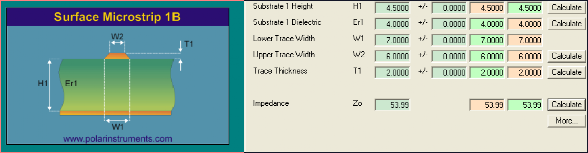

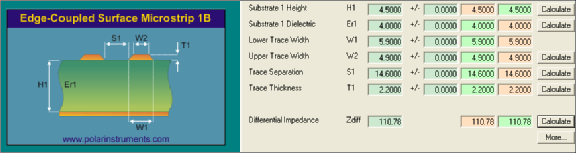

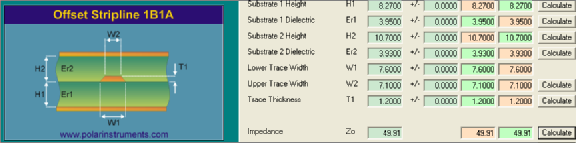

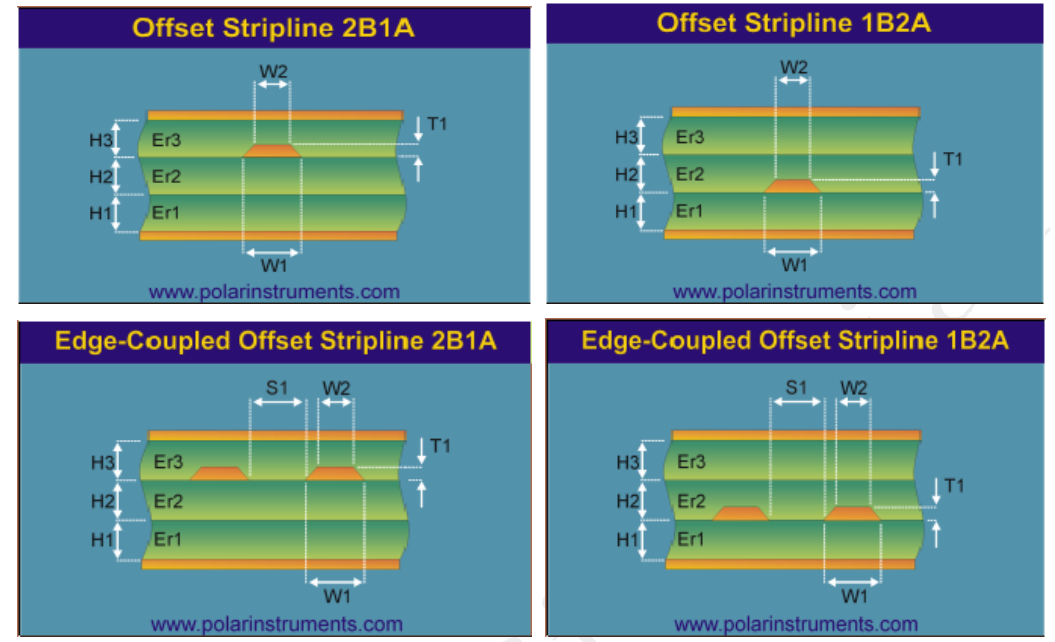

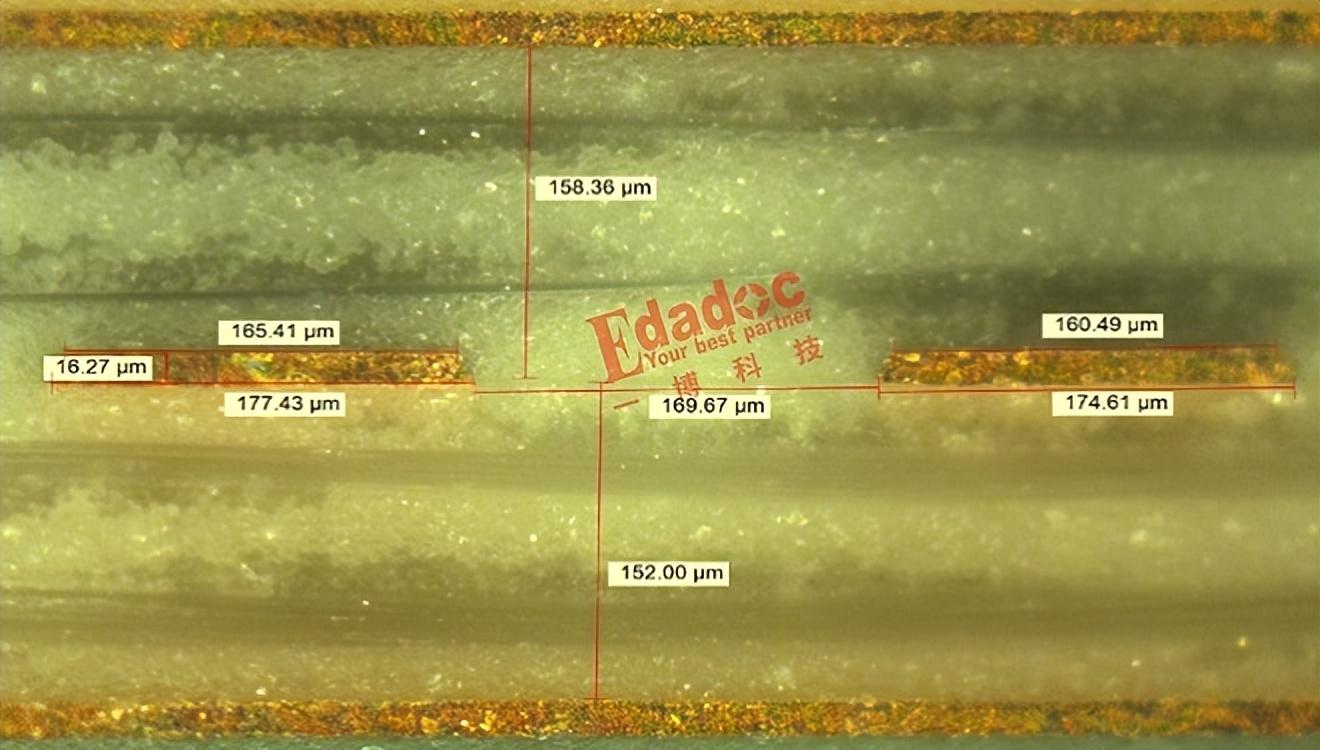

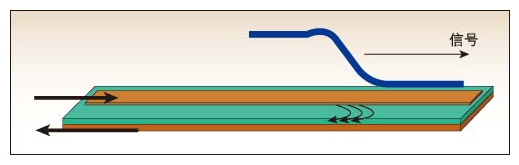

图1:传输线等效模型传输线等效模型如图1示,其中各参数如下:1、铜层厚度(T1)2、PCB板迹线的上下线宽(W2,W1)3、绝缘层厚度(H1)4、介电常数(Er1)5、若为差分线,则还有一个参数线间距(S1)。

图1:传输线等效模型传输线等效模型如图1示,其中各参数如下:1、铜层厚度(T1)2、PCB板迹线的上下线宽(W2,W1)3、绝缘层厚度(H1)4、介电常数(Er1)5、若为差分线,则还有一个参数线间距(S1)。2.参数说明

特征阻抗主要与线宽,绝缘层厚度等参数有关。线宽越大,特征阻抗越小;绝缘层越厚,相应的特征阻抗越大。阻抗控制采用以下参数:介质常数(Er1):4.0,FR4材料。下线宽(W1):设计线宽(假设为W);上线宽(W2):外层走线=W-1; 内层走线=W-0.5;铜层厚度(T1):分为表层与内层,如下表。需电镀填铜层铜厚(表层):| 电镀填铜层基铜铜厚(OZ) | 1/3 OZ | 1/2OZ | 1 OZ |

| 计算铜厚(mil) | 1.7 | 2.0 | 2.7 |

| 非电镀填铜层铜厚(OZ) | 1/2OZ | 1 OZ | 1.5OZ |

| 计算铜厚(mil) | 0.6 | 1.2 | 2.56 |

二、具体计算实例:

计算所使用的PCB模型为某低速业务板工装测试背板,有18层,其结构如下:表1:| L1 | --------------------------------------- | 0.5oz +电镀 |

| PP 2116 4.495mil | ||

| L2 | 1oz | |

| CORE 0.21 8.27mil | ||

| L3 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L4 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L5 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L6 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L7 | --------------------------------------- | 1oz |

| PP 1080+7628 9.82mil | ||

| L8 | --------------------------------------- | 1oz |

| CORE 0.15 5.9mil | ||

| L9 | --------------------------------------- | 1oz |

| PP 3313 3.42mil | ||

| CORE 1(0.5oz) 37.99mil | ||

| PP 3313 3.37mil | ||

| L10 | --------------------------------------- | 1oz |

| CORE 0.15 5.9mil | ||

| L11 | --------------------------------------- | 1oz |

| PP 1080+7628 9.8325mil | ||

| L12 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L13 | --------------------------------------- | 1oz |

| PP 1080+7628 9.4575mil | ||

| L14 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L15 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L16 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L17 | --------------------------------------- | 1oz |

| PP 2116 4.495mil | ||

| L18 | ---------------------------------------- | 0.5oz+电镀 |

| 阻抗计算值 | ||||||

| 层别 | 调整线宽/线间距 | 计算值(ohm) | H1(mil) | Er1 | H2(mil) | Er2 |

| L1/18 | 7.6 mil to 7 mil | 49.6 | 4.5 | 3.95 | ||

| L1/18 | 7/13.5 mil to 5.9/14.6 mil | 98.3 | 4.5 | 3.95 | ||

| L3/16/5/14 | 7.6 mil | 49.6 | 8.27 | 3.95 | 10.7 | 3.93 |

| L3/16/5/14 | 7/13.5 mil | 98.1 | 8.27 | 3.95 | 10.7 | 3.93 |

| L7/12 | 7.6 mil | 50 | 8.27 | 3.95 | 11.07 | 3.93 |

| L7/12 | 7/13.5 mil | 98.7 | 8.27 | 3.95 | 11.07 | 3.93 |

| L9/10 | 7.6 mil to 8 mil | 51.5 | 5.9 | 3.65 | 53.18 | 3.89 |

| L9/10 | 7/13.5 mil | 99.1 | 5.9 | 3.65 | 53.18 | 3.89 |

| L9的屏蔽层为: | L8/L11 | |||||

| L10的屏蔽层为: | L8/L11 | |||||

| 其他层邻层屏蔽 | ||||||

2.1 表层(L1/L18)单端阻抗计算:(单位:mil)

参数说明:H1为绝缘层的厚度4.5mil;W1= 7.0mil;W2= W1-1=6.0mil;T1=2. 0 mil;Er1=4;计算结果:Z0=53.99欧姆。加工后的实际阻抗应为:Z0′=Z0-3=50.99欧姆与厂家所给出的阻抗值基本一致。

参数说明:H1为绝缘层的厚度4.5mil;W1= 7.0mil;W2= W1-1=6.0mil;T1=2. 0 mil;Er1=4;计算结果:Z0=53.99欧姆。加工后的实际阻抗应为:Z0′=Z0-3=50.99欧姆与厂家所给出的阻抗值基本一致。2.2表层(L1/L18)差分线阻抗计算:(单位:mil)

参数说明:H1为绝缘层的厚度4.5mil;W1= 5.9mil;W2=4.9mil;S1= 14.6 mil;T1=2.2mil;Er1=4;计算结果:Z0=110.78欧姆。加工后的实际阻抗应为:Z0′=Z0-9=101.78欧姆与厂家所给出的阻抗值基本一致。

参数说明:H1为绝缘层的厚度4.5mil;W1= 5.9mil;W2=4.9mil;S1= 14.6 mil;T1=2.2mil;Er1=4;计算结果:Z0=110.78欧姆。加工后的实际阻抗应为:Z0′=Z0-9=101.78欧姆与厂家所给出的阻抗值基本一致。2.3内层(L3/L10)单端阻抗计算:(单位:mil)

以L3层为例,参数设置如下: 参数说明:H1为绝缘层厚度8.27mil。Er1为3.95;W1=7.6 mil;W2= W1-0.5=7.1mil;T1=1.2mil;Er2 =3.93;H2为芯板的厚度加上铜箔的厚度为10.7mil计算结果:Z0=49.91欧姆。与厂家所给出的阻抗值基本一致。

参数说明:H1为绝缘层厚度8.27mil。Er1为3.95;W1=7.6 mil;W2= W1-0.5=7.1mil;T1=1.2mil;Er2 =3.93;H2为芯板的厚度加上铜箔的厚度为10.7mil计算结果:Z0=49.91欧姆。与厂家所给出的阻抗值基本一致。2.4内层差分线(L3/L10)阻抗计算: (单位:mil)

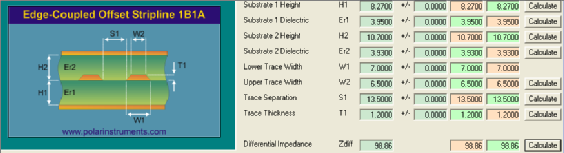

以L3层为例,参数设置如下: 参数说明:H1为绝缘层的厚度8.27mil。Er1为3.95;W1 =7 mil;W2= W1-0.5=6.5mil;S1 =13.5 mil;T1=1.2mil;Er2 =3.93;H2为绝缘层的厚度加上铜箔的厚度,为10.7mil计算结果:Z0=98.86欧姆。与厂家所给出的阻抗值基本一致。

参数说明:H1为绝缘层的厚度8.27mil。Er1为3.95;W1 =7 mil;W2= W1-0.5=6.5mil;S1 =13.5 mil;T1=1.2mil;Er2 =3.93;H2为绝缘层的厚度加上铜箔的厚度,为10.7mil计算结果:Z0=98.86欧姆。与厂家所给出的阻抗值基本一致。2.5 相邻信号层的阻抗计算

理论上相邻信号层的阻抗计算应该用如下模型,如第9第10两层。但是这样非常繁琐,可以简化成2.3,2.4中所述的模型,实际厂家给出的参数也证明了这一点。只要将H1,H2,Er1 ,Er1作相应调整即可,具体参数见表1,表2中所示。

三、总结

本文介绍了传输线特征阻抗的等效模型,并结合具体单板PCB设计,介绍了利用Polar Si9000工具计算特征阻抗的方法,希望能对大家有所帮助。审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

阻抗

+关注

关注

17文章

956浏览量

45910 -

PCB设计

+关注

关注

394文章

4680浏览量

85515 -

传输线

+关注

关注

0文章

376浏览量

24020

原文标题:【PCB设计】传输线特征阻抗的计算方法及实例

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

阻抗对信号传输的影响 阻抗测量仪器的选择

对信号传输的影响主要体现在以下几个方面: 信号反射 :如果信号源的输出阻抗和传输线的输入阻抗不匹配,就可能会发生信号反射,使得信号无法完全进入传输线

平衡传输线标准的重要性

对于需要长距离通信的系统。本文将探讨平衡传输线标准的重要性。 一、平衡传输线标准的必要性 1. 提高信号完整性 在长距离传输中,信号完整性是一个关键问题。不平衡传输线容易受到电磁干扰(

为什么选择hdmi光纤传输线

HDMI光纤传输线,也称为光纤HDMI线或HDMI光纤线,是一种通过光纤传输高清视频和音频信号的设备。它采用了光纤技术,具有以下主要优势: 高传输

输入阻抗、输出阻抗、阻抗匹配到底是个啥?

在原信号上将会改变原信号的形状。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射。为什么阻抗不匹配时会产生反射以及

发表于 06-01 08:08

掌握了这个分析方法,实现传输线阻抗5%的加工公差不是梦!

高速先生成员--黄刚

传输线阻抗控制对系统性能的重要性不言而喻,每一家的PCB加工板厂都在往能控制更严格的阻抗公差这个目标而不断努力。但是我们也知道,传输线

发表于 03-25 18:05

掌握了这个分析方法,实现传输线阻抗5%的加工公差不是梦!

传输线结构很多因素都会影响阻抗,例如线宽、介质厚度、介电常数、铜厚等,那大家有没有想过到底哪个因素最影响阻抗呢?学会了本文的分析方法,或许有一天阻抗加工公差控制到5%也很可能哦!

信号传输使用传输电缆的电路原理

不同电平不同速率的信号传输。请问有关信号线传输理论在哪本书里,与电磁波和电磁场的联系大不大?在应用中主要是利用了传输线的那些优点,传输线材质

发表于 01-30 13:59

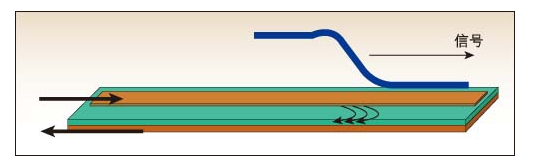

PCB的传输线结构

传输线的定义是有信号回流的信号线(由两条一定长度导线组成,一条是信号传播路径,另一条是信号返回路径。),很常见的传输线也就是我们PCB板上的走线。

发表于 01-15 15:13

•381次阅读

如何解决PCB设计总是有阻抗不连续?

如果传输线是各向同性的,那么只要信号在传输,就始终存在一个电流 I,而如果信号的输出电压为 V,在信号传输过程中,传输线就会等效成一个电阻,

发表于 01-09 16:15

•320次阅读

高速PCB设计基础知识:传输线

传输线的定义是有信号回流的信号线(由两条一定长度导线组成,一条是信号传播路径,另一条是信号返回路径。),常见的传输线也就是我们PCB板上的走线。

发表于 01-02 15:36

•396次阅读

传输线特征阻抗的等效模型

传输线特征阻抗的等效模型

评论