2020 年7 月14 日,半导体标准化组织JEDEC(JointElectron Device Engineering Council)发布了JESD79-5 DDR5 SDRAM 标准,带来许多关键性性能强化。随英特尔近期正式发布第12 代Core 处理器(代号Alder Lake),意味2021 年是DDR5 存储器启航元年。下载链接:《内存技术:内存测试和测量挑战》

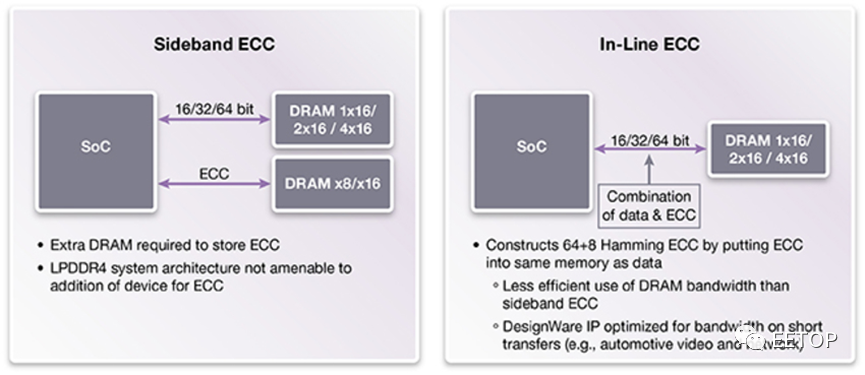

此文尽量设法排除高深莫测的DRAM相关技术名词,让各位迅速了解DDR5相对DDR4的优势与可能的影响,最后再同场加映英特尔Atom x6000系列引进的「In-Band ECC」技术,让大家瞧瞧英特尔如何在没有ECC模组下提供类似纠错功能。

「理所当然」的提升数据传输率

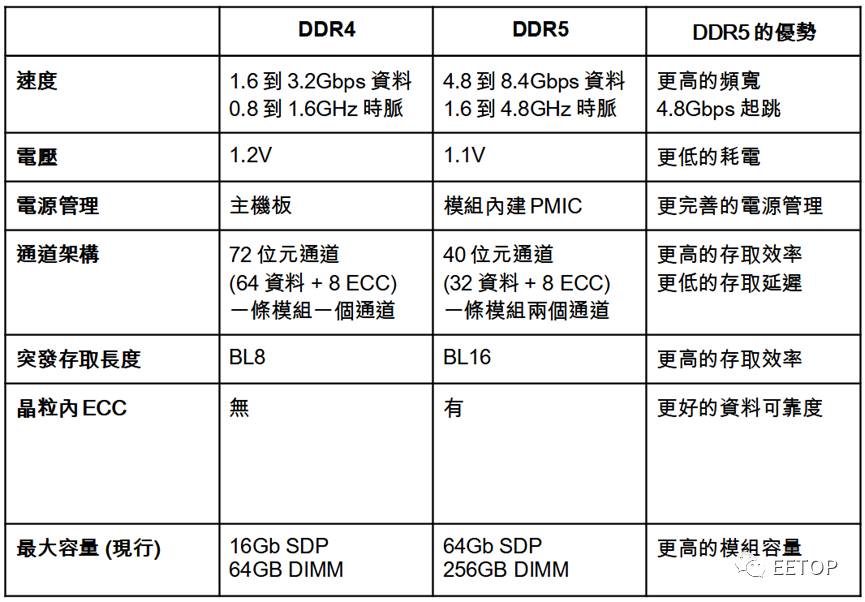

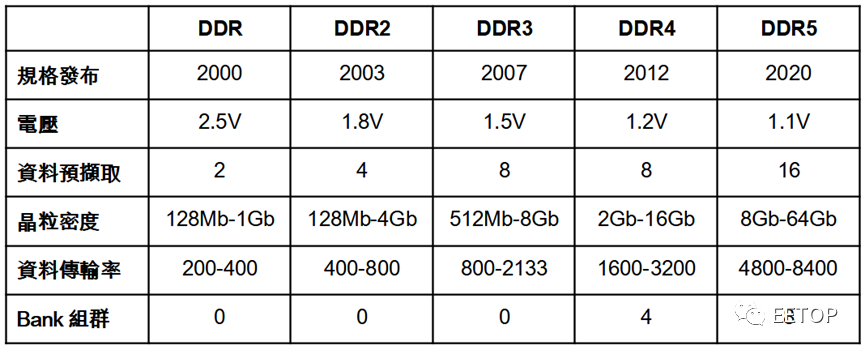

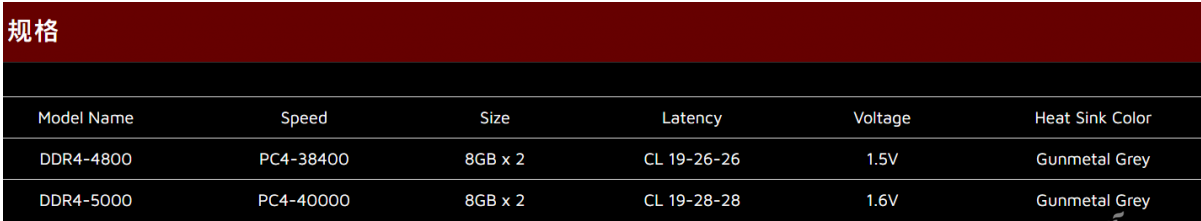

初期DDR5可提供超过DDR4 50%数据传输率,最终预期可达2.6倍8.4Gbps。回顾JEDEC SDRAM历代演进,提升幅度还算惊人,但到头来也只是充分反应相隔八年累积的制程技术成长。

至于「一定会膨胀」的容量看似没什么好提,但后面会提到DDR5强化数据可靠性的手段。

更低电压与崭新电源架构

持续降低工作电压也是历代JEDEC SDRAM的传统,从20年前DDR2.5V一路调降到DDR5 1.1V,让存储器运作「理论上」更节能省电。

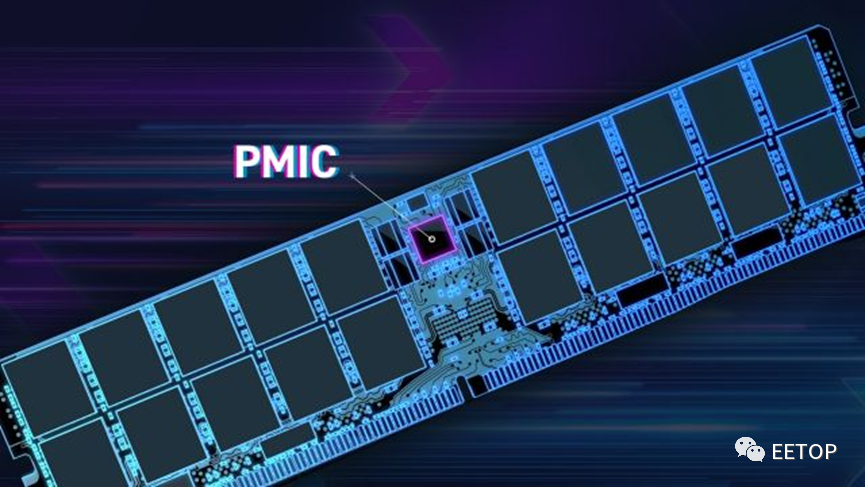

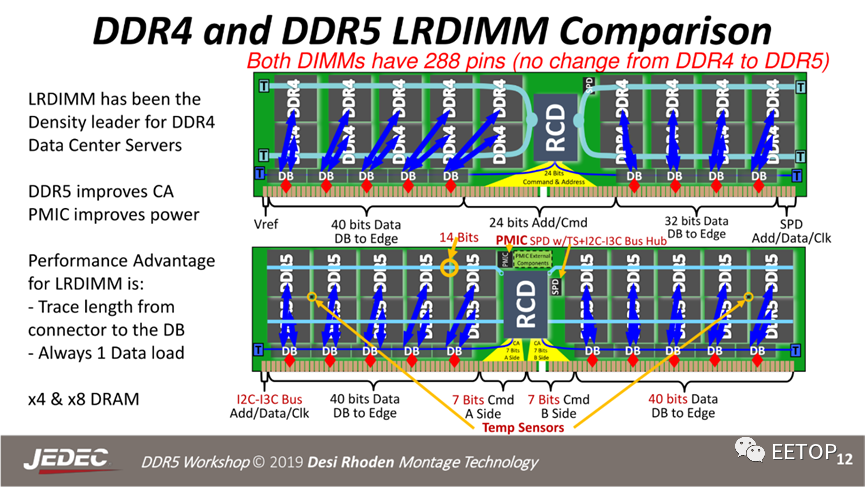

但当DDR5基础工作电压降到1.1V时,意味更小信号容限,所以过去由主机板负责的电源管理功能,就转移到存储器模组本身,因此DDR5会多一颗PMIC,直接控制存储器电源,提供更佳信号辨识能力。

不过多了这颗PMIC也就抬高了成本,都将转嫁给制造商成本和消费者帐单,以及更高的缺料风险。

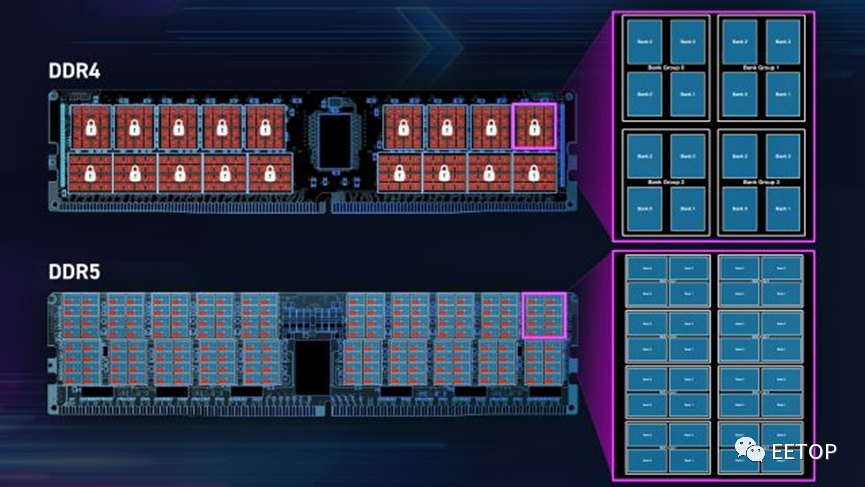

两倍的Bank群组、通道架构与突发存取长度

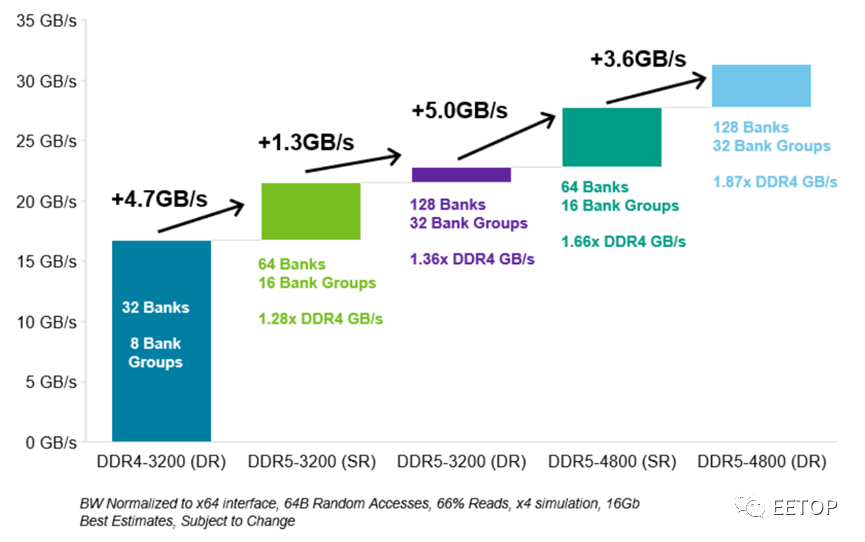

Bank意指DRAM颗粒可单独运作的储存单元。DDR5采用八个Bank群组而成的32Bank,是DDR4两倍。DRAM因储存原理是需定时刷新(Refresh)数据的电容,DDR4与前代刷新时无法执行其他操作,但DDR5可透过Same Bank Refresh (REFsb)命令,允许系统刷新某些Bank时,可存取其他Bank的数据。

换言之,DDR5存取可用性起码是DDR4两倍。

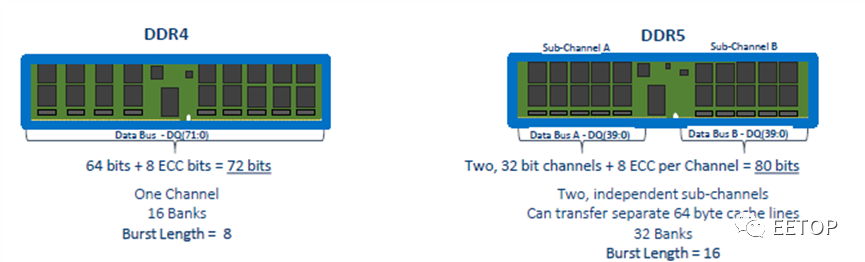

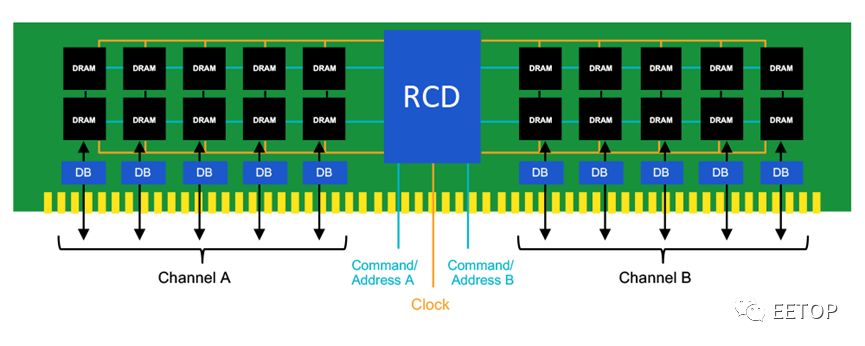

DDR5另一个规格面重大变化(也许是最重要者),在于将双通道实作于单模组。过去DDR都是72位元(64位元数据+8位元ECC),但DDR5变成两组40位元(32位元数据+8位元ECC)。两个较小独立通道可提高存储器存取效率,特别是缩短存取延迟。分而治之的结构,也可便于提高信号完整性。

看起来似乎好棒?但对服务器会用到的ECC模组就不是这样了,因拆成两边都需要完整ECC,会增加额外颗粒数量,例如原本18个颗粒的ECC模组就可能变成20颗,意味更高成本。

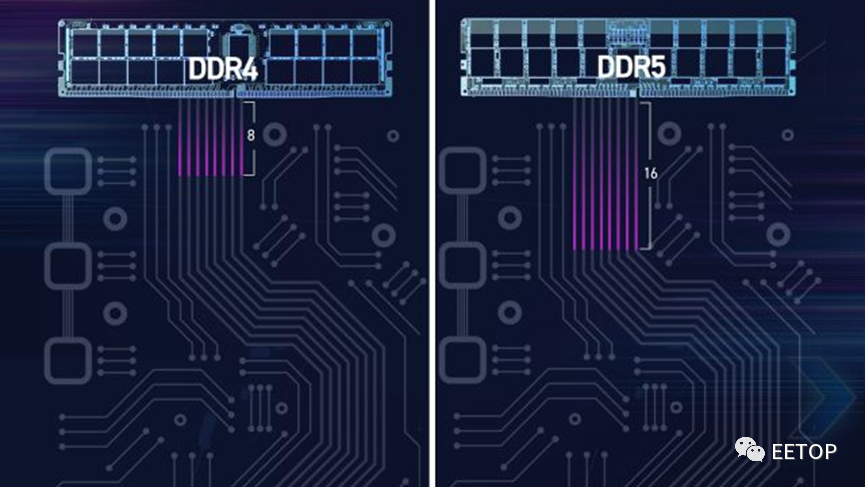

再来就是跟以上双通道结构息息相关的突发存取长度(Burst Length)了,这数字决定单一读写指令可存取的数据量。DDR5的BL从DDR4八倍增到16,这对时下的主流处理器是个「魔术数字」。为何?DDR5的双通道结构让单次数据存取宽度变成32位元(4 Byte),BL16就代表「可一次填充处理器的64 Byte快取存储器区块」。

换句话说,一条DDR5模组可同时满足两个64 Byte快取区块的需求,是DDR4两倍。

更高的存储器有效带宽比例

一般来说,JEDECSDRAM的存储器有效带宽比例,多半是约定俗成的80%(理论和实际毕竟有差距),但DDR5结合这么多架构改进,按某些存储器模组厂商估算,这次有机会达85%~90%,很接近Rambus水准(号称90%以上)。搞了这么多年,JEDEC SDRAM「总算」看到Rambus的车尾灯,值得大书特书一下。

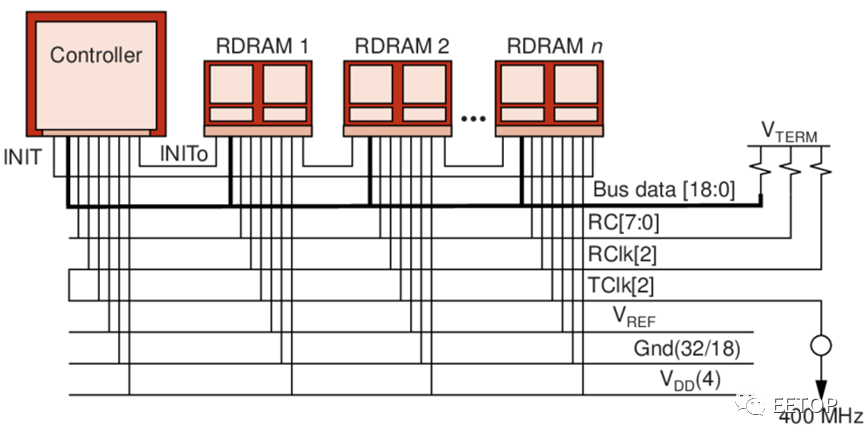

笔者不得不先谈谈Rambus这个英特尔芯片组发展史的黑历史了。Rambus发展出一系列所谓「Protocol-Based DRAM」将传统总线的定址、控制与数据,都包在类似网络封包的Packet内,然后DRAM内部整合大多数控制单元功能,每颗DRAM如同一个网络装置,连接一条超高速序列(Serial)总线。也因此,Rambus DRAM不能有空存储器模组,未使用存储器模组须安装「假的」CRIMM(Continuity RIMM)当终端。

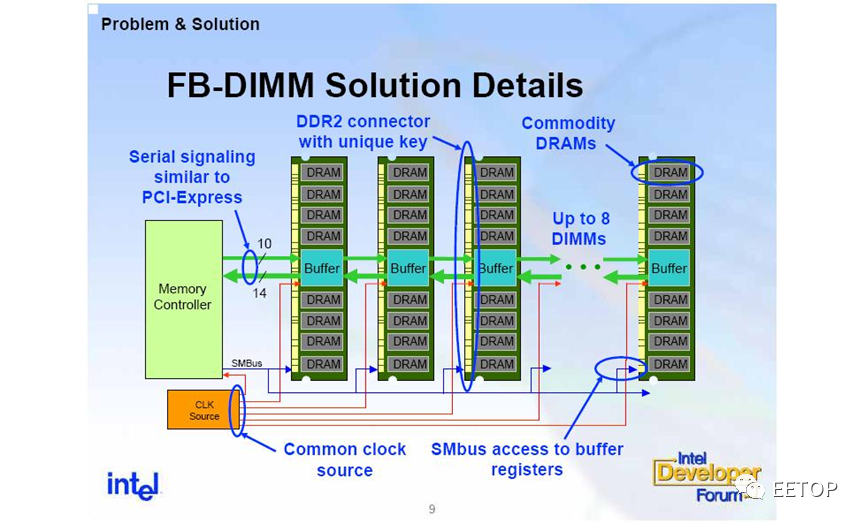

Protocol-Based DRAM可用更少数据线就达成更高存储器频宽,也会有更高存储器有效带宽。Rambus的缺点也很明显,更长存取延迟、高昂制造成本、更高发热量,以及Rambus恶名昭彰的授权费。与PC133 SDRAM相比,同容量Rambus价格多达2~3倍。日后FB-DIMM(Fully-Buffered DIMM)也继承类似Rambus的精神,终究难逃相同的命运。

更高的数据可靠度

以电容为储存原理的DRAM,颗粒容量及储存密度成长,背后藏着诸多潜在风险,如像构成地球低强度背景辐射的带电粒子,引起位元翻转的存储器软错误(Soft Error),这也成为潜在安全攻击目标。这也是为何高效能非挥发性存储器一直视为迟早取代DRAM的主因之一(虽然迟迟没有发生)。

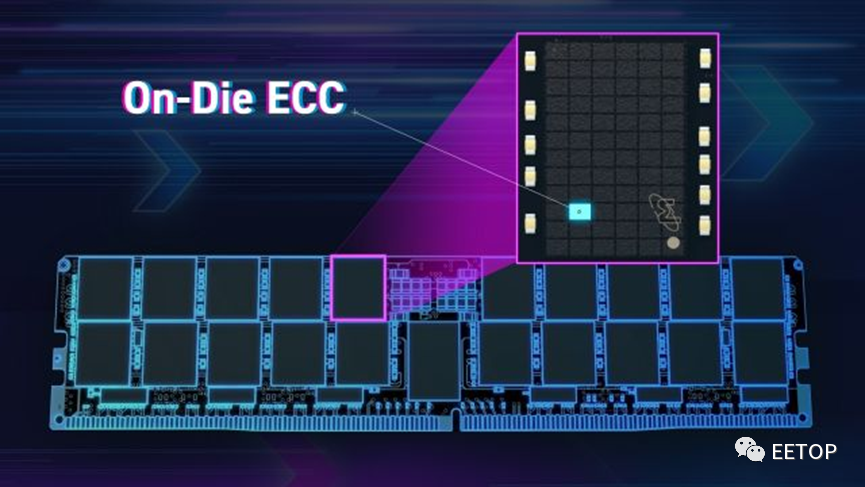

为了强化稳定性,DDR5支持晶粒内建纠错(On-DieECC)机制,每128位元数据就附带8位元纠错码。不过笔者并不认为这能取代标准ECC模组,只能说确保容量更大的DDR5颗粒可维持和过去同等级的数据可靠度。

这会增加多少潜在颗粒成本,只有原厂自己心知肚明。总之谈钱伤感情,就干脆不谈了。

同场加映:英特尔Atom x6000系列的In-Band ECC

既然全文提到这么多次ECC,笔者就同场加映谈谈英特尔新一代Atom x6000处理器(代号Elkhart Lake)导入的In-Band ECC(或称In-Line ECC)技术,不需要ECC存储器模组也能达到相似数据可靠度。

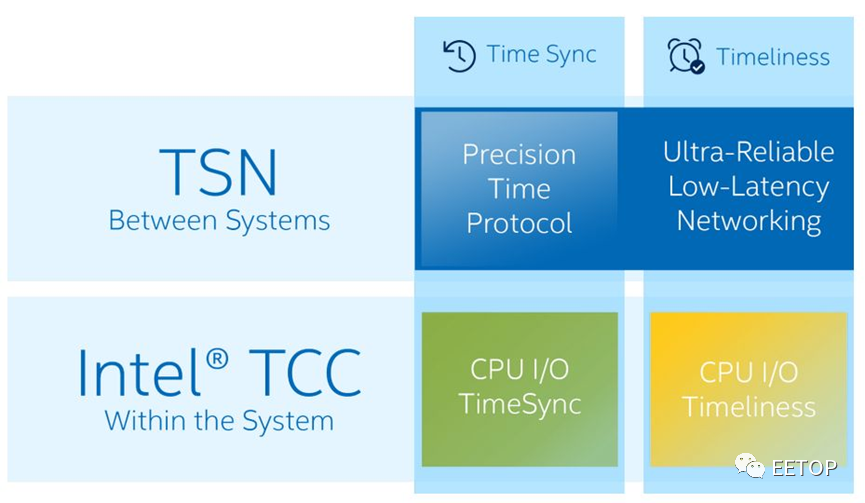

针对工业自动化的相关应用,英特尔Atom x6000系列补强不少新功能,如工业级时间敏感网络(TimeSensitive Networking,TSN)和时间协调运算(Time Coordinated Computing,TCC),安全性和管理性也丝毫不含糊。基本上,论针对特定生态系统的解决方案完整度,也是现阶段AMD依旧不及英特尔的先天弱点。

说穿了,In-BandECC藉由DRAM内分割一块特定区域,存放存储器数据的ECC码。以Atom x6000为例,每64 Byte数据分配到2 Byte ECC,存储器容量预留1/32放置后者。处理器存储器控制也势必多出相关后继处理步骤。

但天底下没有免费的午餐,In-Band ECC固然达成「低成本的高可靠度」,但前提是牺牲存储器的读写性能。照英特尔官方说法,启动In-Band ECC后,存储器读取效能剧降至原本一半,存储器写入更下探到三分之一。话说回来,这对工业物联网应用,或许的确是值得的代价。

最后,终于是升级存储器的好时机了吗?

秉持勤俭持家的原则,笔者死守DDR3多年,连现在用的主机板都刻意选支持DDR3的华硕Z170M-3 D3,死撑活撑,直到最近微软Windows 11判了确定无法升级的死刑。看在迟早得面对现实升级整台桌机的份上,看到DDR5明显演化,说不想直奔DDR5绝对是骗人的。

但时下世界正处于史上前所未见的「万物缺料」,什么都涨,DDR5价格何时才能降到可负担的水准,笔者实在毫无乐观的理由,只能继续看硬件测试网站的效能测试数据过过干瘾了。

审核编辑 :李倩

-

半导体

+关注

关注

334文章

27359浏览量

218593 -

DRAM

+关注

关注

40文章

2314浏览量

183477 -

DDR

+关注

关注

11文章

712浏览量

65332 -

DDR5

+关注

关注

1文章

422浏览量

24145

原文标题:谈谈关于DDR5技术规格的那些事

文章出处:【微信号:AI_Architect,微信公众号:智能计算芯世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DDR3/4都还没玩够,DDR5已经来啦

DDR4已经OUT Cadence宣布DDR5全新进展

5G时代你是等DDR5上市 还是升级DDR4内存

[译] 尽管DDR5快来了,DDR4还是取得新进展

DDR5内存和DDR4有啥不同

专门为内存颗粒测试设计的DDR4/DDR5 Interposr测试板

DDR4和DDR5规格之间的差异

ddr5的主板可以用ddr4内存吗 几代CPU才能上DDR5

0706线下活动 I DDR4/DDR5内存技术高速信号专题设计技术交流活动

了解DDR5相对DDR4的优势与可能的影响

了解DDR5相对DDR4的优势与可能的影响

评论