相对芯片大规模量产来说,前期的流片所需费用也不可小觑,尤其是对于不少Fabless公司来说,从第一版设计到定型,往往需要经历多次流片,从MPW、Full Mask到量产。设计失误或代工厂失误导致流片失败更是最让设计团队头疼的一件事,之所以每次流片验证是如此让人提心吊胆的过程,不仅是因为设计过程中付出的心血,还有流片所需的金钱与时间成本。

流片花费的时间

对于精力和产能都有限的这些晶圆代工厂来说,他们并不是随时都能帮助客户流片的,所以他们的MPW计划往往都有排期。首先,厂商要想找晶圆代工厂或第三方服务公司询问、预留并下达订单。排上之后提交自己的GDS数据,然后等待其他“拼车人”提交数据后再进入流片过程,最终等待芯片送到自己的手中。从设计提交截止到拿到芯片,可能需要半年以上的时间,这就是时间成本。

以三星为例,三星的12英寸和8英寸晶圆厂都有开展MPW服务,其中12英寸目前最高公开提供5LPE这一5nm的工艺。一般来说,越是先进的工艺,往往每年的MPW流片次数就越少,比如台积电的CyberShuttle可能今年就只提供一次3nm的MPW服务。如何缩短这些MPW项目的周转时间,其实也是晶圆代工厂需要考虑的问题之一。

三星MPW Shuttle 服务 / Samsung Foundry

然后就是流片的金钱成本了,以为光掩膜版的费用对于前期数量不多的试验片来说还是太贵了,所以不少厂商都选择了MPW这种共享光掩膜版的服务,定型后再走Full Mask。当然了,在MPW服务商,每家晶圆代工厂给出的定价其实并没有那么固定,而且不少先进工艺的定价也都是保密的,有的还需要签订NDA保密协议。所以我们一般只能通过第三方MPW服务公司提供的部分定价来获取公开信息。

几家晶圆厂的流片费用

格芯虽然没有参与到先进工艺的竞争中来,但无疑也是全球最大的几家晶圆代工厂之一了。格芯也与不少IC服务平台达成了合作,为不同地区提供MPW服务,所以他们的定价还算是比较公开的。以加拿大的CMC Microsystems给出的数据为例,格芯的12nm工艺12LP的定价为51525美元/mm2。还有一点需要注意的是,即便同为45nm工艺节点,但如果选择特种工艺,比如高压、硅光或射频等等,流片费用也还要再高一截的。

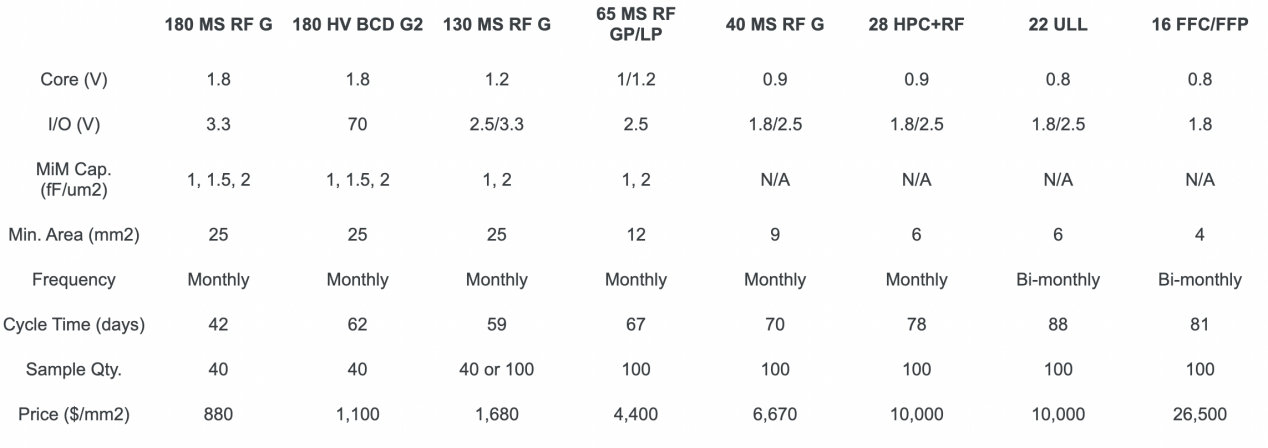

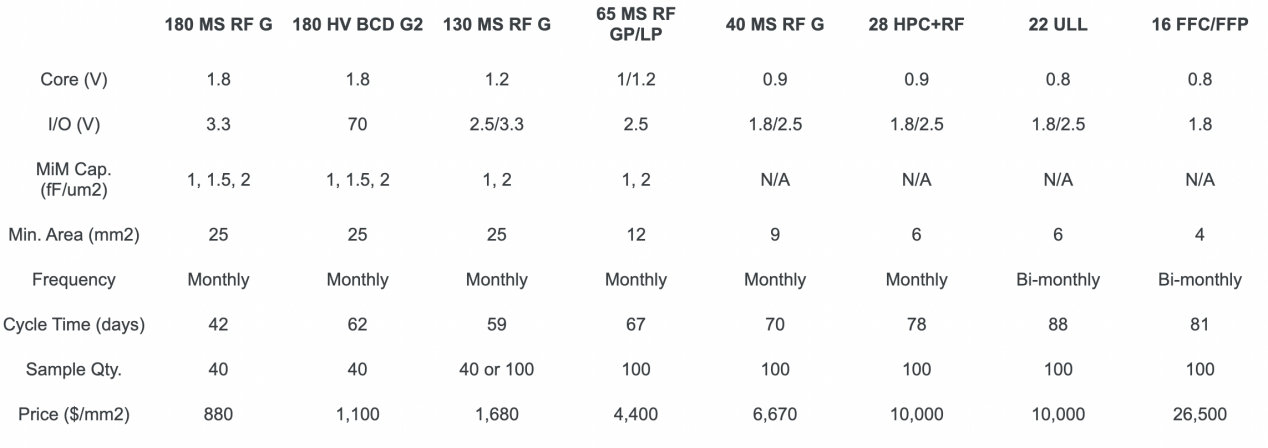

台积电部分工艺的MPW费用 / MUSE Semiconductor

在CMC提供的台积电MPW服务中,最先进的工艺为28nm的28 HPC+RF节点,定价为16850美元/mm2。而专供台积电MPW服务的MUSE Semiconductor,却最高可以提供16nm的16 FFC/FFP工艺节点,定价为26500美元/mm2。但该工艺下支持Full Block流片,有4mm2的最小面积要求,且频率为两月开展一次。

作为国内的龙头企业,中芯国际自然也提供了MPW服务,不过定价也没有公开。中芯国际在国内的MPW服务中心就有15个之多,工艺上也涵盖了0.18微米到14纳米。根据中芯国际官网的说明,除了每月根据不同工艺提供多达六次共乘服务以外,还提供一年6次55纳米和一年各四次40纳米和28纳米的MPW服务,就频率来看还是挺高的。

成本的话,我们目前可以从一些学界的项目中可以有个大致的了解。比如中科院包云岗教授开展的第一期“一生一芯”计划中,他们的教学芯片就选择了中芯国际的110nm工艺,价格在20万一个Block左右。今年西安交通大学电信学部微电子学院公开的中芯国际55nm流片服务MPW采购项目中,他们选择了中芯国际的55nm射频CMOS工艺,面积为3mm*4mm,给出的预算金额为40万元。

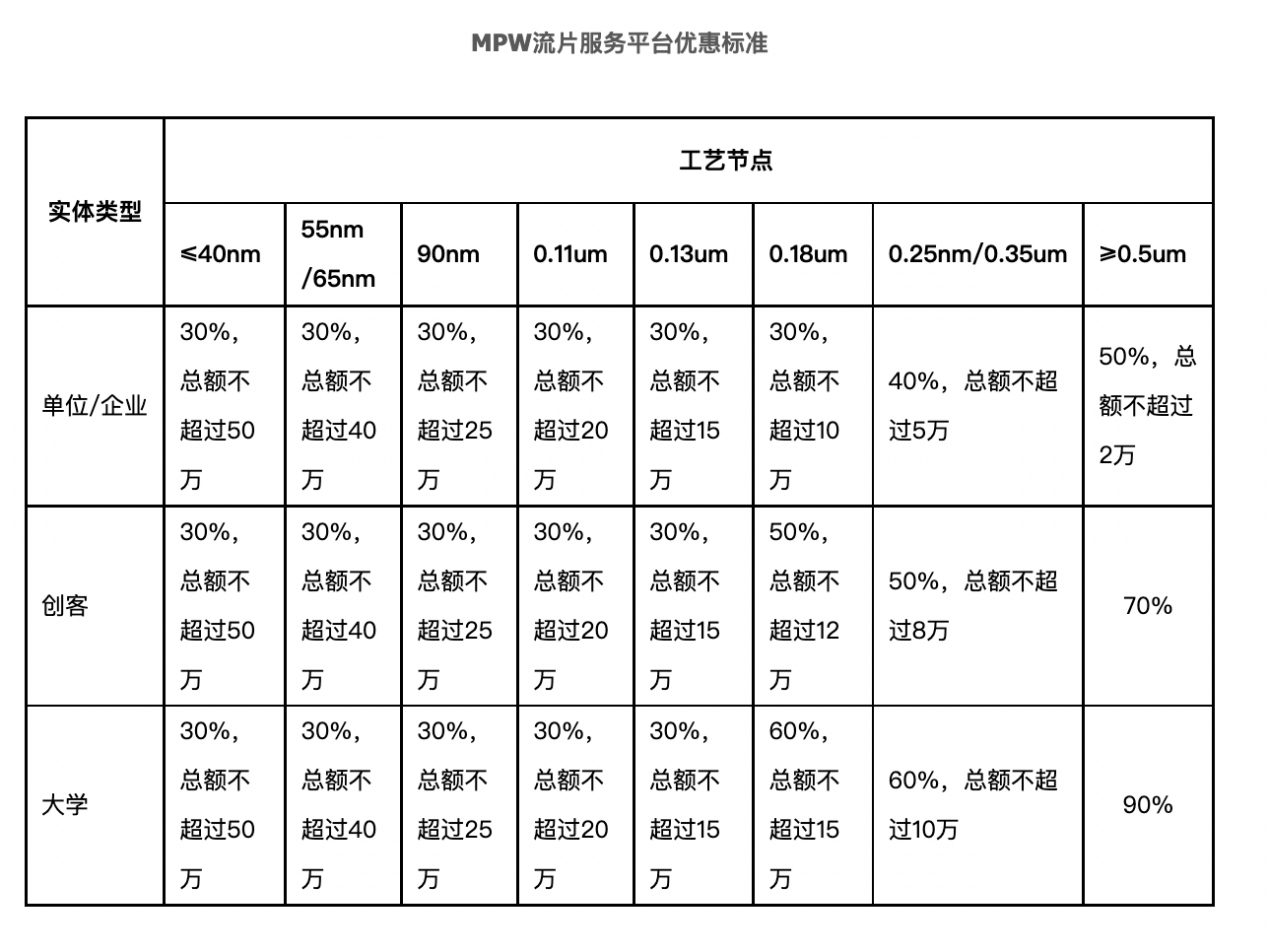

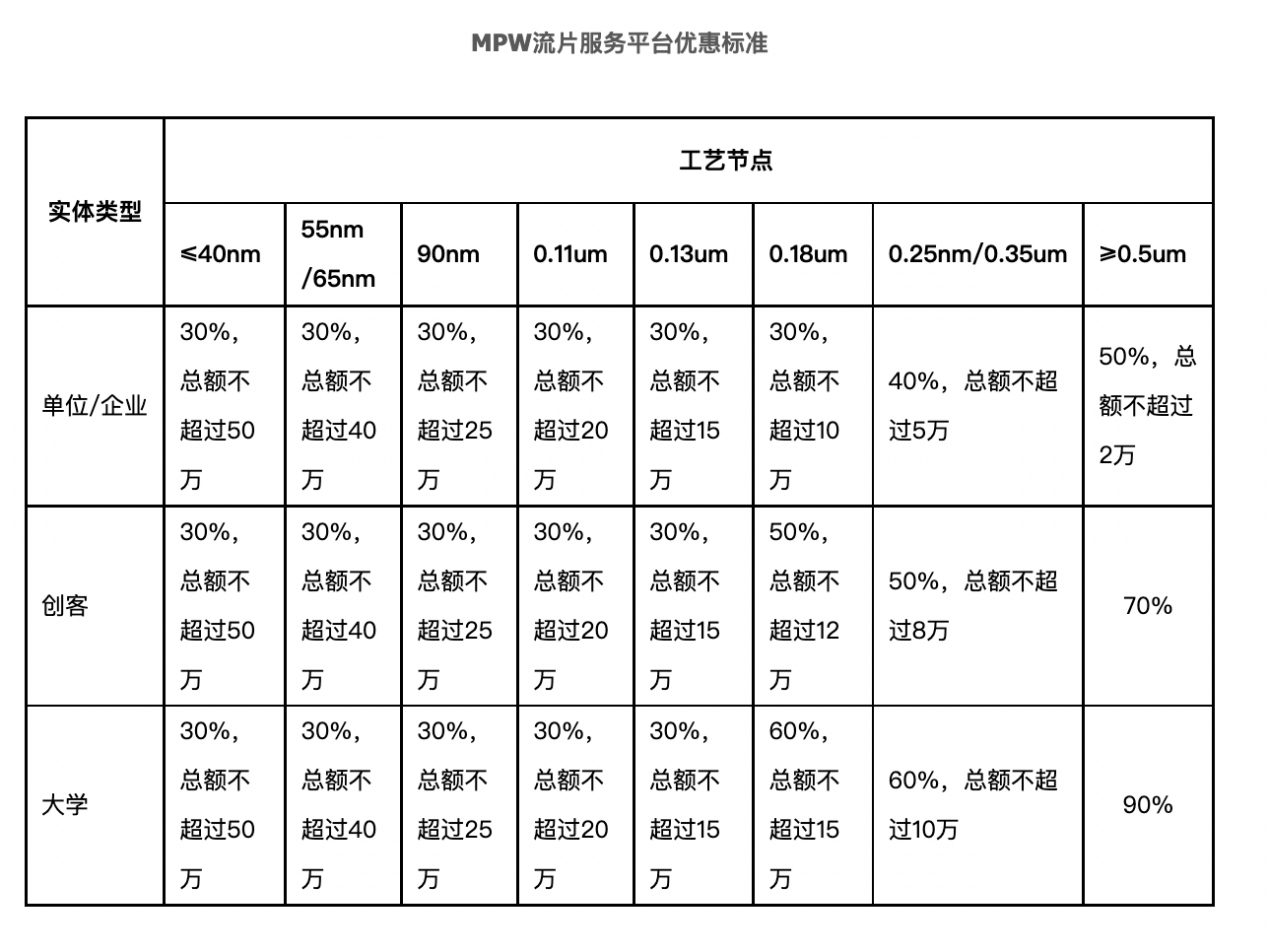

考虑到流片成本对一些初创企业和大学来说也确实很高,所以一些地方政府为了扶持集成电路设计产业的发展,也会给出一些优惠政策,比如国家集成电路设计深圳产业化基地与晶圆代工厂合作打造的MPW流片平台,就对单位/企业、创客和大学在不同的工艺节点上提供了不同程度的优惠,虽然这仅仅这对成熟工艺,但从30%到90%的优惠力度其实已经相当大了。而从上表的总额限制中,其实也可以看出这几个成熟工艺节点在成本上的差距。

晶圆厂积极参与MPW流片

与此同时,晶圆代工厂也开始积极与学研界合作,比如中芯国际就北大清华、东南大学等合作MPW项目。台积电也和台湾半导体研究中心达成合作,对于一些学界的MPW芯片项目提供优惠,甚至对于一些优秀成果产出提出更高的优惠,比如研究中心发表ISSCC论文的项目,可以享受免审查且百分百报销的服务(有工艺节点、芯片数量和总金额的限制)。

目前像美国的Skywater等晶圆代工厂也开始对开源芯片提供免费的MPW服务,只不过这些免费服务提供的工艺并不算先进,而且还是得由谷歌或者政府这样的靠山提供成本支持。不然的话别说免费或增加排期了,哪怕维持这样一个服务频率对晶圆代工厂来说都是一件吃力不讨好的事。

流片花费的时间

对于精力和产能都有限的这些晶圆代工厂来说,他们并不是随时都能帮助客户流片的,所以他们的MPW计划往往都有排期。首先,厂商要想找晶圆代工厂或第三方服务公司询问、预留并下达订单。排上之后提交自己的GDS数据,然后等待其他“拼车人”提交数据后再进入流片过程,最终等待芯片送到自己的手中。从设计提交截止到拿到芯片,可能需要半年以上的时间,这就是时间成本。

以三星为例,三星的12英寸和8英寸晶圆厂都有开展MPW服务,其中12英寸目前最高公开提供5LPE这一5nm的工艺。一般来说,越是先进的工艺,往往每年的MPW流片次数就越少,比如台积电的CyberShuttle可能今年就只提供一次3nm的MPW服务。如何缩短这些MPW项目的周转时间,其实也是晶圆代工厂需要考虑的问题之一。

三星MPW Shuttle 服务 / Samsung Foundry

然后就是流片的金钱成本了,以为光掩膜版的费用对于前期数量不多的试验片来说还是太贵了,所以不少厂商都选择了MPW这种共享光掩膜版的服务,定型后再走Full Mask。当然了,在MPW服务商,每家晶圆代工厂给出的定价其实并没有那么固定,而且不少先进工艺的定价也都是保密的,有的还需要签订NDA保密协议。所以我们一般只能通过第三方MPW服务公司提供的部分定价来获取公开信息。

几家晶圆厂的流片费用

格芯虽然没有参与到先进工艺的竞争中来,但无疑也是全球最大的几家晶圆代工厂之一了。格芯也与不少IC服务平台达成了合作,为不同地区提供MPW服务,所以他们的定价还算是比较公开的。以加拿大的CMC Microsystems给出的数据为例,格芯的12nm工艺12LP的定价为51525美元/mm2。还有一点需要注意的是,即便同为45nm工艺节点,但如果选择特种工艺,比如高压、硅光或射频等等,流片费用也还要再高一截的。

台积电部分工艺的MPW费用 / MUSE Semiconductor

作为国内的龙头企业,中芯国际自然也提供了MPW服务,不过定价也没有公开。中芯国际在国内的MPW服务中心就有15个之多,工艺上也涵盖了0.18微米到14纳米。根据中芯国际官网的说明,除了每月根据不同工艺提供多达六次共乘服务以外,还提供一年6次55纳米和一年各四次40纳米和28纳米的MPW服务,就频率来看还是挺高的。

成本的话,我们目前可以从一些学界的项目中可以有个大致的了解。比如中科院包云岗教授开展的第一期“一生一芯”计划中,他们的教学芯片就选择了中芯国际的110nm工艺,价格在20万一个Block左右。今年西安交通大学电信学部微电子学院公开的中芯国际55nm流片服务MPW采购项目中,他们选择了中芯国际的55nm射频CMOS工艺,面积为3mm*4mm,给出的预算金额为40万元。

考虑到流片成本对一些初创企业和大学来说也确实很高,所以一些地方政府为了扶持集成电路设计产业的发展,也会给出一些优惠政策,比如国家集成电路设计深圳产业化基地与晶圆代工厂合作打造的MPW流片平台,就对单位/企业、创客和大学在不同的工艺节点上提供了不同程度的优惠,虽然这仅仅这对成熟工艺,但从30%到90%的优惠力度其实已经相当大了。而从上表的总额限制中,其实也可以看出这几个成熟工艺节点在成本上的差距。

晶圆厂积极参与MPW流片

与此同时,晶圆代工厂也开始积极与学研界合作,比如中芯国际就北大清华、东南大学等合作MPW项目。台积电也和台湾半导体研究中心达成合作,对于一些学界的MPW芯片项目提供优惠,甚至对于一些优秀成果产出提出更高的优惠,比如研究中心发表ISSCC论文的项目,可以享受免审查且百分百报销的服务(有工艺节点、芯片数量和总金额的限制)。

目前像美国的Skywater等晶圆代工厂也开始对开源芯片提供免费的MPW服务,只不过这些免费服务提供的工艺并不算先进,而且还是得由谷歌或者政府这样的靠山提供成本支持。不然的话别说免费或增加排期了,哪怕维持这样一个服务频率对晶圆代工厂来说都是一件吃力不讨好的事。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

流片

+关注

关注

0文章

28浏览量

9814

发布评论请先 登录

相关推荐

芯片流片的基础知识

宣布了一项重大突破:他们成功流片了全球首颗5纳米工艺的车规级智能驾驶芯片——“神玑NX9031”。这一成就不仅标志着蔚来在芯片设计领域的突破,也预示着即将到来的测试和验证阶段。一旦性能和质量达到设计要求,这款芯片将进入大规模量

PI发热片制作流程(上)

温,一次打样搞定终品,不再需要为一款产品频繁修改设计和打样,节省大量时间成本和经济成本。 ③首创行业发热片布线设计智能计算器,只需要输入四个参数,即可通过大数据智能模型计算,一次性获得

世芯电子成功流片2nm测试芯片

近日,高性能ASIC设计服务领域的领先企业世芯电子(Alchip)宣布了一项重大技术突破——成功流片了一款2nm测试芯片。这一里程碑式的成就,使世芯电子成为首批成功采用革命性纳米片(或全能门GAA)晶体管架构的IC创新者之一。

过流保护片是怎样与电池组连接的

过流保护片(Current Limiting Fuse)是一种电路保护元件,用于保护电池组免受过大电流的损害。它通过限制电流的流动来防止电池过热、损坏或者发生火灾。过流保护片通常与电池

过流保护片的型号选择要考虑哪些参数

过流保护片,也称为过电流保护片或电流限制片,是一种用于电路中保护电子设备免受过大电流损害的元件。选择合适的过流保护片对于确保电路的可靠性和安

消息称小鹏汽车自研智驾芯片流片成功

小鹏汽车近期传来振奋人心的消息,其自主研发的智能驾驶芯片已成功完成流片,标志着小鹏在核心技术自研领域迈出了坚实的一步。据知情人士透露,这款小鹏智驾芯片专为满足高度智能化的驾驶需求而生,采用先进的端到端大模型设计理念,构建了一套舱驾一体的中央计算架构。

LED恒流IC领域的照明方案

调色灯带恒流 IC NU403,NU403恒流芯片+普通调光器可变色温调光 , 面对LED灯带市场成本要求高的用户端打造的一款芯片,,LED灯带灯条20米/30米/50米长距离无压降.亮度一致.

0

发表于 08-02 17:05

蔚来神玑5nm智驾芯片流片成功

在日前举办的2024蔚来创新科技日上,蔚来汽车董事长李斌宣布,全球首颗车规级5纳米高性能智驾芯片蔚来神玑 NX9031流片成功。

InspireSemi Thunderbird I 芯片流片,包含 1536 个 RISC-V 核心

IT之家6月27日消息,芯片设计企业InspireSemi近日宣布其成功采用台积电工艺完成ThunderbirdI加速计算芯片的流片。InspireSemi在该芯片上的合作伙伴还包括日月光(IT之家

珠海錾芯实现28纳米FPGA流片

近日,珠海錾芯半导体有限公司在其官方微博上宣布,已成功实现28纳米流片。此次流片成功的CERES-1 FPGA芯片,不仅对标国际主流28纳米FPGA架构,还实现了管脚和比特

什么是时间片轮转调度?时间片轮转调度算法基本原理

进程切换时间一定的情况下,如果时间片长度设定的越小时,这种浪费更明显。所以,时间片长度与CPU利用率是一对不可调和的矛盾,必须处理好它们之间的关系。

流片的时间与金钱成本

流片的时间与金钱成本

评论