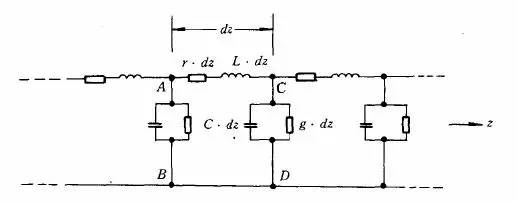

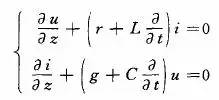

从此图可以推导出电报方程

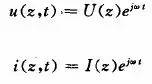

取传输线上的电压电流的正弦形式

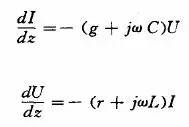

得

推出通解

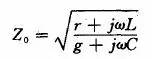

定义出特性阻抗

无耗线下r=0, g=0 得

注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义)

特性阻抗与波阻抗之间关系可从

此关系式推出。

Ok,理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓 的反射现象等等。在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来。

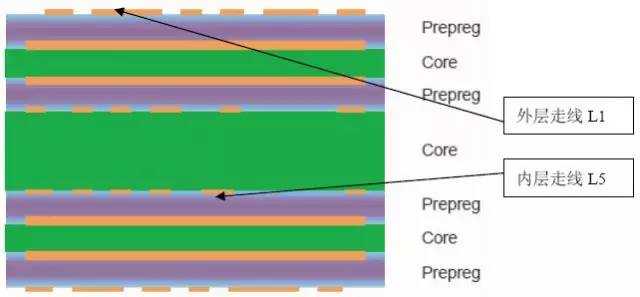

叠层(stackup)的定义

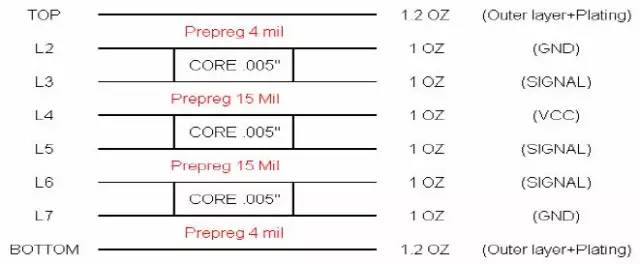

我们来看如下一种stackup,主板常用的8 层板(4 层power/ground 以及4 层走线层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为L1,L4,L5,L8

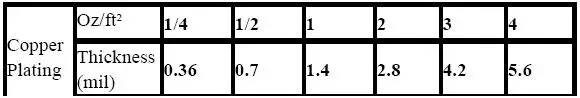

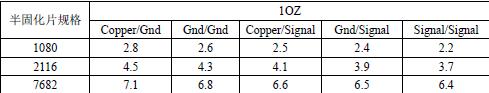

下面熟悉下在叠层里面的一些基本概念,和厂家打交道经常会使用的Oz 的概念

Oz 本来是重量的单位Oz(盎司 )=28.3 g(克)

在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz,对应的单位如下

介电常数(DK)的概念

电容器极板间有电介质存在时的电容量Cx 与同样形状和尺寸的真空电容量Co之比为介电常数:

ε = Cx/Co = ε‘-ε“

Prepreg/Core 的概念

pp 是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两面都覆有铜箔,而pp 没有。

传输线特性阻抗的计算

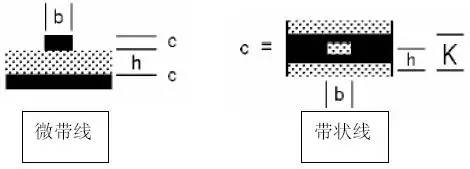

首先,我们来看下传输线的基本类型,在计算阻抗的时候通常有如下类型:微带线和带状线,对于他们的区分,最简单的理解是,微带线只有1 个参考地,而带状线有2个参考地,如下图所示

对照上面常用的8 层主板,只有top 和bottom 走线层才是微带线类型,其他的走线层都是带状线类型。

在计算传输线特性阻抗的时候, 主板阻抗要求基本上是:单线阻抗要求55 或者60Ohm,差分线阻抗要求是70~110Ohm,厚度要求一般是1~2mm,根据板厚要求来分层得到各厚度高度。

在此假设板厚为1.6mm,也就是63mil 左右, 单端阻抗要求60Ohm,差分阻抗要求100Ohm,我们假设以如下的叠层来走线

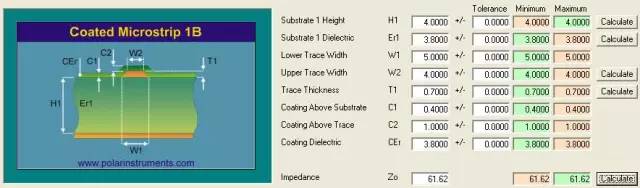

先来计算微带线的特性阻抗,由于top 层和bottom 层对称,只需要计算top 层阻抗就好的,采用polar si6000,对应的计算图形如下:

在计算的时候注意的是:

1,你所需要的是通过走线阻抗要求来计算出线宽W(目标)

2,各厂家的制程能力不一致,因此计算方法不一样,需要和厂家进行确认

3,表层采用coated microstrip 计算的原因是,厂家会有覆绿漆,因而没用surface microstrip 计算,但是也有厂家采用surface microstrip 来计算的,它是经过校准的

4,w1 和w2 不一样的原因在于pcb 板制造过程中是从上到下而腐蚀,因此腐蚀出来有梯形的感觉(当然不完全是)

5,在此没计算出精确的60Ohm 阻抗,原因是实际制程的时候厂家会稍微改变参数,没必要那么精确,在1,2ohm 范围之内我是觉得没问题

6,h/t 参数对应你可以参照叠层来看

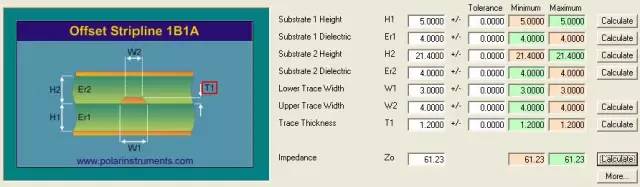

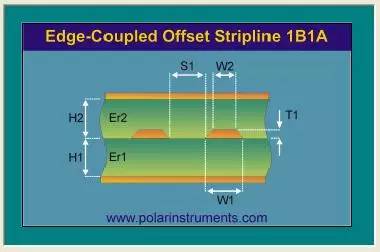

再计算出L5 的特性阻抗如下图

记得当初有各版本对于stripline 还有symmetrical stripline 的计算图,实际上的差异从字面来理解就是symmetrical stripline 其实是offset stripline 的特例H1=H2

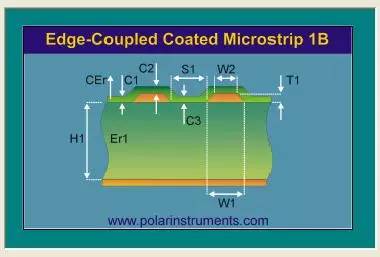

在计算差分阻抗的时候和上面计算类似,除所需要的通过走线阻抗要求来计算出线宽的目标除线宽还有线距,在此不列出。

选用的图是

在计算差分阻抗注意的是:

在满足DDR2 clock 85Ohm~1394 110Ohm 差分阻抗的同时又满足其单端阻抗,因此我通常选择的是先满足差分阻抗(很多是电流模式取电压的)再考虑单端阻抗(通常板厂是不考虑的,实际做很多板子,问 题确实不算大,看样子差分线还是走线同层同via 同间距要求一定要符合)

审核编辑:汤梓红

-

传输线

+关注

关注

0文章

377浏览量

24209 -

特性阻抗

+关注

关注

1文章

78浏览量

16996

原文标题:阻抗怎么计算?

文章出处:【微信号:衡丽,微信公众号:衡丽】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

传输线特性阻抗的计算

传输线特性阻抗的计算

评论