ePort-M模块到手,通信接口不了解?TX线需要串接电阻?信号线不懂处理、走线麻烦?3分钟带你了解ePort关键设计技巧,轻松上手!

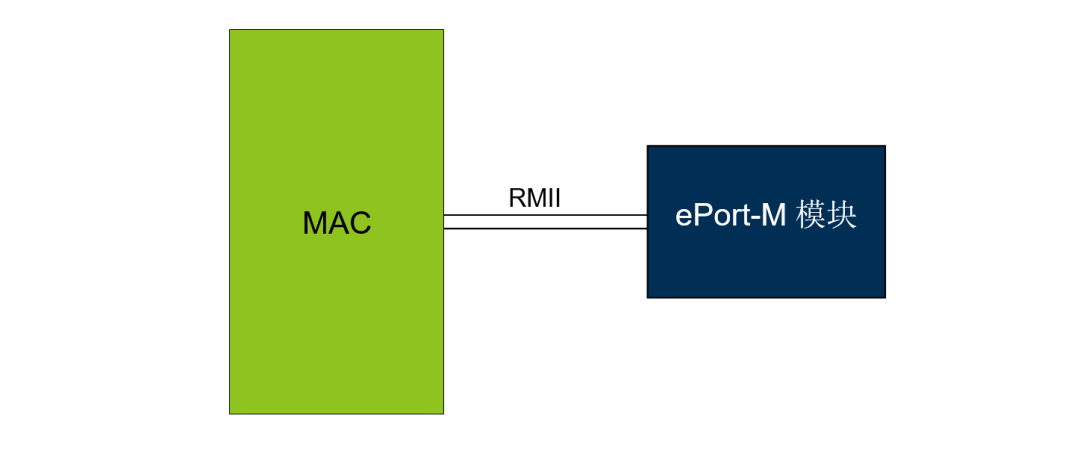

ePort-M百兆以太网模块采用了RMII接口(精简的独立于介质接口),相比较于MII接口(媒体独立接口),RMII通信所需要的引脚数更少,根据IEEE802.3标准,MII接口需要16个信号引脚,RMII接口则只需要7个信号引脚,此时ePort-M模块的时钟信号频率为50MHz,该时钟信号由MAC端提供或外部时钟源提供。

ePort-M模块简单易用,然而应用到产品时,如何保证模块的正常通信,提高模块的的通信质量呢?下面介绍如何进行ePort-M模块的原理图设计以及PCB设计。

原理图设计

1、发送信号引脚RMII_TXEN、RMII_TXD0、RMII_TXD1需串联22Ω电阻,对信号线进行阻抗匹配,防止信号反射,ePort-M模块内部相关信号已串联电阻;

2、模块的RMII_CLK_50M直接与MAC端的50MHz时钟信号连接;

3、模块的RMII_RXER、RMII_CRS_DV、RMII_RXD0、RMII_RXD1、RMII_MDC、RMII_MDIO信号直接与MAC端的对应信号连接;

4、模块的复位信号RMII_RSTn、中断信号RMII_INTn内部已有4.7k上拉电阻,复位信号RMII_RSTn必须接到MCU的GPIO管脚,用于上电复位;若GPIO管脚资源紧张,RMII_INTn引脚可不接。

PCB设计

1、ePort-M模块PCB布线时,发送信号RMII_TXEN、RMII_TXD0、RMII_TXD1串联的22Ω电阻需要靠近MCU放置;

2、以太网的信号线需要控制单端50Ω阻抗匹配,避免信号传输过程出现反射以及过冲;

3、PCB走线保证TXD组内100mil等长,RXD组内100mil等长处理,模块内部TXD/RXD组已做等长处理,因此在处理等长时,无需考虑ePort-M模块内部的走线长度;

4、以太网复位信号是敏感信号,PCB走线距离MCU应尽量短,并且远离其他高速信号;

5、在条件允许的情况下,以太网时钟信号线两侧需要进行包地处理,包地线应该尽量粗,同时包地线上应该多打地孔,以减少时钟信号线与其他信号线之间的串扰。

审核编辑:汤梓红

-

pcb

+关注

关注

4309文章

22899浏览量

395261 -

通信接口

+关注

关注

3文章

234浏览量

30950

原文标题:3分钟了解ePort关键设计技巧

文章出处:【微信号:ZLG_zhiyuan,微信公众号:ZLG致远电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCB原理图与PCB设计文件的区别

Altium Designer 实用宝典—原理图与PCB设计

【技术应用】一步完成ePort-M百兆模块地址配置

3分钟了解ePort关键设计技巧

【技术分享】M6Y2C+ePort-M辐射整改

【产品应用】3分钟了解ePort关键设计技巧

ePort-M模块的原理图设计以及PCB设计

ePort-M模块的原理图设计以及PCB设计

评论