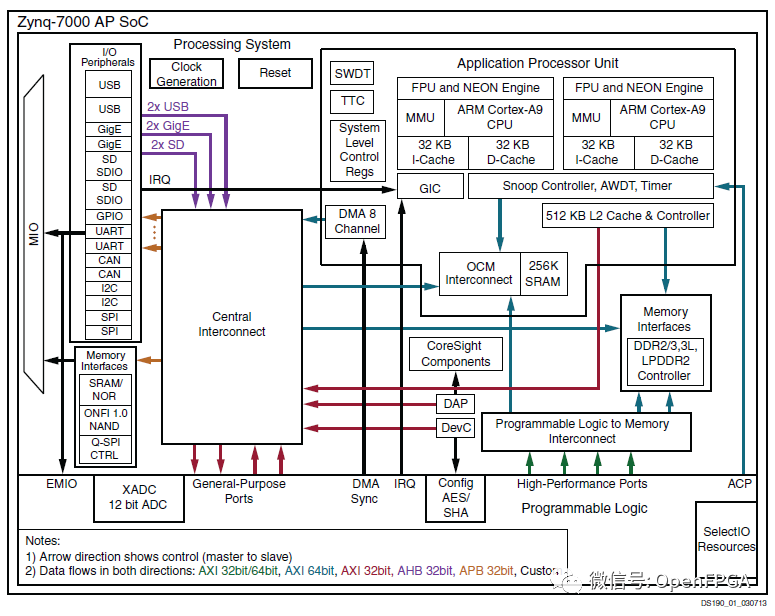

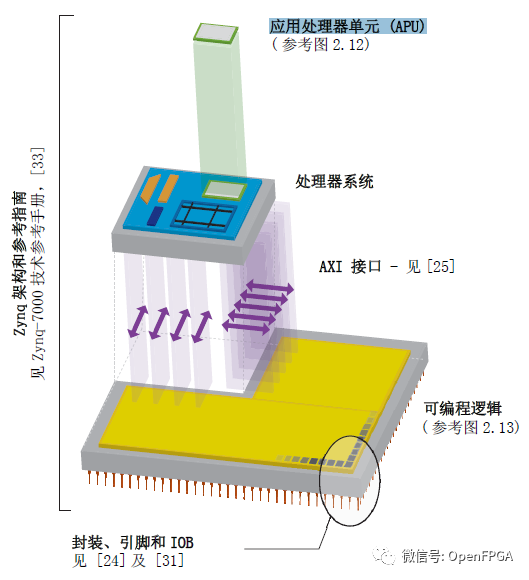

ZYNQ架构

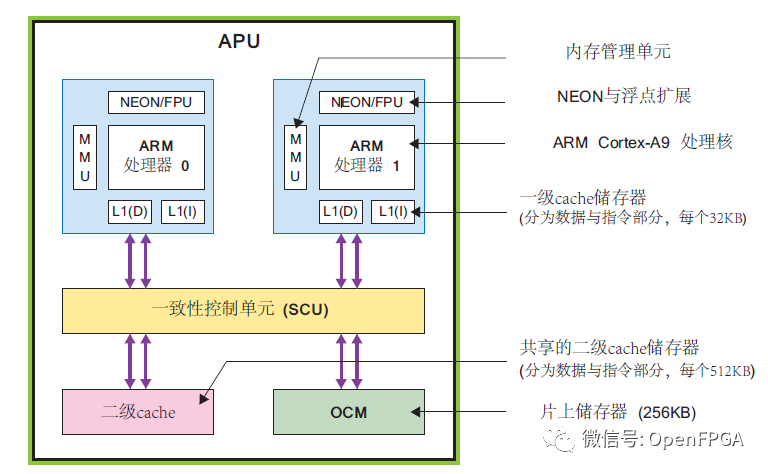

双核ARM Cortex-A9 处理器:ARM Cortex-A9 是一个应用级的处理器,能运行完整的像Linux 这样的操作系统

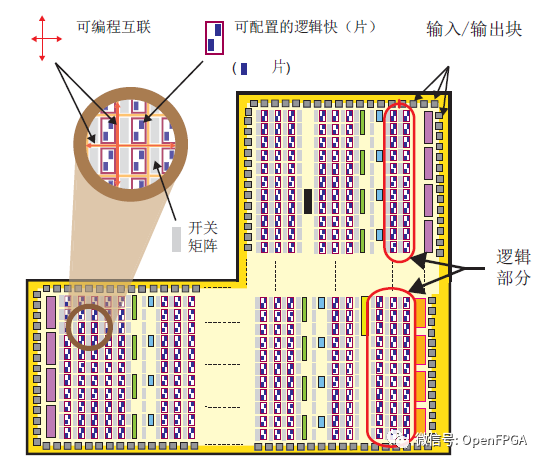

传统的现场可编程门阵列(Field Programmable Gate Array,FPGA)逻辑部件:基于Xilinx 7 系列的FPGA 架构

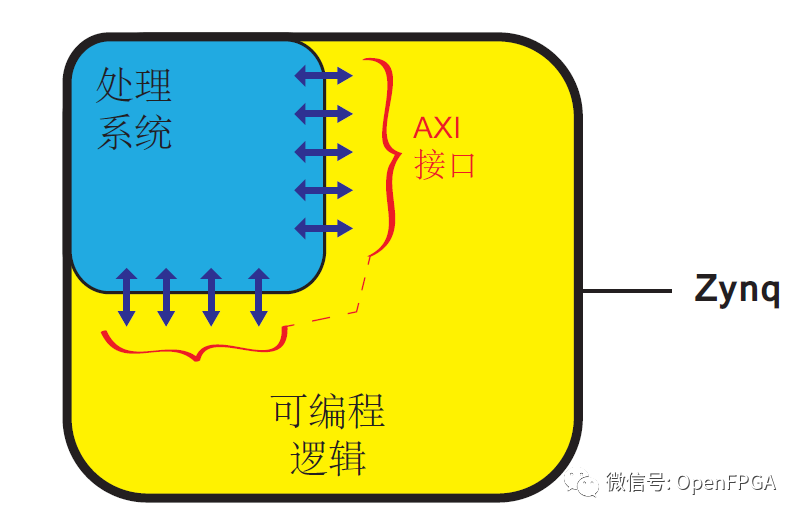

这个架构实现了工业标准的AXI 接口,在芯片的两个部分之间实现了高带宽、低延迟的连接。

这意味着处理器和逻辑部分各自都可以发挥最佳的用途,而不会有在两个分立的芯片之间的那种接口开销。

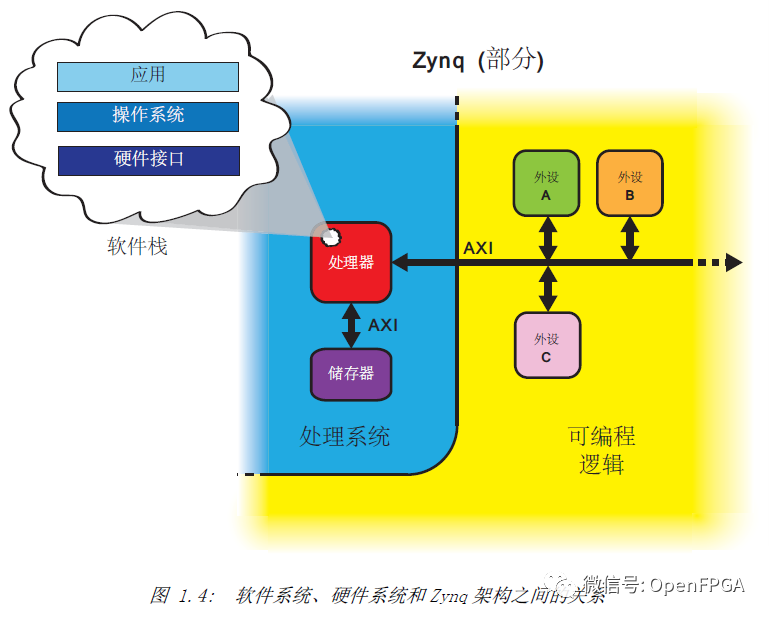

外设是处理器之外的功能部件,一般从事三种功能之一:(一)协处理器—— 辅助主处理器的单元,往往是被优化用于特定任务;(二)与外部接口交互的核心,如连接到LED 和开关、编解码器等等;(三)额外的存储器单元。

PS具有固定的架构,承载了处理器和系统存储区

而PL完全是灵活的,给了设计者一面“ 空白画布” 来创建定制的外设,或重用标准外设。

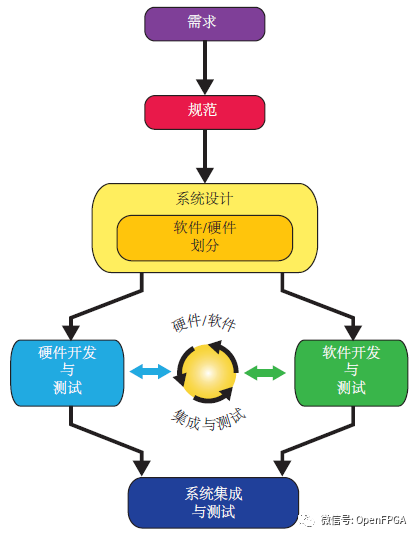

ZYNQ的SoC设计流基本模型

ZYNQ芯片

处理器系统(PS)

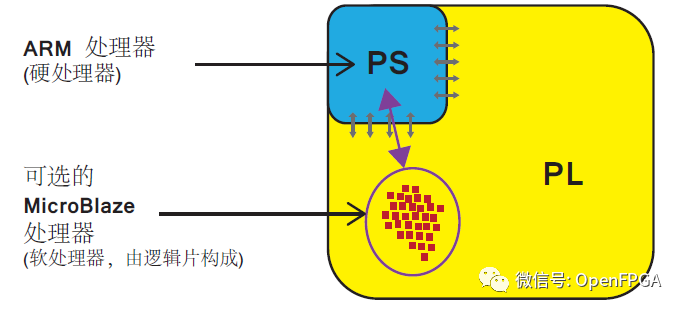

ARM是一颗“硬”处理器,硬件处理器以外的另一种方案,就像Xilinx 的MicroBlaze这样的“软”处理器,这是由可编程逻辑部分的单元组合而成的。也就是说,一个软处理器的实现和部署在FPGA 的逻辑结构里的任何其他IP 包是等价的。要求不高的任务可以从主的ARM Cortex-A9 处理器上脱离出来,分配给软处理器,软处理器与ARM协同工作,提升整体性能

PS里并非只有ARM 处理器,还有一组相关的处理资源,形成了一个应用处理器单元(Application Processing Unit,APU),另外还有扩展外设接口、cache 存储器、存储器接口、互联接口和时钟发生电路

处理器系统外部接口——PS 和外部接口之间的通信主要是通过复用的输入/ 输出(Multiplexed Input/Output,MIO)实现的。这样的连接也可以通过扩展EMIO (ExtendedMIO,EMIO)来实现,EMIO 并不是PS 和外部连接之间的直接通路,而是通过共用了PL 的I/O 资源来实现的。

可用的I/O 包括标准通信接口(SPI,I2C,USB,SD,CAN,UART,GigE)和通用输入/ 输出(General Purpose Input/Output,GPIO)

可编程逻辑(PS)

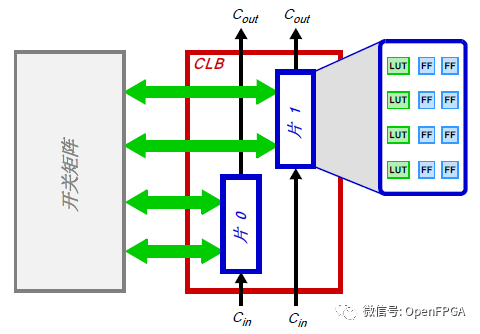

LUT-查找表(https://www.cnblogs.com/lbf-19940424/p/6564885.html)

FF-触发器,一个实现1 位寄存的时序电路,带有复位功能。FF 的一种用处是实现锁存。

CLB-可配置编程逻辑块

IOB-输入/ 输出块(Input/Output Blocks,IOB)-实现了PL 逻辑资源之间的对接,并且提供物理设备“ 焊盘” 来连接外部电路。每个IOB 可以处理一位的输入或输出信号。IOB 通常位于芯片的周边。

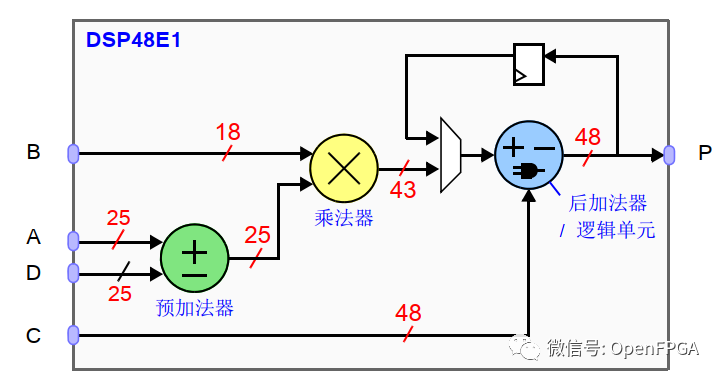

除了通用的部分,还有两个特殊用途的部件:满足密集存储需要的块RAM和用于高速算术的DSP48E1片

通用输入输出IOB

通信接口--包括PCIExpress、串行RapidIO、SCSI 和SATA

其他可编程逻辑扩展接口--XADC,时钟,编程与调试

处理器系统与可编程逻辑的接口

1、AXI标准--Advanced eXtensible Interface

有三类AXI4总线协议

• AXI4 [2] — 用于存储映射链接,它支持最高的性能:通过一簇高达256 个数据字(或“ 数据拍(data beats)”)的数据传输来给定一个地址。

• AXI4-Lite [2] — 一种简化了的链接,只支持每次连接传输一个数据(非批量)。AXI4-Lite也是存储映射的:这种协议下每次传输一个地址和单个数据。

• AXI4-Stream [1] — 用于高速流数据,支持批量传输无限大小的数据。没有地址机制,这种总线类型最适合源和目的地之间的直接数据流(非存储器映射)

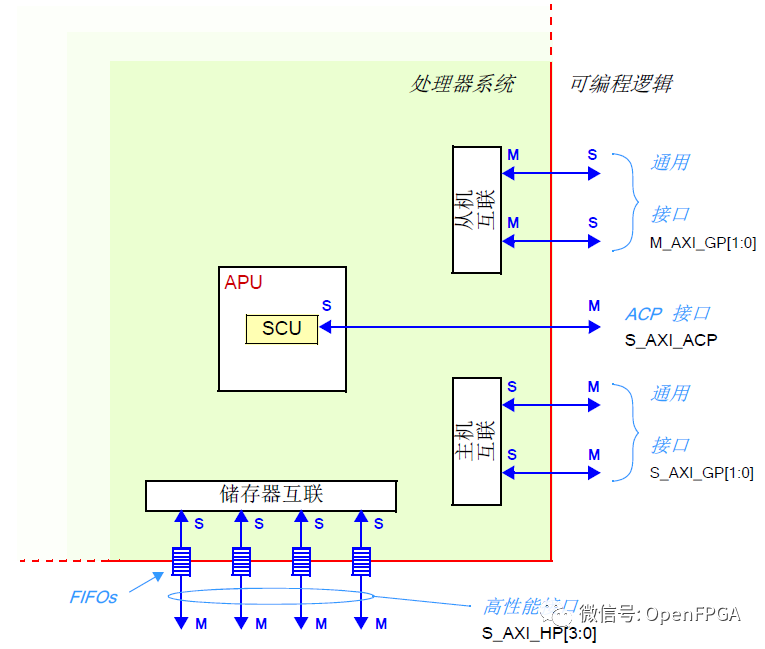

互联(Interconnect)— 互联实际上是一个开关,管理并直接传递所连接的AXI 接口之间的通信。在PS 内有几个互联,其中有些还直接连接到PL (如图2.9),而另一些是只用于内部连接的。这些互联之间的连接也是用AXI 接口所构成的。

接口(Interface)— 用于在系统内的主机和从机之间传递数据、地址和握手信号的点对点连接。(M-主机,S-从机)

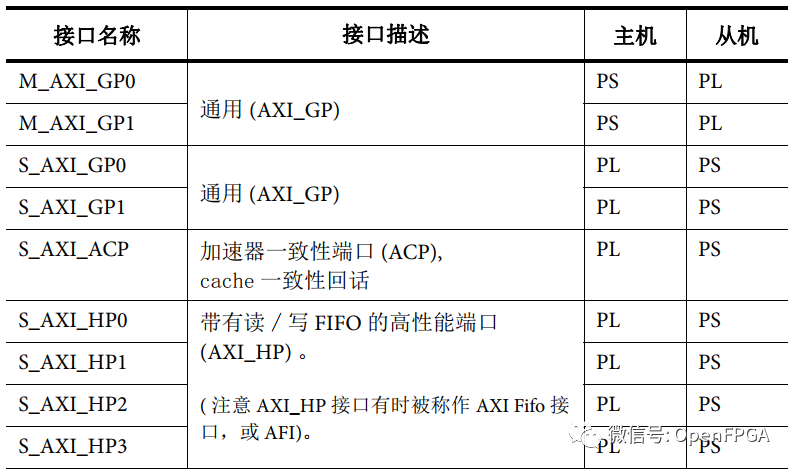

• 通用AXI(General Purpose AXI) — 一条32 位数据总线,适合PL 和PS 之间的中低速通信。接口是透传的不带缓冲。总共有四个通用接口:两个PS 做主机,另两个PL 做主机。

• 加速器一致性端口(Accelerator Coherency Port) — 在PL 和APU 内的SCU之间的单个异步连接,总线宽度为64 位。这个端口用来实现APU cache 和PL的单元之间的一致性。PL 是做主机的。

• 高性能端口(High Performance Ports) — 四个高性能AXI 接口,带有FIFO缓冲来提供“ 批量” 读写操作,并支持PL 和PS 中的存储器单元的高速率通信。数据宽度是32 或64 位,在所有四个接口中PL 都是做主机的。

表 2.2 给出给出了每个接口的简述,标出了主机和从机 (按照惯例,主机是控制总线并发起会话的,而从机是做响应的)。注意接口命名的规范(在表 2.2 的第一列)是表示了 PS 的角色的,也就是说,第一个字母 “M” 表示 PS 是主机,而第一个字母 “S” 表示 PS 是从机。

2、EMIO接口

3、其他PL-PS信号

跨越PS-PL 边界的其他信号包括看门狗定时器、重启信号、中断和DMA 接口信号。

安全

总结

附议:

本人觉得除了整体架构的创新,灵活的IO也是ZYNQ成为受欢迎的一部分:

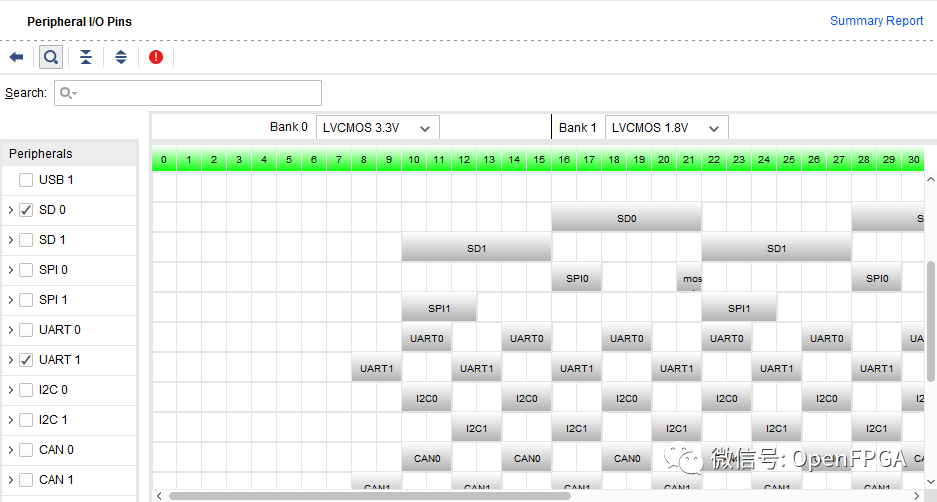

Multiplexed I/O (MIO):PS端外设IO复用,这是什么概念呢?前面介绍了ZYNQ主要分PS/PL两大组成模块,PS端前面介绍的外设如USB/CAN/GPIO/UART等都必要需要引脚与外界打交道,这里所谓的复用与常见的单片机、处理器里引脚复用的概念一样。但是(这里划重点),ZYNQ具有高达54个PS引脚支持MIO,MIO具有非常高的灵活度以达到灵活配置,这给硬件设计、PCB布板带来了极大的便利!,MIO的配置利用vivado软件可以实现灵活配置,如下图所示。

硬件工程师往往发现对一个复杂的系统的布局布线,常常会很困难,也常因为不合理的布局布线而陷入EMC深坑。ZYNQ的IO引脚高度灵活性,无疑在电路设计方面提供极大的方便,可实现非常灵活的PCB布局布线。从而在EMC性能改善方面带来了很大便利。

灵活的PS-PL互连接口

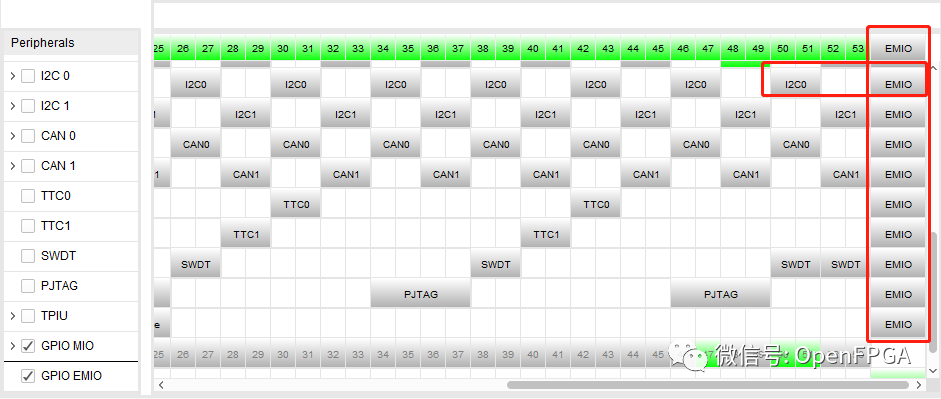

Extended Multiplexed I/O (EMIO):扩展MIO,如果想通过PS来访问PL又不想浪费AXI总线时,就可以通过EMIO接口来访问PL。54个I/O中,其中一部分只能用于MIO,大部分可以用于MIO或EMIO,少量引脚只能通过EMIO访问。

如上图,比如I2C0则可以通过EMIO映射到PL端的引脚输出,这无疑又增加了更多的灵活性!

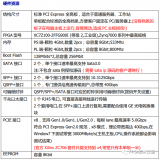

PS-PL接口HP0-HP3:如上架构图中AXI high-performance slave ports (HP0-HP3) 实现了PS-PL的接口

可配置的32位或64位数据宽度

只能访问片上存储器OCM(On chip memory)和DDR

AXI FIFO接口(AFI)利用1KB FIFOs来缓冲大数据传输

PS-PL接口GP0-GP1:如上架构图中AXI general-purpose ports

两个PS主接口连接到PL的两个从设备

32位数据宽度

一个连接到CPU内存的64位加速器一致端口(ACP)AXI从接口,ACP 是 SCU (一致性控制单元)上的一个 64 位从机接口,实现从 PL 到 PS 的异步 cache 一致性接入点。ACP 是可以被很多 PL 主机所访问的,用以实现和 APU 处理器相同的方式访问存储子系统。这能达到提升整体性能、改善功耗和简化软件的效果。ACP 接口的表现和标准的 AXI 从机接口是一样的,支持大多数标准读和写的操作而不需要在 PL 部件中加入额外的一致性操作。

DMA, 中断, 事件信号:

处理器事件总线信号事件信息到CPU

PL外设IP中断到PS通用中断控制器(GIC)

四个DMA通道RDY/ACK信号

扩展多路复用I/O (EMIO)允许PS外设端口访问PL逻辑和设备I/O引脚。

时钟以及复位信号:

四个PS时钟带使能控制连接到PL

四个PS复位信号连接到PL

审核编辑 :李倩

-

架构

+关注

关注

1文章

514浏览量

25485 -

Zynq

+关注

关注

10文章

610浏览量

47192

原文标题:ZYNQ架构

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

zynq7000 BSP无法在u-boot加载运行怎么解决?

正点原子ZYNQ7015开发板!ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2,性能强悍,资料丰富!

zynq7000 BSP无法在u-boot加载运行,为什么?

[XILINX] 正点原子ZYNQ7035/7045/7100开发板发布、ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2!

简谈Xilinx Zynq-7000嵌入式系统设计与实现

Xilinx ZYNQ 动手实操演练

Zynq-7000为何不是FPGA?

ZYNQ架构及ZYNQ芯片

ZYNQ架构及ZYNQ芯片

评论