摘要:针对 L频段数字航空通信系统接收机 DME 信号干扰抑制算法缺乏真实验证平台这一问题,利用软件无线电技术搭建 L⁃DACS1 的原型系统。按照 L⁃DACS1 系统前向链路的技术参数和超帧结构,设计实现了基于 Yun SDR320 和 Matlab的 L⁃DACS1 系统前向链路发射机和接收机的原型构建,在真实的无线信道环境下实现信号的发送与接收。测试结果表明,所设计的 L⁃DACS1系统前向链路平台符合系统规范、工作稳定,该平台可以用作未来 DME干扰抑制算法的验证平台。

0 引 言

为了保障民用航空器安全、可靠、高效的运行,提升空 域 容 量 ,国 际 民 航 组 织(International Civil AviationOrganization,ICAO)将L频段数字航空通信系统(L⁃bandDigital Aeronautical Communication System,L⁃DACS)确立为未来航空移动通信主要依赖的技术手段之一[1]。目前,L⁃DACS 有两种候选技术方案:一种是基于多载波调制技术的L⁃DACS1[2];另一种是基于单载波高斯最小频移键控的 L⁃DACS2[3]。其中,L⁃DACS1因其具有传输容量大、抗多径能力强、频谱效率高的优点而获得航空制造业和学术界的广泛关注[4]。由于L⁃DACS1系统的工作频谱与L频段已 有 的 DME(Distance MeasureEquipment,DME)系统频谱存在部分交叠[5],导致 DME信号对L⁃DACS1系统接收机产生了不可避免的干扰。

目前,国内外针对L⁃DACS1系统接收机如何抑制DME信号干扰的问题提出了很多算法,例如:脉冲熄灭与脉冲限幅干扰抑制算法[6]、压缩感知信号重构干扰抑制算法[7]、判决反馈脉冲噪声估计干扰抑制算法[8]等,这些干扰抑制算法的研究主要通过理论分析与仿真相结合的方式,并没有搭建真实的测试平台验证其有效性。为了更深入地研究DME信号对L⁃DACS1系统接收机性能的影响,本文根据L⁃DACS1系统规范[2],基于软件无线电 Yun SDR320平台和Matlab软件平台设计实现了L⁃DACS1系统前向链路的发射机与接收机,发射机产生发射信号并经过真实的无线信道后由接收机接收。该平台可以验证L⁃DACS1系统发射机和接收机的性能,也为进一步验证和比较不同DME干扰抑制算法的有效性提供了一个真实的环境平台。

1 Yun SDR 软件无线电平台

软件无线电是指在硬件条件不变的前提下,通过软件编程对物理硬件进行配置来实现各种无线电功能[9]。利用软件无线电技术,通过软件平台实现通信系统链路的各种功能,包括信号的产生、调制解调、编码译码、滤波等。

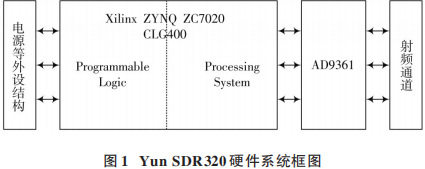

北京威视锐科技公司的产品Yun SDR320实验平台是专为无线通信系统研究而开发的一款便携式软件无线电平台。Yun SDR320通过千兆以太网线与PC机进行数据交互,由于其具有更宽的频谱范围和模拟带宽而受到广泛应用。Yun SDR320实验平台的基本硬件结构由 ZYNQ 嵌入式处理器、AD9361[10]射频前端和电源电路三部分构成。其中,嵌入式处理器采用 Xilinx ZYNQZC7Z020 CLG400型号的SoC芯片完成信源的数字基带信号处理过程。射频前端采用 ADI公司的 AD9361芯片实现数字信号处理、数字上/下变频、数/模和模/数转换、滤波、射频收发等功能。Yun SDR320的硬件系统框图如图 1所示。

2 L⁃DACS1系统前向链路物理层传输特性

L⁃DACS1是一个基于正交频分复用(OrthogonalFrequency Division Multiplexing,OFDM)多载波传输技术的航空移动通信系统,采用频分双工(Frequency ⁃Division Duplex,FDD)的通信方式[2]。系统前向链路采用OFDM传输技术,基本数据传输单元是超帧,工作频段为985.5~1 085.5MHz,比特传输速率为303~1373Kb/s。

2.1 L⁃DACS1系统前向链路物理层技术参数

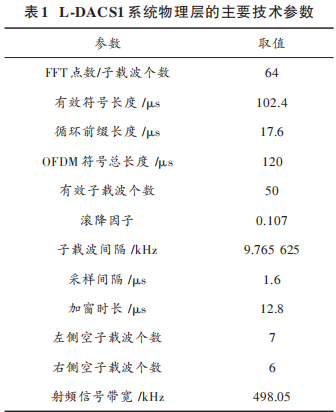

L⁃DACS1系统物理层的主要技术参数如表1所示。

L⁃DACS1系统前向链路OFDM系统子载波总数为64个,其中包含50个有效子载波,14个直流子载波和空子载波,子载波间隔为9.765 625 kHz,射频信道带宽为498.05kHz。OFDM 符号总长度为120 μs,其中有效符号长度为102.4 μs,循环前缀长度为17.6 μs。

2.2 L⁃DACS1系统前向链路帧结构

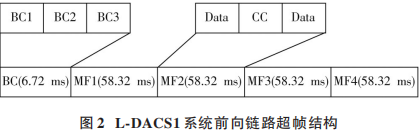

L⁃DACS1系统前向链路的超帧结构如图2所示。每个超帧由1个广播(BC)帧和4个多帧(MF)组成,其中,广播帧用于传输前向链路的广播信息,多帧用于承载高层的调制符号。每个广播帧的持续时间为6.72ms,由3个子帧组成,分别是BC1、BC2和BC3,BC1和BC3子帧完全相同,持续时间为1.8 ms,BC2子帧的持续时间为3.12 ms。每个多帧的持续时间为58.32 ms,由9个长度可变的Data/CC子帧组成,Data/CC子帧的持续时间为6.48 ms。每个超帧的持续时间为240 ms,可以传输的OFDM符号总数为2000个。

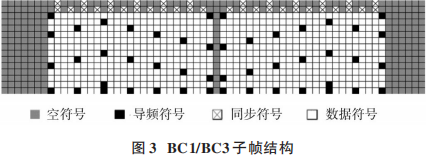

BC1/BC3子帧结构如图3所示,每个子帧包含三部分:同步符号、数据符号和导频符号。其中,同步符号用于接收机建立超帧同步,定位帧头的准确起始位置;数据符号用于承载高层的比特信息;导频符号用于接收机进行信道估计。

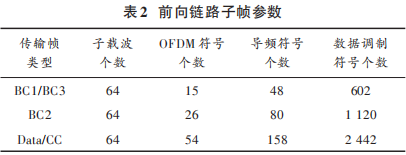

BC2、Data/CC 子帧结构与BC1/BC3子帧结构类似,其参数如表2所示。

3 系统设计与实现

3.1 系统平台结构设计

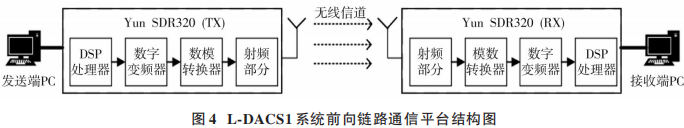

L⁃DACS1系统前向链路通信平台主要包括两个部分,即PC端和Yun SDR320设备,其结构示意图如图4所示。

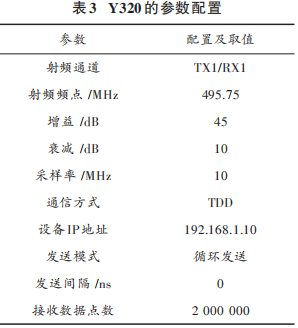

在发射端,由发送端PC产生的数字基带信号通过千兆以太网线送入DSP处理器完成数字调制,再由数字上变频器将基带信号转变为中频信号,之后经过数模转换器转换为模拟信号,通过射频部分将模拟信号放大到足够功率,由天线发射到无线信道中。在接收端,由天线接收到的无线电信号经过射频放大后对其进行模/数转换,数字化之后的信号经过数字下变频器将中频信号转变为基带信号,然后将基带信号送入DSP处理器完成数字解调,将解调后的信号通过千兆以太网线送入接收端PC恢复出原始发送序列。Y320的参数配置如表3所示。

3.2 发射机的实现

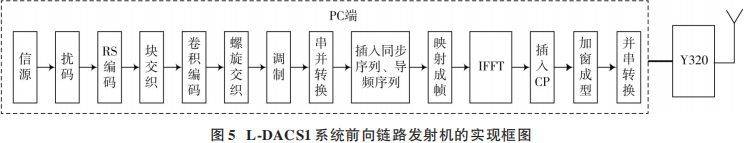

L⁃DACS1系统前向链路发射机主要由编码交织、调制、映射成帧和加窗成型几部分构成,其实现框图如图5所示。

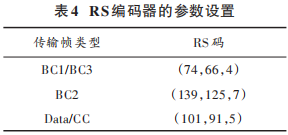

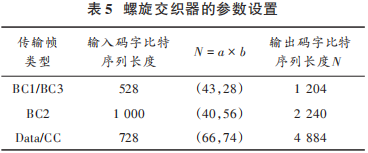

为了将传输的比特序列随机化,信源产生的比特序列首先经过比特扰码处理;选择合适的编码方式,其中,外编码采用RS编码,其参数设置如表4所示,内编码采用(171,133,7)卷积码;之后根据传输帧的类型选择合适的交织方式,其中,广播(BC)帧采用的交织方式为螺旋交织,Data/CC帧采用的交织方式为块交织与螺旋交织,其参数设置如表5所示。

对编码和交织后的比特序列进行符号调制;将符号调制后的序列与生成的导频序列、同步序列分别映射到BC1、BC2、BC3子帧及Data/CC子帧;根据L⁃DACS1系统前向链路超帧结构将各子帧组合成为一个超帧,再将超帧通过IFFT完成OFDM符号调制;最后插入循环前缀(CP),进行时域加窗处理,通过并/串转换将并行数据转换为串行数据,通过千兆以太网线传送到Y320。至此实现了L⁃DACS1系统前向链路的发射机部分设计。

3.3 接收机的实现

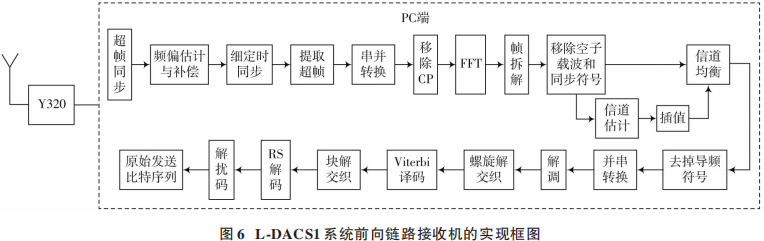

L⁃DACS1系统前向链路接收机主要由同步、信道估计、信道均衡和解调译码等部分构成,其实现框图如图6所示。

Y320接收到的信号经过千兆以太网线传送到PC端,将得到的信号首先根据广播(BC)帧的特定结构确定出超帧帧头的大概起始位置,建立接收机的超帧同步,然后利用前向链路各数据帧的同步符号获得接收信号的载波频偏,并对其进行补偿,之后利用同步符号进行细定时同步,确定出超帧帧头的准确起始位置;从接收数据中提取出一个完整的超帧,并进行串并转换,移除CP,之后通过FFT完成OFDM解调;将解调之后的超帧进行帧拆解,拆解出BC1、BC2、BC3子帧和Data/CC子帧;移除子帧中的空子载波和直流子载波,分别提取子帧中的导频符号进行信道估计,并根据各个子信道的信道估计值进行一维线性插值,之后进行信道均衡;将信道均衡之后的数据移除导频符号,进行并串转换;根据传输帧的类型,对得到的串行数据进行解调、解交织和译码,其中解交织和译码的参数设置均与发射机保持一致;最后经过解扰恢复出原始发送比特序列。至此实现了L⁃DACS1系统前向链路的接收机部分设计。

4 测试及分析

为了测试基于Y320的L⁃DACS1系统前向链路发射机与接收机设计的正确性,本文从发射机超帧功率谱图、接收机接收信号功率谱图和子帧星座图的收敛程度三方面进行观测。

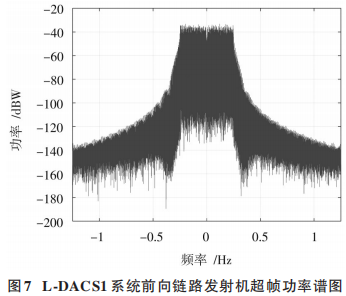

L⁃DACS1系统前向链路发射机超帧功率谱图如图7所示。由发射机功率谱图可以观测出,L⁃DACS1系统前向链路的射频信号带宽接近0.5MHz,零频处为直流,不传输任何信息,测试结果与L⁃DACS1系统前向链路发射机标准一致。

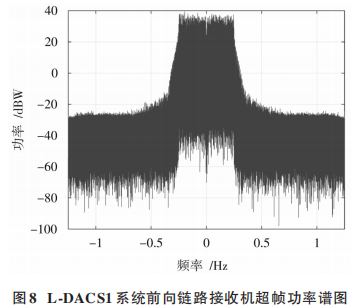

L⁃DACS1系统前向链路接收机超帧功率谱图如图8所示。

由接收机功率谱图可以观测出,接收机接收到的信号功率谱带宽也接近0.5 MHz,零频处为直流,证明了接收机成功接收到发射机发送在空中的调制信号。

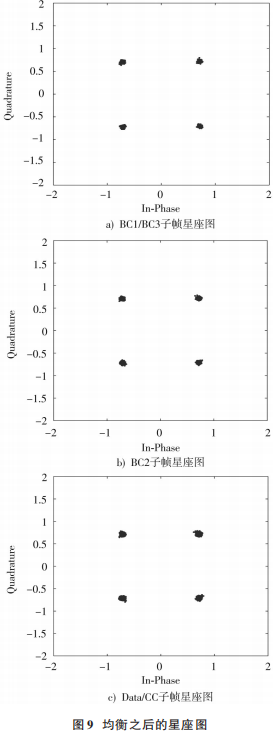

在L⁃DACS1系统前向链路发射机采用QPSK调制方式的情况下,利用子帧中的导频符号进行信道估计和均衡之后的星座如图9所示。

其中,图9a)是BC1/BC3子帧均衡后的星座图;图9b)是BC2子帧均衡后的星座图;图 9c)是 Data/CC 子帧均衡后的星座图。

由均衡之后的星座图可以观测出,BC1、BC2、BC3、Data/CC子帧的星座点收敛较好,满足设计需求。

5 结 语本文按照L⁃DACS1系统协议规定的技术参数和超帧结构,基于软件无线电Y320和Matlab设计实现了L⁃DACS1系统前向链路的发射机和接收机,并进行了发射机和接收机的联调测试。通过测试发射机和接收机功率谱图、观测星座图的收敛性,可以证明所设计的L⁃DACS1系统平台运行有效,该平台将用作后续算法研究的实际验证平台。 审核编辑 :李倩

-

接收机

+关注

关注

8文章

1182浏览量

53526 -

无线电

+关注

关注

60文章

2144浏览量

116597

原文标题:论文速览 | 基于 Yun SDR 的 L⁃DACS1系统前向链路平台的设计与实现

文章出处:【微信号:现代电子技术,微信公众号:现代电子技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于Yun SDR的L⁃DACS1系统前向链路平台的设计与实现

基于Yun SDR的L⁃DACS1系统前向链路平台的设计与实现

评论