早期集成电路设计中,工程师考虑的信号延迟主要产自于标准单元自身的延迟。然而从业界的主流工艺进入深亚微米之后:

■绕线产生的信号延迟在总占比上越来越大

■信号噪声对于芯片功能的影响也不断增加

■在高频电路中的频率变化又会改变电阻、电感值的分配

这就对于寄生参数的计算精准度有了更高的要求。伴随着工艺的不断升级,芯片规模也在不断扩大,也对寄生参数提取的效率有了更高要求。

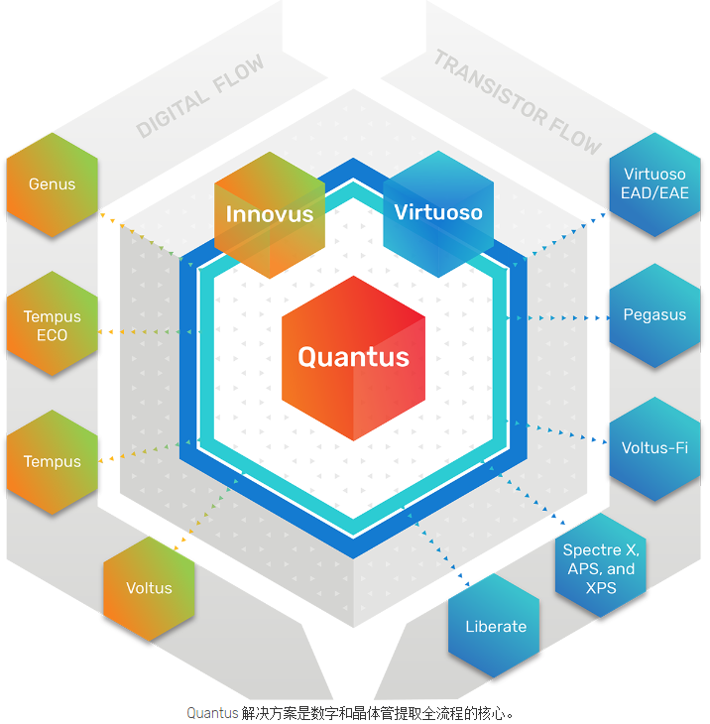

Quantus 是目前业界非常受信任的寄生参数抽取工具。在集成电路行业内,处于领先地位的制造厂商和设计公司都会大规模地应用该工具,尤其在工艺制程步入深亚微米的先进工艺领域(16 nm 及更先进的制程),Quantus 在模拟电路和数字电路上的优异表现都备受客户的广泛好评。

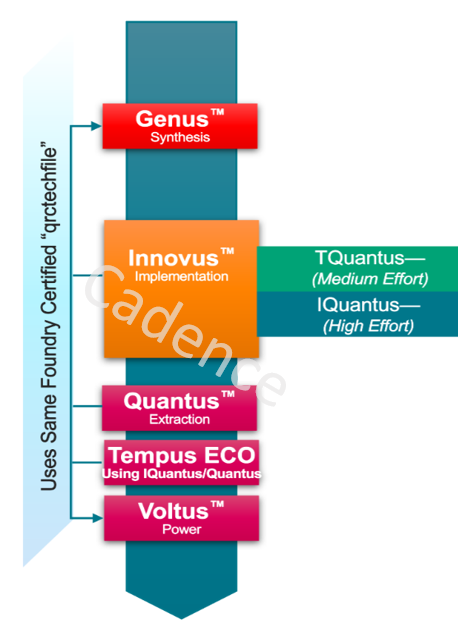

此外,Quantus 与 Cadence 的各类数字电路设计工具都有良好的集成,诸如 Genus&Innovus、Tempus、Voltus 等。工具与这些数字设计的平台的深度绑定,为客户提供了便捷和高效的体验。本文将简单介绍 Quantus 在数字电路设计上针对以上挑战的一些解决方案和应用实例。

Quantus 在数字电路设计中提取寄生的精度

Quantus 的运行速度

Quantus 与 Cadence 其它工具平台的深度集成和应用

#1

Quantus 在数字电路设计中提取寄生的精度

从 2014 年开始,Quantus 取得了具备各类先进工艺制程的制造商的认证:从最初的 16 nm、10 nm、7 nm,到目前行业内最先进的 3 nm 工艺,Quantus 在各个工艺节点上,不断得到了各个知名芯片设计公司的肯定。

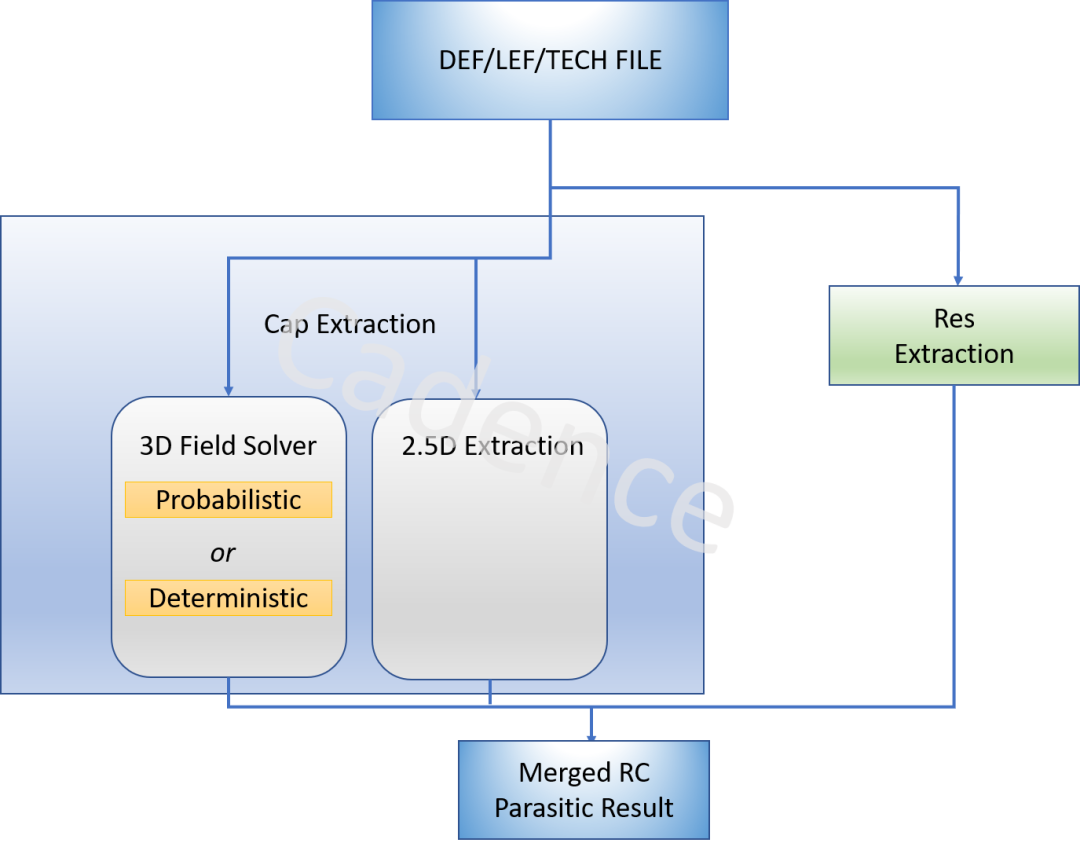

Quantus 抽取的寄生值与标准值的精度对比

在寄生抽取中,电容的计算是最为繁琐且复杂的,对此 Quantus 中内嵌的 Random-Work Field Solver (3D)引擎,经过先进工艺芯片制造商的认证,成为了寄生参数抽取中精度的标准值。不同于传统的电容系数模型匹配(2.5D)方式,Quantus FS 引擎通过 3D 场效应求解方式,直接依据版图的形状数据进行计算,从而得到完全匹配真实芯片构成的寄生电容数值。

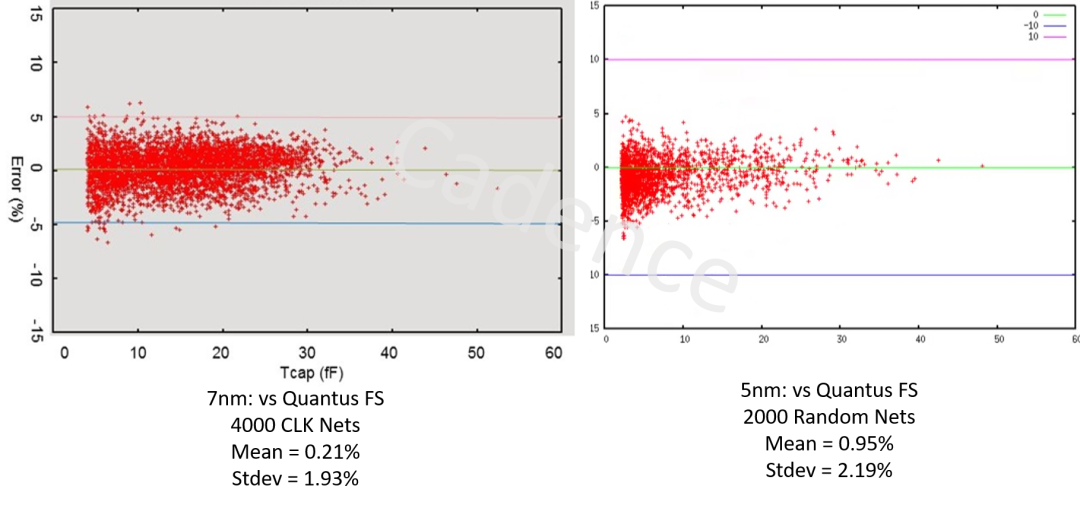

下图为全球领先的美国集成电路芯片设计公司在 7 nm 和 5 nm 的工艺节点中,对于 Quantus 精度调研的例子:通过对比 Quantus 抽取的寄生电容数值和 Quantus FS 产生的标准值可以看到,Quantus 与标准值的误差是处于制造商认可的范围内的。

下图是中国最大的通信设备制造厂商在 TSMC-OIP 2019 南京会议上做的寄生参数引擎抽取精度对比(7 nm)。可以看出 Quantus FS 和 Quantus 都有很好的收敛性。

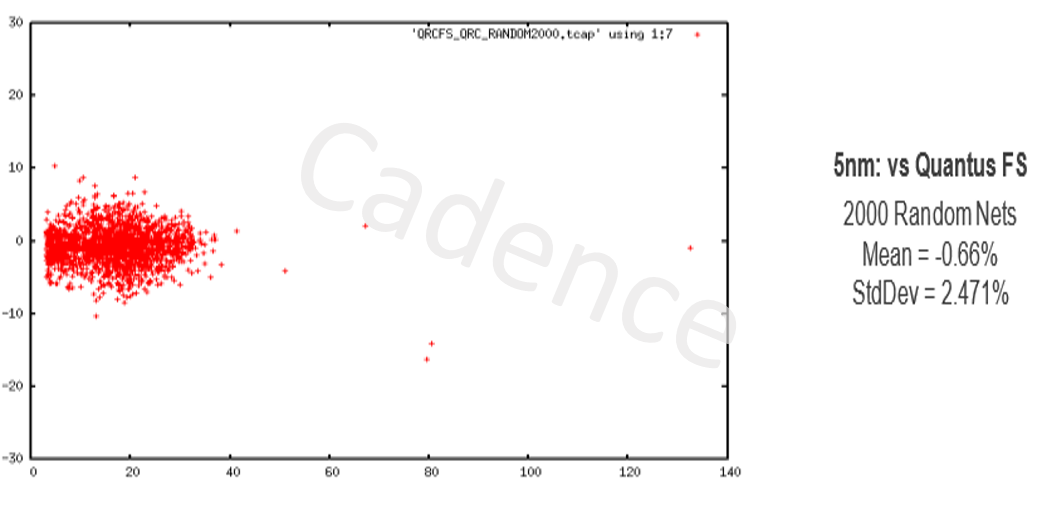

下图是中国大陆移动设备龙头公司在 5 nm 工艺节点的实际案例中的精度对比:

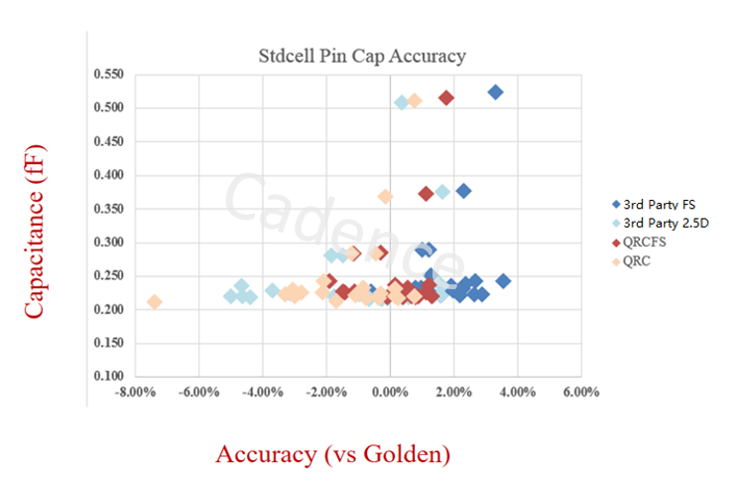

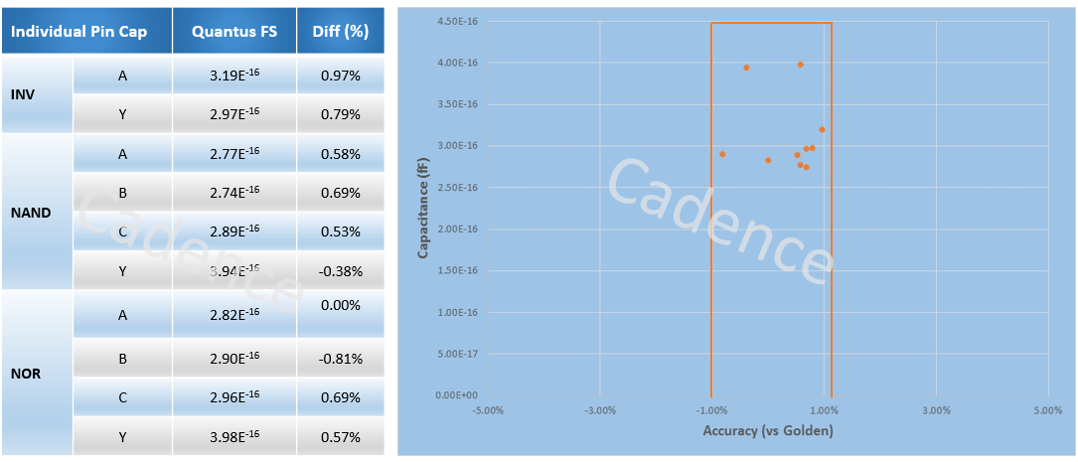

对于目前最先进的 3 nm 制程,Quantus 在寄生抽取的精度上也有良好的表现。以下图表展示的是全球最大工艺制造商在标准单元的实际分析中,对于 pin cap 的计算误差,Quantus 也可以做到在正负百分之一以内。

Quantus 在数字电路中的电感抽取

在高频的数字电路设计中,考虑寄生电感对于芯片的可靠性分析造成的影响是相当重要的。一般来说,如果时钟线的频率高于 1 GHz,单根高层时钟线长超过 1500 micron 的话,电感所造成的影响是不可忽视的,且其主要表现在以下两个方面:过冲 / 下冲(overshoot / undershoot)和时钟延迟。

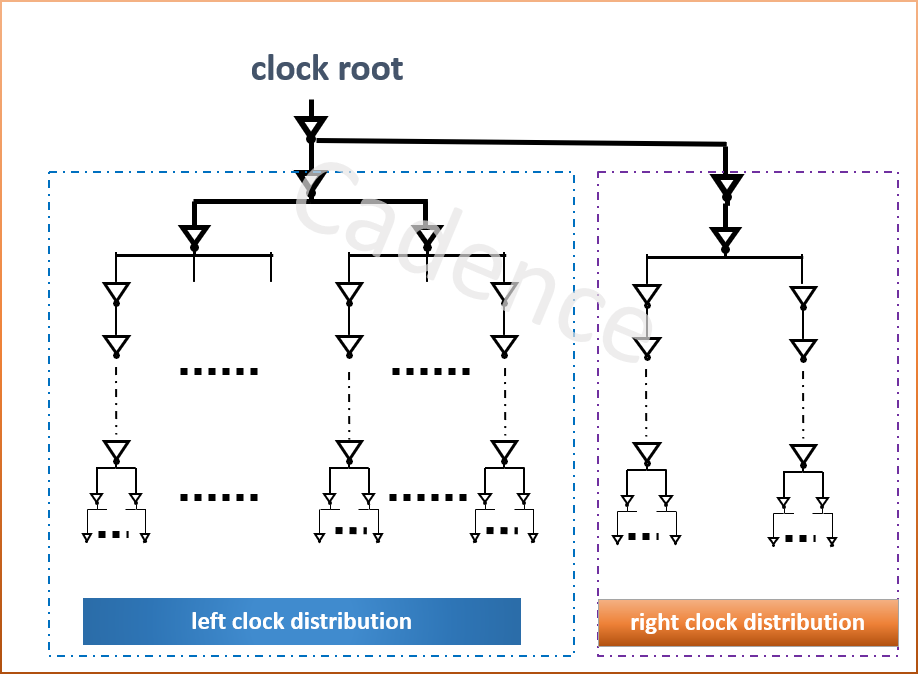

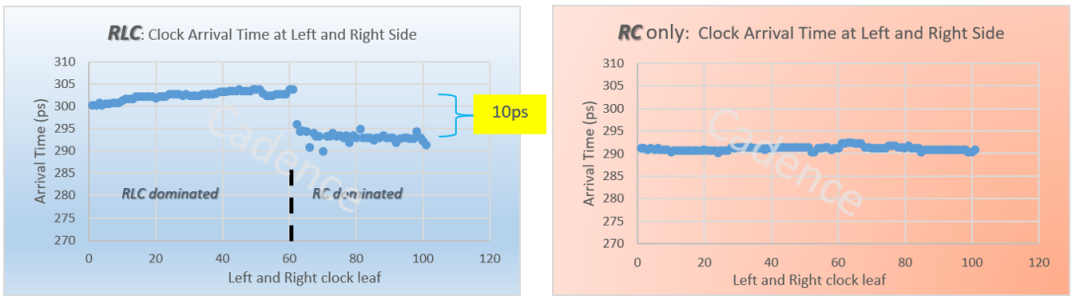

以下从客户设计的实例入手分析,左侧时钟树采用了更宽、更厚、更长的绕线,可以得到更多的时钟分布;右侧时钟树的绕线更窄、更短,能够使用的时钟分布就会偏少。

如果在分析寄生参数的时候不考虑电感效应(RC only),那么两边的时钟树在到达时间上相差无几。然而在实际分析中,客户引入 Quantus 电感抽取(RLC)的解决方案后发现:左侧时钟树的到达时间会相比于右侧,有着显著的延迟(见下图对比)。因此,如果忽略了寄生电感的影响,则有可能造成芯片在时序上的失效。

对于电感的计算可分为环路电感和区域电感,前者是人们熟知的电磁感应模型,简单却不具备通用性,而后者的计算虽然复杂,但是适用于网表中的二维节点分析,因此 Quantus 采用了后者的表达方式,将寄生电感引入到网表中。

此外,Quantus 可以支持自感和互感的抽取。采用 Partial Element Equivalent Circuit(区域电感等效模型 PEEC)的电感提取算法,可以得到区域电感的数值并融入到电路网表中,由此可以计算 90° 和 45° 的电感互联。在数字电路的电感抽取中,推荐使用的另一种模型 Ladder Network 更是可以匹配因为趋肤效应和邻近效应等造成的寄生电感。

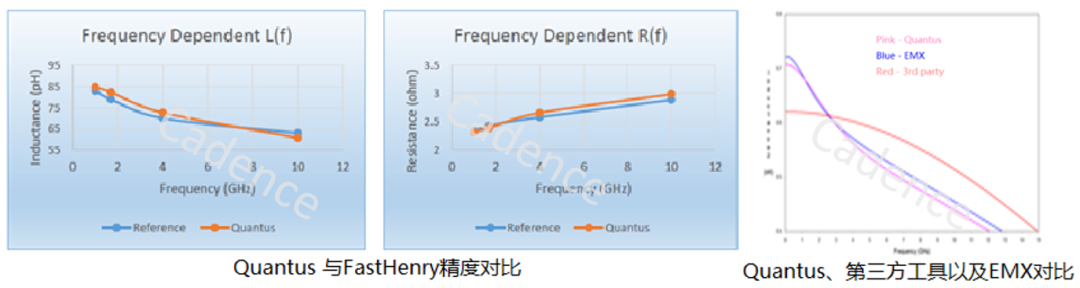

在电感提取中,业界通常认为 FastHerny 和 EMX 的结果作为标准值。通过与 FastHenry 的对比可以发现,Quantus 在高频电路中,可以很好地模拟出寄生电阻和寄生电感随着电路工作频率的增加而产生的变化。Quantus 抽取的电感精度也从实验中得到了证实:在工作频率逐渐增加的电感值计算中,Quantus 和 EMX 的结果在拟合程度上是远胜于第三方工具的。

Customer Success Story—Top 10 Semiconductor Company

#2

Quantus 的运行速度

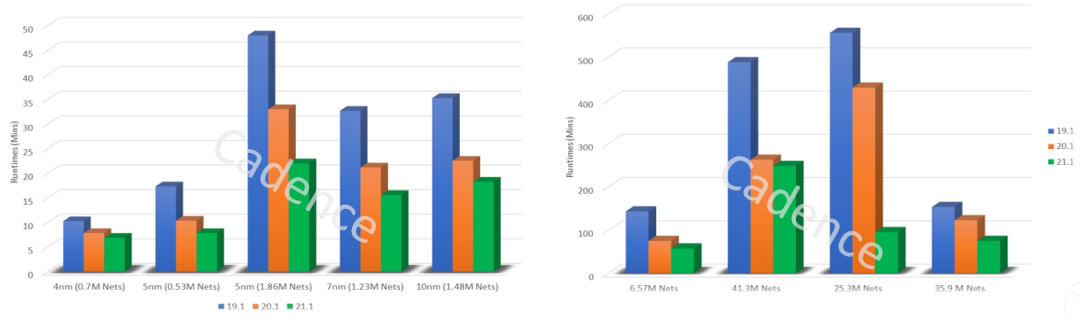

Quantus 每年发布的新版本都会比旧版本有很大的速度提升。无论是对于底层模块设计还是对于顶层的设计。在最新的 21 版本中,Quantus 的平均抽取速度要比 20 版本提高了 50% 以上,而相较于 19 版本则有 2 倍多提升。

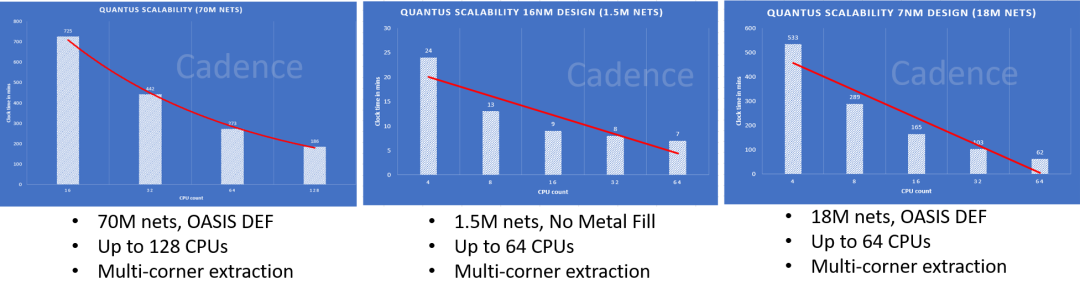

Quantus 的多核抽取方式,展现了良好的速度与线程数量的线性关系。以下为客户在先进制程中使用 Quantus 的实际例子。

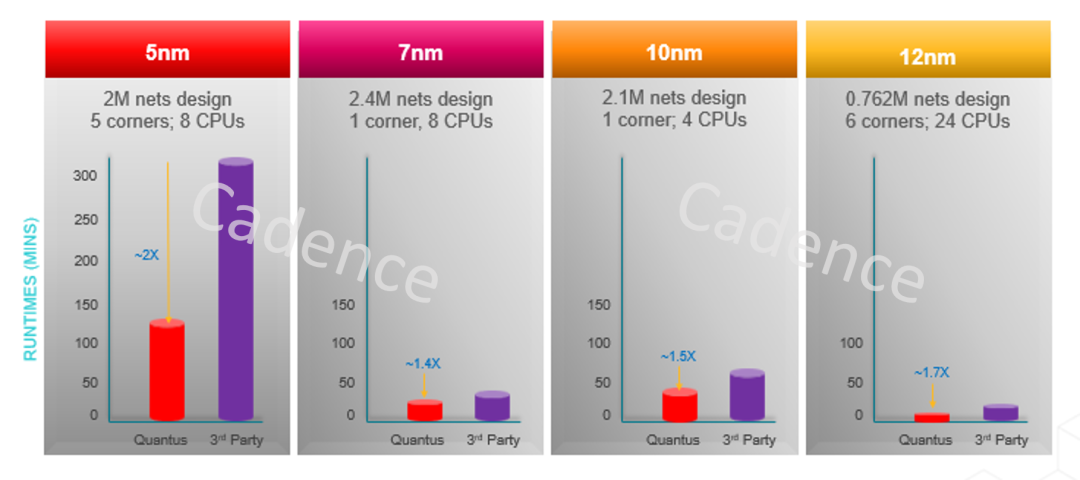

Quantus 与业内的其它抽取工具相比,在速度上也有一定的优势。以下图片展示了从 12 nm 到 5 nm 工艺制程的芯片设计中,Quantus 与某第三方工具的速度对比。

#3

Quantus 与 Cadence 其它工具平台的深度集成和应用

在后端验证工具的集成上,Quantus 与Innovus 和 Tempus 有着深度的绑定

对于 PR 工具 Innovus,时序的分析是驱动整个流程的根本,并且在不同的分析阶段,对于时序的精确度的需求也是大相径庭的。对此,Quantus 有不同的抽取引擎来提供时序分析所需的寄生参数:例如,在全局的 placement 阶段, 仅需要粗略的计算可能的寄生对时序的影响,Quantus 有对应的 TQuantus 引擎提供支持,可以快速地得到布局过程中所引起的寄生参数估计;在绕线阶段,需要依据绕线情况来提供较为精确的寄生信息,对此,Quantus 提供了 IQuantus 引擎,可以在有限的精度损失下,以较快的速度来支持 ECO 阶段的迭代分析;对于最后的 Signoff 阶段,需要使用 Quantus 的引擎来提供最精确的寄生参数分析。

在抽取引擎(preroute / postroute)的选择中,如果选择了 preroute ,则 RC 的抽取是基于绕线的密度和 net 的形状(由 early GlobalRoute 和 Clock Tree Synthesis 提供)来进行计算的,并且是不考虑耦合电容;如果选择了 postroute,则 RC 的抽取是基于绕线的间距来进行计算的,并且是考虑耦合电容的。

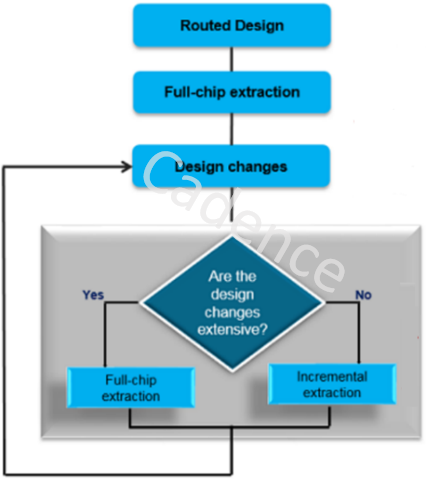

对于 IQRC 和 Signoff QRC 有两种抽取模式:全局寄生抽取模式和增量寄生抽取模式。对低于一定阈值(基于 net 数量和面积)的改动,使用的是增量寄生抽取模式,反之则会触发全局寄生抽取模式。

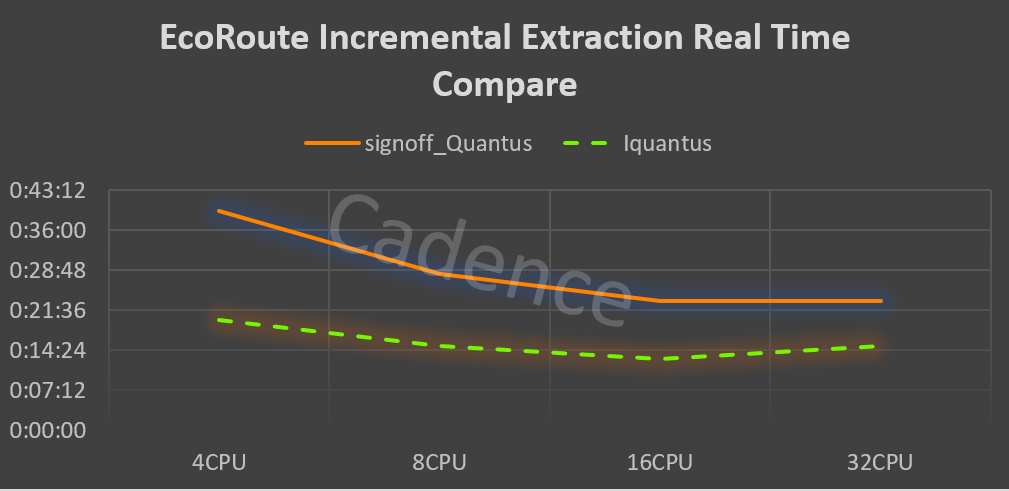

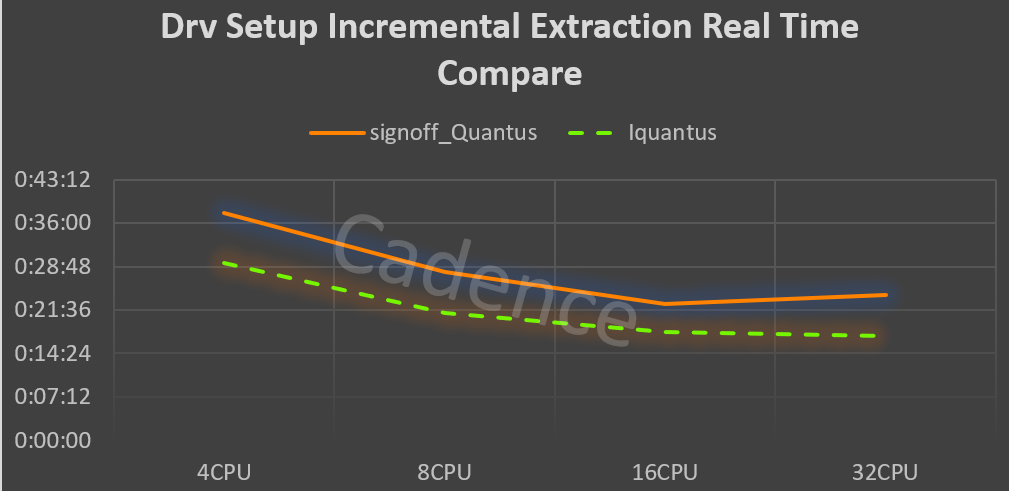

在 Innovus 中调用 Tempus 执行 ECO 的阶段,基于时序的考虑,需要对芯片设计中用到的缓冲器做优化(替换)来满足设计规则,对于这个阶段的寄生参数信息,使用增量抽取模式是最为高效的。下图比较了在该阶段中,Quantus 与 IQuantus 在其中两个步骤的运行时间,一个考虑的是缓冲器变换所引起的寄生变化,另一个则是考虑了在缓冲器更换后重新布线所引起的寄生变化。从实验结果可以看出,在增量寄生的抽取中,IQRC 有着显著的性能优势,即在 CPU 资源有限的情况下可以更好地减少运行时间。

左右滑动查看更多

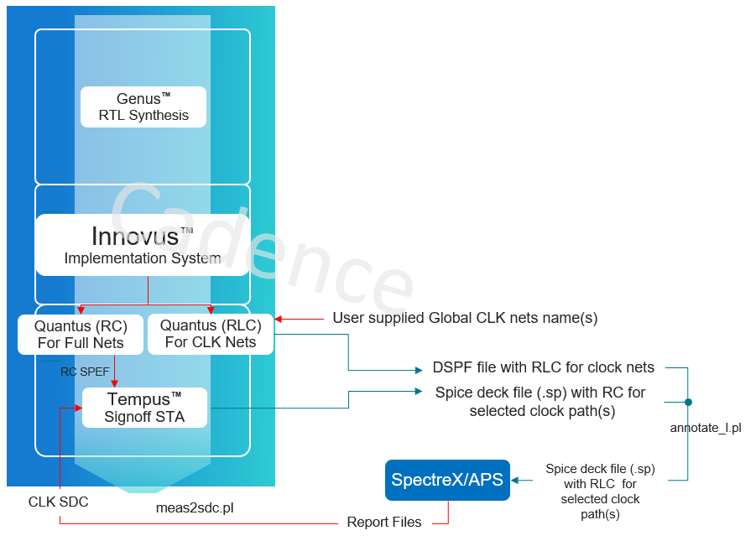

Quantus 与 Cadence 的其它平台(Spectre、Tempus)在电感分析流程上有紧密联系

用户可以通过将 Quantus 产生的带有电感寄生参数的 DSPF 网表和由 Tempus 产生的 SPICE 网表相结合,进由 Spectre 仿真,从而判断电感是否对设计造成了过冲 / 下冲 (overshoot / undershoot)的影响。同时在 Spectre 的报告文件中,可以提取出用于做静态时序分析的 SDC 文件。通过使用这个 SDC 文件,Tempus 可以做出同时基于电阻、电容、电感的静态时序分析。

综上所述,随着芯片设计更加复杂、生产工艺更加先进,寄生参数的分析对于芯片的功能性甚至成败发挥了更加重要的作用。为了解决寄生参数分析的精度以及抽取效率问题,Quantus 提供了准确、高效、完整的解决方案,为客户的芯片设计保驾护航。

-

芯片

+关注

关注

458文章

51408浏览量

428510 -

集成电路

+关注

关注

5397文章

11655浏览量

363917 -

模拟电路

+关注

关注

125文章

1577浏览量

102987 -

数字电路

+关注

关注

193文章

1630浏览量

80933

原文标题:浅析 Quantus 在 Cadence 数字设计平台中的深度应用

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Quantus在数字电路设计上面对的挑战

Quantus在数字电路设计上面对的挑战

评论