和上一篇文章介绍的cross一样,SV跳变(=>)特性也能够建模出比代码覆盖率更加复杂和丰富的功能覆盖率。

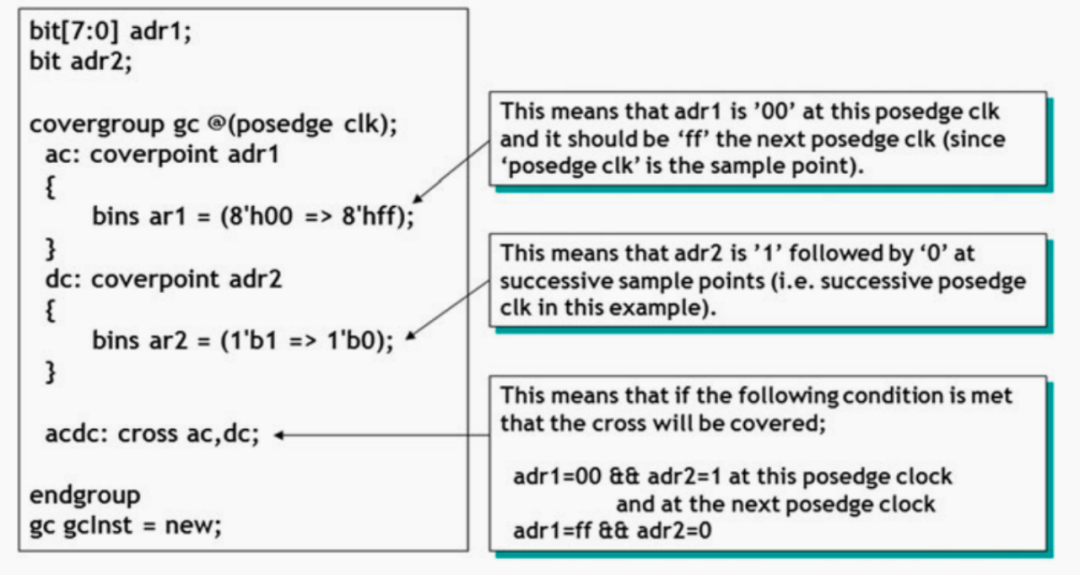

在上面的例子当中有1个跳变覆盖率coverpoint:

bins ar1 = (8’h00 => 8’hFF);

这意味着验证环境需要施加激励,让adr1在连续2个周期内从8’h00跳变到8’hff。

类似地,还有' bins ar2 ',指定了1’b1 => 1’b0的切换。

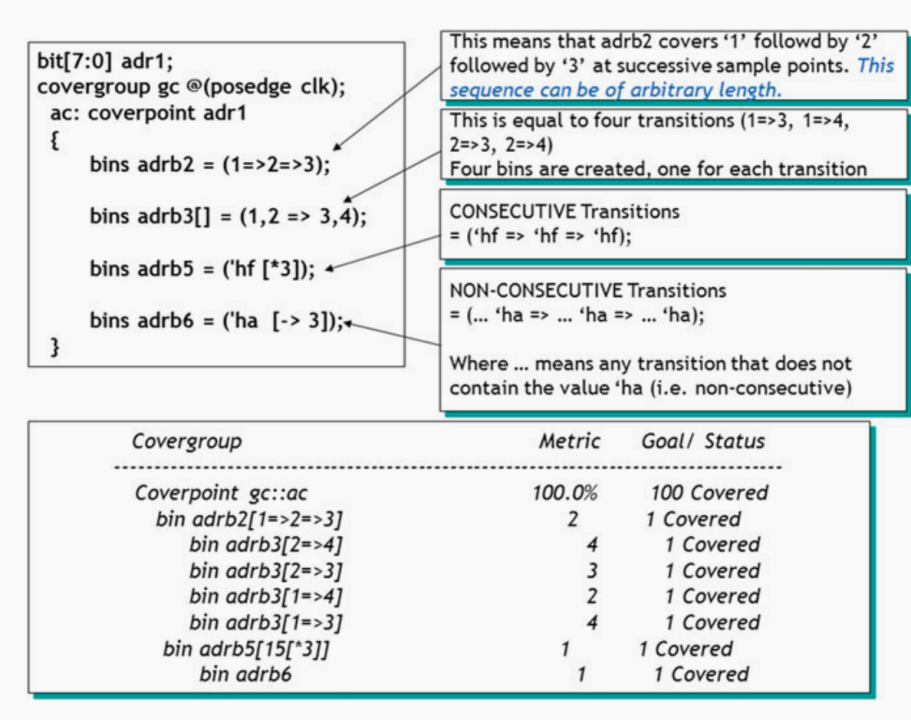

如果你希望adr1这个值能够连续3拍值f这个场景,可以使用语法

‘hf[*3]

如果不要求连续覆盖,那么可以使用语法

’hf[-> 3]

另外,注意下bins adrb3[] = (1,2=>3,4)这种写法,其实等价于

binsadrb3[]=(1=>3),(1=>4),(2=>3),(2=>4);

SV信号跳变覆盖率非常重要,因为非常多的bug都是出现在这种场景切换上的。

编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

信号

+关注

关注

11文章

2789浏览量

76720 -

代码覆盖率

+关注

关注

0文章

4浏览量

6824

原文标题:如何使用SV建模信号跳变覆盖率

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

嵌入式仿真平台SkyEye的覆盖率分析相关资料下载

代码执娜行覆盖情况的功能,来检测代码中未执行覆盖情况。在覆盖率分析时需要分析嵌入式软件的指令覆盖率、指令函数覆盖率、指令函数分支

发表于 12-17 07:27

重点厘清覆盖率相关的概念以及在芯片开发流程中跟覆盖率相关的事项

。提个小建议,即使对SV相关语法很熟悉,实现覆盖率模型的时候还是使用最直接和最简单的方式。这样可以提高可读性,便于维护和评审。03 代码覆盖率代码覆

发表于 09-14 11:57

Systemverilog覆盖率的合并和计算方式

说下sv里覆盖率的计算方式。 说明下,coverpoint有两种,1种是用户自动指定bins,另1种是系统自动生成bins。1个bin如果没有转换或者值,那么这个bin的结果会从Ci计算公式里的分母

发表于 03-21 14:24

Verilog代码覆盖率检查

Verilog代码覆盖率检查是检查验证工作是否完全的重要方法,代码覆盖率(codecoverge)可以指示Verilog代码描述的功能有多少在仿真过程中被验证过了,代码覆盖率分析包括以

发表于 04-29 12:35

•8406次阅读

USCIS API的应用程序发热覆盖率下

的建议以及分析运行过代码的覆盖率的准确性。此外,我们还尝试了自动化的一些方面,随着工具开发人员对这个重要问题的重视,它很可能在未来进行扩展。

发表于 09-15 10:53

•2次下载

IP开发时如何考虑复用覆盖率

如何在开发IP的同时去巩固集成和复用覆盖率?IP的某些功能和性能是可以配置的,需要考虑的是IP被各种合理配置后的工作是否都能够正常,将功能覆盖率先整理为层次化的抽象功能覆盖率模型,称之为cover model。

统计嵌入式代码覆盖率的方法和经验

)是软件测试中的一种度量,描述程式中源代码被测试的比例和程度,所得比例称为代码覆盖率。 在进行代码测试时,常常使用代码覆盖率作为考核测试任务完整性的指标,并且代码覆盖率也被拿来作为衡量

高覆盖率的Verilog代码的编写技巧

设计工程师需要关心的主要有行覆盖率(Block),条件覆盖率(Expression),翻转覆盖率(Toggle),状态机覆盖率。本文从ASIC设计的角度上来讨论,如何写出高

代码覆盖率工具的重要性

测试覆盖率是软件质量的重要指标,也是软件维护的重要组成部分。它通过提供不同承保项目的数据来帮助评估测试的有效性。这种洞察力允许通过为未经测试的代码定义新的测试用例来改进测试,从而提高代

如何获得100%的安全关键系统结构代码覆盖率

许多软件开发和验证工程师其实并不能真正理解获得结构覆盖率的重要性。大部分人这么做只是因为这是他们行业的功能标准所要求的,而并没有真正认真对待它。

SV建模信号跳变覆盖率的重要性

SV建模信号跳变覆盖率的重要性

评论