选择性外延工艺

通过图形化硅氧化或氮化硅掩蔽薄膜生长,可以在掩蔽膜和硅暴露的位置生长外延层。这个过程称为选择性外延生长(SEG)。

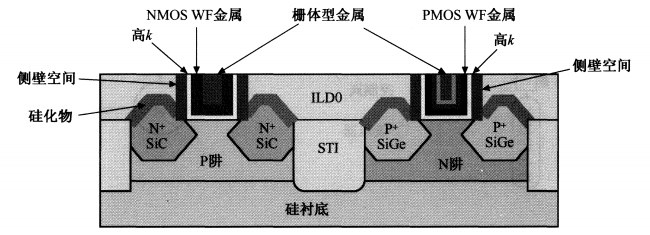

下图显示了利用SEG SiC形成NMOS拉伸应变沟道,以及利用SEG SiGe形成PMOS压缩应变沟道。

多晶硅沉积

自从20世纪70年代中期离子注入被引入IC生产中作为硅掺杂工艺后,多晶硅就作为栅极材料使用,同时也广泛用于DRAM芯片的电容器电极。

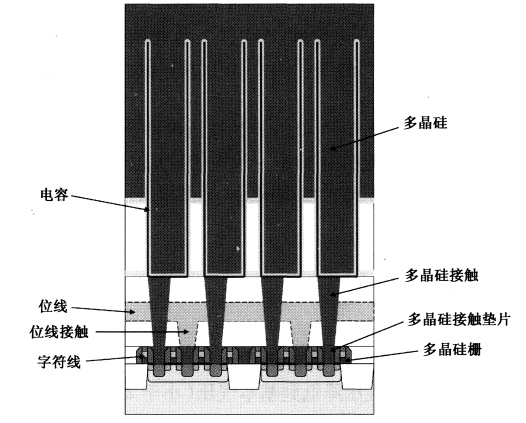

下图显示了多晶硅在先进DRAM 芯片上的应用。

硅化物叠在第一层多晶硅(Poly 1)上形成栅电极和局部连线,第二层多晶硅(Poly 2)形成源极/漏极和单元连线之间的接触栓塞。

硅化物叠在第三层多晶硅(Poly 3)上形成单元连线,第四层多晶硅(Poly 4)和第五层多晶硅(Poly 5)则形成储存电容器的两个电极,中间所夹的是高介电系数的电介质。

为了维持所需的电容值,可以通过使用高介电系数的电介质减少电容的尺寸。

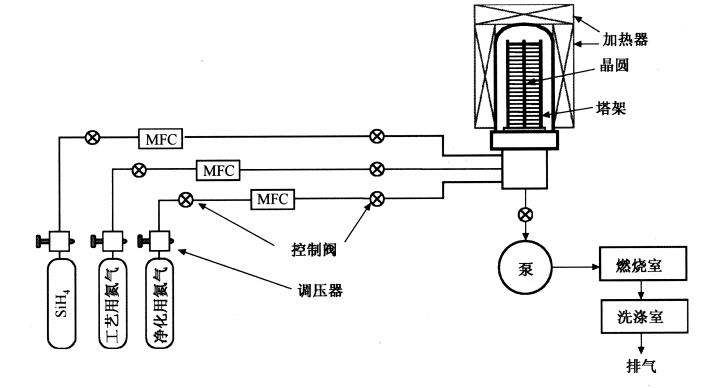

多晶硅沉积是一种低压化学气相沉积(UPCVD), 一般在真空系统的炉管中进行(见下图) 。

多晶硅沉积一般釆用硅烷(SiH4)化学反应。高温条件下硅烷将分解并在加热表面形成硅 沉积,该化学反应可以表示如下:

SiH4 --> Si+2H2

多晶硅也可以使用二氯W(SiH2Cl2, DCS)的化学反应形成沉积。高温状态下DCS将和氢反应并在加热表面形成硅沉积,DCS过程需要的沉积温度比硅烷过程高。

DCS的化学反应为:

SiH2Cl2+H2 --> Si+2HCl

通过在反应室内(即炉管中)将三氢化碑(ah3 )、三氢化磷(PH3)或二硼烷的掺杂气体直接输入硅烷或DCS的硅材料气体中,就可以进行临场低压化学气相沉积(LPCVD)的多晶硅掺杂过程。

一般情况下,多晶硅沉积是在0.2-1 Torr的低压条件及600 ~650摄氏度之间的沉积温度下进行,使用纯硅烷或以氮气稀释后纯度为20% ~30%的硅烷。

这两种沉积过程的沉积速率都在100〜200A/min之间,主要由沉积时的温度决定。晶圆内的薄膜厚度不均匀性低于4%。

多晶硅沉积过程如下:

•系统闲置时注入吹除净化氮气

•系统闲置时注入工艺氮气

•注入工艺氮气并载入晶圆

•注入工艺氮气并降下反应炉管(钟形玻璃罩)

•关掉氮气,抽真空使反应室气压降低到基本气压(小于2 mTorr)

•注入氮气并稳定晶圆温度、检查漏气

•关掉氮气,抽真空使气压回升到基本气压(小于2 mTorr)

•注入氮气并设置工艺过程所需的气压(约250 mTorr)

•开启SiH4气流并关掉氮气,开始沉积

•关掉硅烷气流并打开栅极活塞,抽真空使气压回升到基本气压

•关闭栅极活塞,注入氮气并将气压提高到一个大气压力

•注入氮气降低晶圆温度,然后升起钟形玻璃罩

•注入工艺氮气并卸载晶圆 •

•系统闲置时注入吹除净化氮气

LPCVD多晶硅沉积过程主要由工艺温度、工艺压力、稀释过程的硅烷分压及掺杂物的浓度决定。虽然晶圆的间距和负载尺寸对沉积速率的影响较小,但对晶圆的均匀性相当重要。

多晶硅薄膜的电阻率很大程度上取决于沉积时的温度、掺杂物浓度及退火温度,而退火温度又会影响晶粒的大小。

增加沉积温度将造成电阻率降低,提高掺杂物浓度会降低电阻率,较高的退火温度将形成较大尺寸晶粒,并使电阻率随之下降。

多晶硅的晶粒尺寸越大,其刻蚀工艺就越困难,这是因为大的晶粒尺寸将造成粗糙的多晶侧壁,所以必须在低温下进行多晶硅沉积以获得较小的晶粒尺寸,经过多晶硅刻蚀和光刻胶剥除,再经过高温退火形成较大的晶粒尺寸和较低的电阻率。

某些情况是在450摄氏度左右沉积非晶态硅后再进行图形化、刻蚀及退火,最后形成具有更大、更均匀晶粒尺寸的多晶硅。

审核编辑:刘清

-

电容器

+关注

关注

64文章

6970浏览量

108484 -

DRAM芯片

+关注

关注

1文章

89浏览量

18936 -

PMOS

+关注

关注

4文章

273浏览量

31714

原文标题:半导体行业(一百三十三)——加热工艺(十四)

文章出处:【微信号:FindRF,微信公众号:FindRF】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体选择性外延生长技术的发展历史

选择性焊接的工艺流程及特点

PCB选择性焊接技术介绍

PCB选择性焊接技术详细

PCB选择性焊接工艺难点解析

深度解析PCB选择性焊接工艺难点

PCB选择性焊接工艺难点解析

PCB板选择性焊接工艺

PCB选择性焊接的工艺特点及流程

半导体前端工艺:刻蚀——有选择性地刻蚀材料,以创建所需图形

半导体之选择性外延工艺介绍

半导体之选择性外延工艺介绍

评论