某年某月某日

我在知乎看到了多bit信号跨时钟的问题,于是整理了一下自己对于跨时钟域信号的处理方法。

1,fifo

数据的话,直接用fifo

2,使用赛灵思原语XPM(Xilinx Parameterized Macros)

打开vivado -- tools -- language_templates,里面直接搜索XPM,相关的原语里会注释相应的用法和参数配置,对于不同场景的跨时钟,有不同的原语。

同步复位,XPM_CDC_SYNC_RESET

异步复位,XPM_CDC_ASYNC_RESET

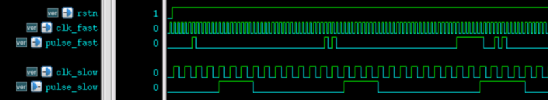

脉冲信号,XPM_CDC_PULSE

单bit信号(电平信号),XPM_CDC_SINGLE

单bit信号数组,xpm_cdc_array_single

(这个用得较多,官方说数组的每1bit需不相关,即可以把多个不相关的单bit信号拼起来,用一个原语,甚至可以是上百bit位宽。

除了不相关的单bit信号,同一个多bit信号我也经常使用此原语,这种信号一般是跨时钟域的参数,在下发后保持不变,这样有助于时序收敛。)

格雷码同步器,利用了格雷码单次只能跳变1位的特性,要求输入的数据是累加1或者累减1的数据,本质上是单比特跨时钟域处理,xpm_cdc_gray

握手机制的跨时钟域总线数据同步,XPM_CDC_HANDSHAKE

3,只要是正确处理了跨时钟域的问题,也可以不用xpm,直接使用set_false,但xpm是赛灵思官方认可的跨时钟处理,处理后不会有时序问题出现在时序报告中。

-

数据

+关注

关注

8文章

7221浏览量

90128 -

时钟

+关注

关注

11文章

1756浏览量

132146 -

XPM

+关注

关注

0文章

12浏览量

8710 -

时钟域

+关注

关注

0文章

52浏览量

9609

原文标题:vivado时序-多bit信号跨时钟域

文章出处:【微信号:FPGA通信小白成长之路,微信公众号:FPGA通信小白成长之路】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

看看Stream信号里是如何做跨时钟域握手的

基于FPGA的跨时钟域信号处理——MCU

关于跨时钟域信号的处理方法

关于跨时钟域信号的处理方法

评论