摘要:在高性能计算环境中,MPI应用多个计算节点同时访问底层存储系统文件时,其I/O开销受到访问模式和外存设备性能的影响。针对MPI应用访问文件的特征,利用非易失内存高带宽、低时延、可字节寻址、数据可持久化等优势,提出面向非易失内存的MPI-IO接口优化方案;对文件数据建立分布式的缓存并维护持久性的元数据、对进程间数据传输策略进行优化,使应用可以有效管理、利用非易失内存设备,保持缓存数据一致有效。

为了实现 对非易失内存的管理与利用、对文件数据缓存的管理与访问,本文设计并实现了面向非易失内存的MPI-IO接口优化(NVMPI-IO)。本文的工作主要包括:

● 修改MPI-IO接口,截取应用对底层共享文件系统的访问,并将其转化为对计算节点内或计算节点之间的非易失缓存的访问;

● 在非易失内存中建立并维护缓存数据,使计算节点之间的缓存一致且有效,使应用失效重启后可以快速地从非易失内存中恢复有效数据;

● 通过多种优化,降低维护、访问缓存的开销;

● 最后给出一个原型系统,并对其进行实验,实验表明,此系统可以有效地管理、应用非易失内存,并使MPI应用获得性能提升。

使用NVMPI-IO,MPI应用无须进行修改,即可通过MPI-IO中间件将非易失内存作为数据缓存,实现对文件缓存的分布式访问,从而减少I/O开销,并减轻共享文件系统的负载;同时,在非易失内存中维护元数据,使程序在崩溃重启后可以快速恢复数据,并继续运行。

MPI应用的文件访问模式

MPI是基于消息传递的并行编程模型,可使多个节点中的多个进程合作完成同一个计算任务,达到并行加速的目的。

MPI被广泛地应用在科学研究与工程仿真中,常见的MPI实现包括Intel MPI、OpenMPI、MPICH等。使用MPI的应用在访问文件时显示出以下访问特征。

● 多个进程同时访问同一文件的不同部分。研究物理模型或工程结构的MPI应用在进行计算前,首先需要准备模型文件,多个进程将同时利用模型文件上的数据进行计算,如每个进程读取多维矩阵的不同部分;进程间按需通信,并将计算结果写回文件的相应位置。

● MPI-IO使用聚合I/O与数据筛选技术,将多个进程需要的大量小粒度数据聚合成少量的大粒度数据,避免了小粒度的文件数据访问。

● MPI标准不对文件数据进行缓存。MPI应用在访问文件时可能对同一文件进行多次读写,且每次读写的位置可能不一致;同时,多个进程对文件的并行访问容易使节点内缓存失效;内存的空间有限,而工程模型的数据量可根据工程的精度呈指数型增大,将大量的文件数据缓存到内存可能影响计算效率;在允许直接输入输出(direct I/O)的文件系统(如XFS、Lustre)中,MPI建议使用直接输入输出,以避免操作系统的缓存。

● MPI应用应周期性地写出检查点(checkpoint)文件。大型工程仿真项目可能需要多个节点同时长时间运行,若其中某个节点出现故障导致作业失败,仿真项目需要重新进行;为了避免过多的重复工作,MPI应用应周期性地输出检查点文件,若作业失败,则从最近的有效检查点开始继续计算。同时,检查点文件可用于仿真的可视化输出。写检查点文件时,进程需要暂停计算任务,或将文件数据复制一份,以避免数据不一致。

● MPI应用多进程对文件进行访问有显著的同步特性。数据库、文件系统等会在任何时间点接收来自多个客户端的数据请求,若有分布式的缓存,则需要随时保证数据的一致性;MPI应用的多个进程在访问同一文件时,多个进程同时访问数据,当这一阶段完成后,进程之间需同步进度后再进行下一阶段的访问。MPI应用多进程的同步避免了写后读等数据不一致的问题,可用于简化缓存的设计。

基于上 述的MPI应用的 数 据 访问特征,在计算节点上部署非易失缓存有利于MPI应用的性能提升。利用非易失内存容量大、带宽高、可按字节寻址等特点,在非易失内存上部署缓存层不占用高效的DRAM空间,并将缓慢的文件访问转变为高速的非易失内存访问,可提高MPI应用的性能,同时可减少底层文件系统的负载。

面向非易失内存的MPI-IO接口优化被应用在HPC系统中,其修改MPI-IO模块接口以管理非易失内存的空间及访问形式。NVMPI-IO在MPI运行时初始化,并向操作系统申请NVM空间,当作业结束后释放NVM资源,使NVM资源可供其他应用使用。NVMPI-IO采用简单而有效的方法获得了以下优点。

● NVM设备的非独占使用:NVMPI-IO在运行时,只按需占用NVM的部分空间,其他应用仍可以使用该设备进行其他作业。作业 结 束后,NVMPI-IO立即释放NVM资源,使其可以被更高效地利用。

● 数据一致性:NVMPI-IO随MPI程序的运行而运行,每个MPI进程维护文件的部分缓存数据及相应的元数据;通过维护元数据保证缓存数据的一致性。

● 后台写回:MPI应用周期性地写出checkpoint文件,引起大量的数据写回。NVMPI-IO允许数据的后台写回,可在写回过程同时进行计算任务。

● MPI应用的快速重启:若MPI应用中某个进程失效引起整个程序的崩溃,在NVM设备上仍然存在有效的数据;使用NVMPI-IO,MPI应用重启后,可以在NVM中快速恢复数据,实现快速的重启。

● 高可移植性:MPI可以在不同计算机架构、操作系统上正常工作;NVMPI-IO继承了MPI的高可移植性。同时,NVMPI-IO不修改提供给上层应用的应用程序接口(application programming interface,API),现有的MPI应用不需要做任何修改即可在此系统上运行。

NVMPI-IO部署在HPC系统中,需对HPC系统的软硬件做相应的调整。

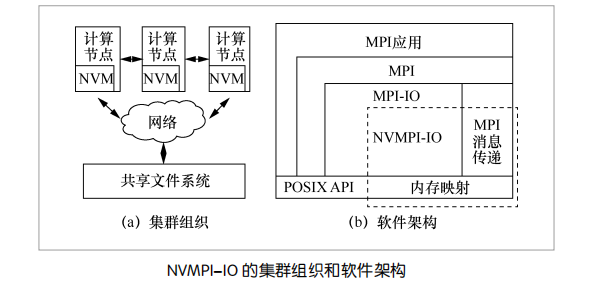

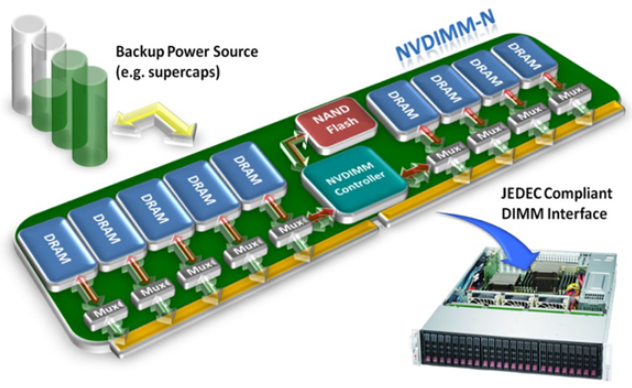

NVMPI-IO在传统HPC集群组织中引入NVM设备。在传统HPC集群中,计算节点通过网络与共享的存储系统相连,计算节点从存储系统中获得数据,并对数据进行加工处理;同时,计算节点之间通 过TCP/IP网络或RDMA技术进行通信。如图所示,NVMPI-IO在每个计算节点中部署NVM设备,同时保持共享存储系统的设计不变;节点间通信沿用传统HPC系统中的网络传输,若配备了RDMA网络,则可以使用RDMA直接访问其他节点的非易失内存。

NVMPI-IO为MPI应用服务,同时也利用了MPI定义的通信过程。一个典型的HPC应用包含多个MPI进程,其中每个进程使用MPI定义的接口与其他进程进行消息传递,使用MPI-IO模块对底层存储系统进行数据访问。本系统保留MPI-IO的聚合I/O与数据筛选优化,这些优化将上层应用需要的小粒度I/O整合成大粒度的I/O,避免了数据的小粒度随机访问。如图所 示,本系统部署在MPI-IO中间件中,截取MPI-IO对文件的系统调用,并 按 需 转发为非易失内存的数据维护、访问。

NVMPI-IO在部署时,首先需要在NVM设备上挂载可以直接访问(direct access,DAX)的文件系统。在NVM设备上挂载DAX文件系统可使应用直接通过指针 访问NVM上的数据。具体地,进程使用内存映射(memory map)技术将文件系统中的文件映射到应用的进程空间中,进程可以通 过 指针直接 修改NVM,而不是修改操作系统的内核缓存(kernel cache)。

此外,NVMPI-IO使用MPI定义的消息传递API与其他节点进行通信,使用POSIX API与底层文件系统进行数据的维护和访问。

-

接口

+关注

关注

33文章

8691浏览量

151787 -

内存

+关注

关注

8文章

3052浏览量

74260 -

数据缓存

+关注

关注

0文章

23浏览量

7133

原文标题:面向非易失内存的MPI-IO接口优化

文章出处:【微信号:AI_Architect,微信公众号:智能计算芯世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TPL1401数字电位器易失性和非易失性的区别是什么?

Cypress非易失性SRAM技术

非易失性内存有写入限制吗?

采用55纳米非易失性内存的Qorivva MCU

新型非易失存储MVM数据管理

如何设计并实现面向非易失内存的MPI-IO接口优化

如何设计并实现面向非易失内存的MPI-IO接口优化

评论