应用场景:

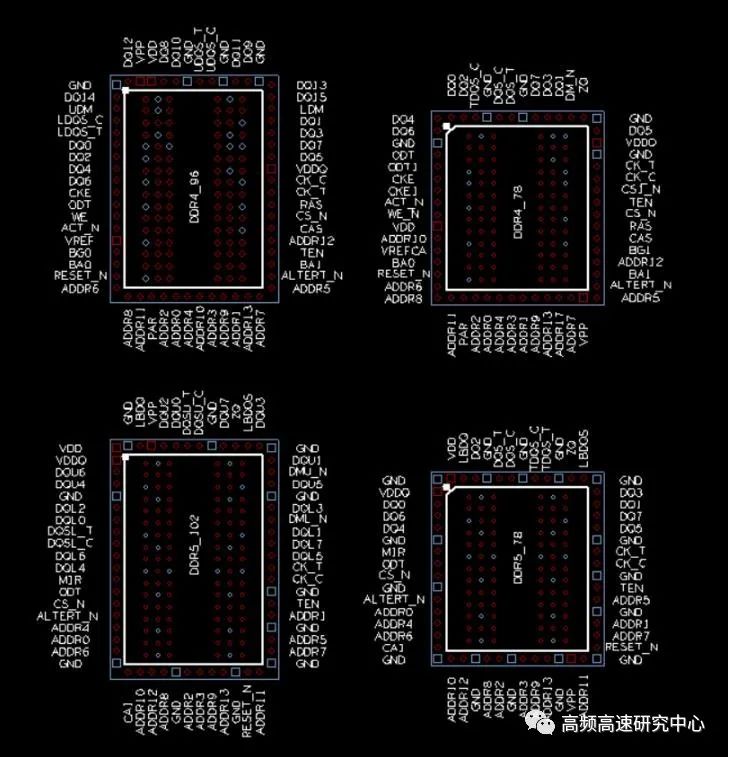

支持DDR4 DDR5的芯片颗粒测试,符合JEDEC协会规范。

主要特点:

阻抗一致性优越,体积紧凑。

极低的插入损耗。

搭配riser板可在所有硬件系统测试。

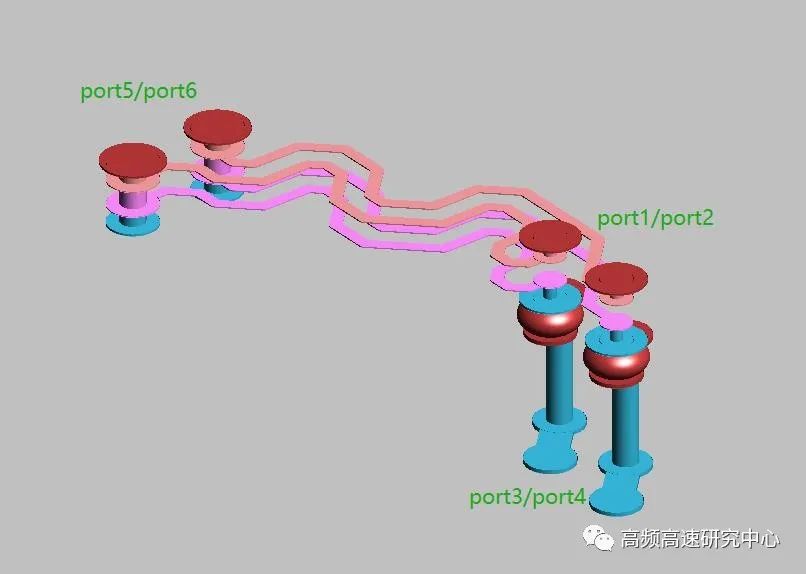

各通道skew差异小于±1ps。

8层3阶盲埋孔工艺,极限加工。

迪赛康DDR4/DDR5 Interposr测试板专门为内存颗粒测试设计,阻抗一致性优异,极低延迟,最高速率支持6.4Gbps,可以用于78pin和96pin/102pin封装的DDR4和DDR5颗粒测试。

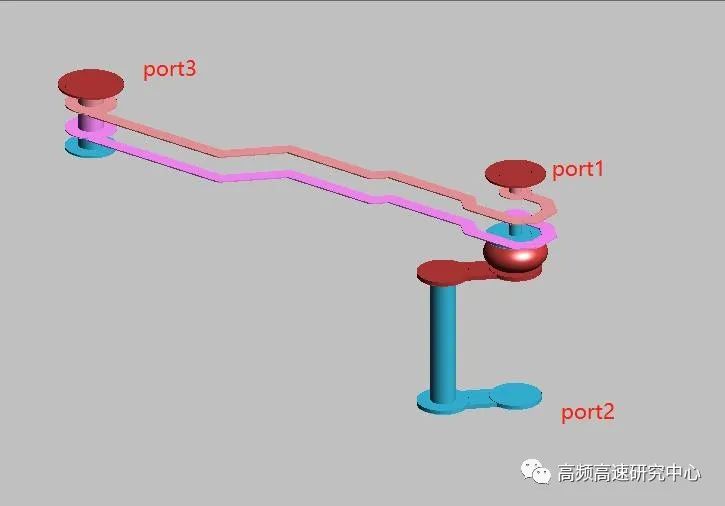

内存芯片所有信号均引出板边,包括电源和地,根据实际测试环境可选择使用增高板(Riser)避开周边干涉。

●因为走线空间狭小,所以要通过仿真精准确定层叠和走线拓扑结构

DDR颗粒的Interposer板测试一般是将DDR4或DDR5颗粒焊接在Interposer上再焊接在产品单板(根据实际情况决定是否需要增加riser板避开单板器件)后,上电可以正常开机,表示通过系统检测,然后就可以通过测试探头连接仪器对相关的信号进行测试。

审核编辑:刘清

-

连接器

+关注

关注

98文章

14476浏览量

136430 -

DDR

+关注

关注

11文章

712浏览量

65318

原文标题:【迪赛康】DDR4/DDR5 Interposer产品说明书

文章出处:【微信号:si-list,微信公众号:高频高速研究中心】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DDR3、DDR4、DDR5的性能对比

DDR4内存适合哪些主板

DDR5内存的工作原理详解 DDR5和DDR4的主要区别

如何选择DDR内存条 DDR3与DDR4内存区别

DDR4内存频率最高多少

什么是DDR4内存模块

Introspect DDR5/LPDDR5总线协议分析仪

0706线下活动 I DDR4/DDR5内存技术高速信号专题设计技术交流活动

南亚科技明年初试产DDR5内存颗粒,四款1Bnm制程DRAM产品已投产

影驰HOF PRO DDR5 7000内存详细评测报告

专门为内存颗粒测试设计的DDR4/DDR5 Interposr测试板

专门为内存颗粒测试设计的DDR4/DDR5 Interposr测试板

评论