摘要

本文介绍了运放电路共模抑制比CMRR的概念,分为运放器件自身的CMRR,还有与外部电阻搭配在一起时,整体电路的CMRR计算方法。目的是为了反映出运放器件自身的CMRR值是如何影响最终整体电路的CMRR值,还有以差分放大电路为例,阐述外部的电阻匹配程度对整体电路CMRR影响的程度。

很多用户对运放器件自身的CMRR值比较在意,实际上在外部电阻精度只有1%或者更差时,运放器件自身CMRR值对电路整体CMRR值的降低程度已经可以忽略不计了。文中还以仿真软件为例,运用CMRR定义的方法来测试电路整体的CMRR,得出本文介绍的计算方法与实测值非常吻合的结论。此方法对实际电路的测试非常具有指导意义,可以比较准确测量电路的CMRR值。

引言

在选型运算放大器时,不少工程师朋友片面追求运放器件自身的CMRR参数,而忽视了电路整体的CMRR。

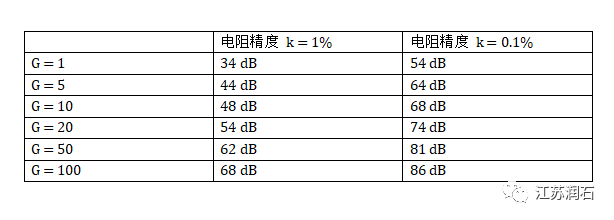

电路整体的CMRR受外部选用的电阻的精度影响更大,比如在标准差分放大电路里,运放自身的CMRR参数为100dB,电路增益为10倍时,如果选用1%精度的电阻,电路整体的CMRR只有48dB,即便选用昂贵的0.1%精度的电阻,电路整体的CMRR也只能达到68dB,都远低于运放器件自身的CMRR参数。

本文档通过理论计算和仿真证明所提供的计算方法非常准确有效,可以帮助设计者快速了解电路的整体CMRR水平。

共模抑制比CMRR的定义

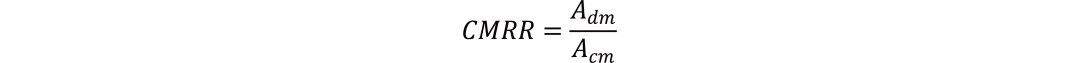

共模抑制比,定义为电路中差模增益与共模增益的比值,其公式如下:

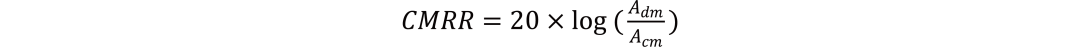

一般用对数形式来表述,定义为

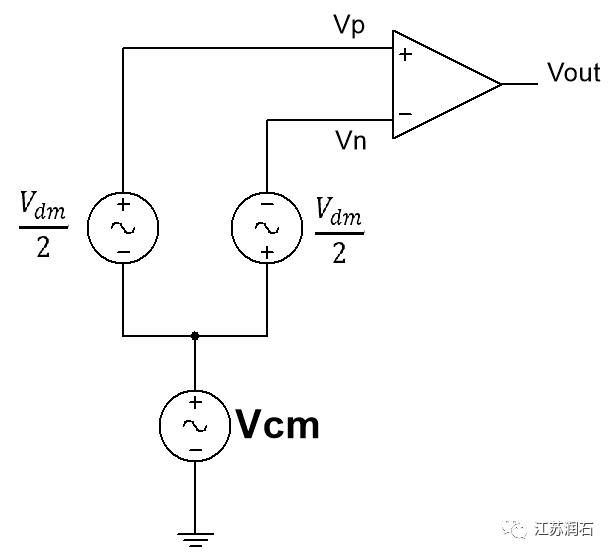

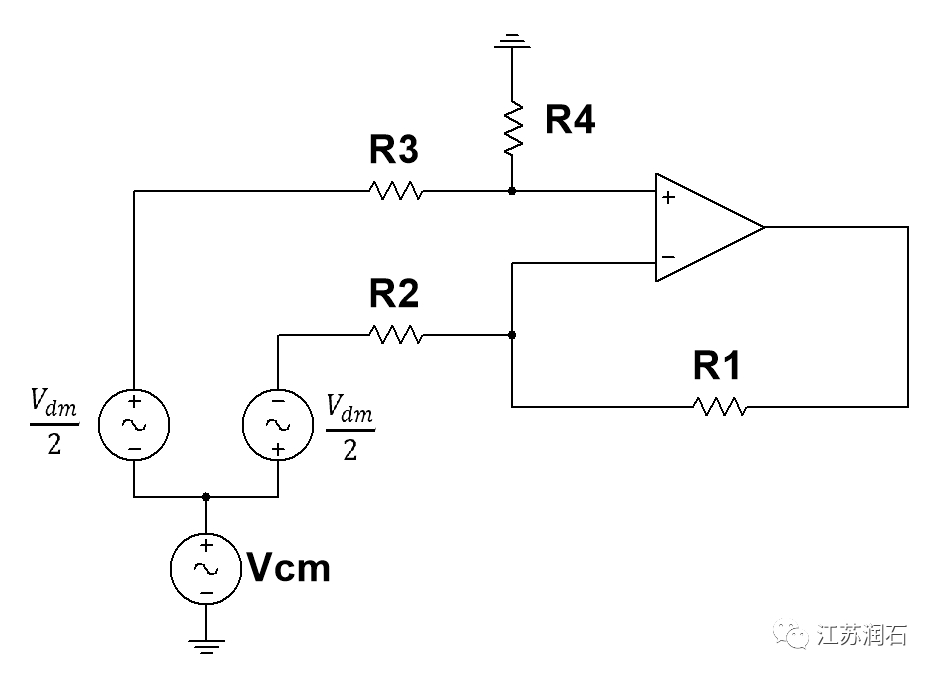

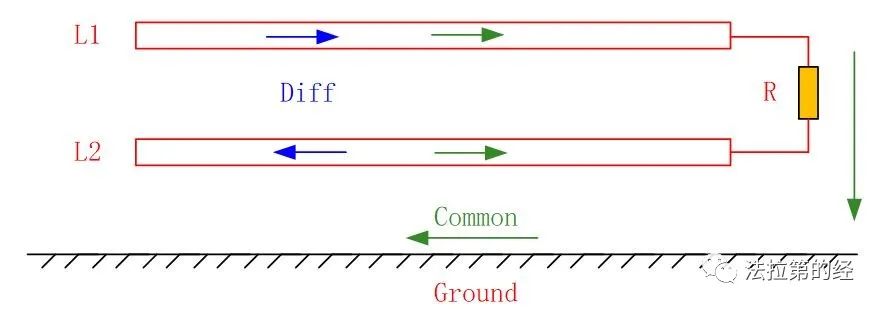

共模电压与差模电压接入电路示意图见 Figure 1:

Figure 1共模电压与差模电压示意图

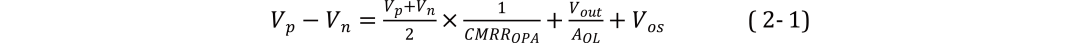

对于运放器件自身来说,简化等效模型下,其两个输入端的电压差与输出电压存在以下关系:

Vp是同相输入端电压,Vn是反相输入端电压,CMRROPA是运放器件自身共模抑制比。

AOL是运放的开环增益,Vos是运放的失调电压。

差分放大电路的共模抑制比

CMRR计算方法

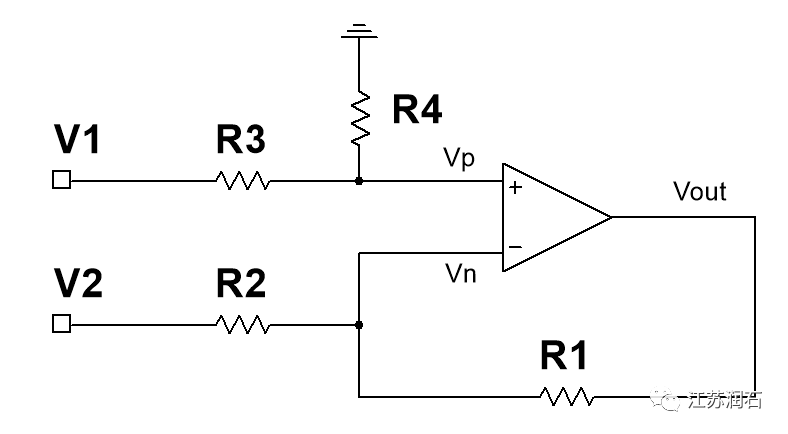

非理想运放由于共模抑制比CMRR有限,低频处CMRR值一般有80dB以上,再加上外部4个电阻的误差,差分放大电路整体的CMRR值会下降。典型的差分放大电路图如 Figure 2:

Figure 2典型的差分放大电路图

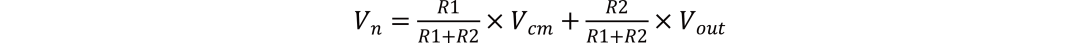

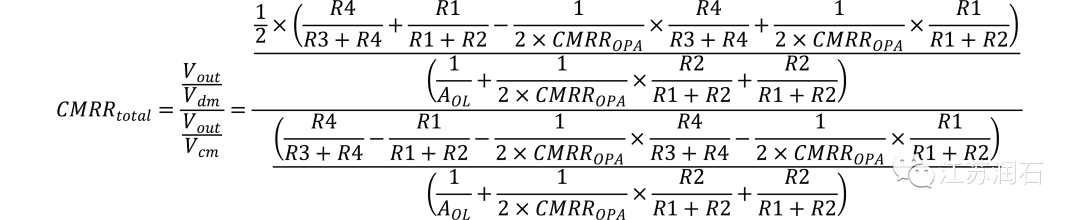

根据共模抑制比CMRR的定义,计算使用非理想运放差分放大电路的CMRR值,分为三步,第一步先计算

第二步再计算

第三步计算

1)计算电路整体Acm_total

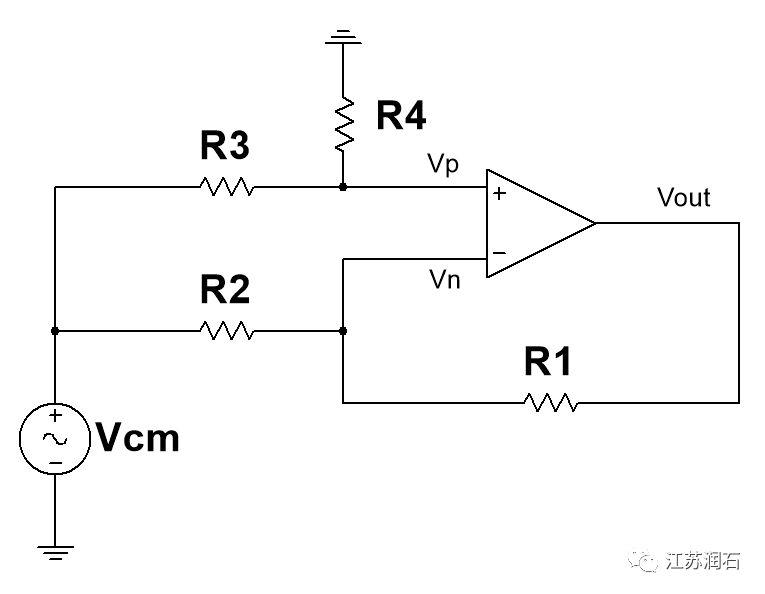

Figure 3对共模电压的差分放大电路图

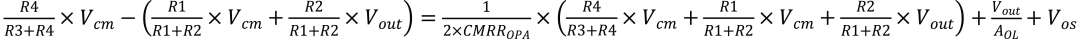

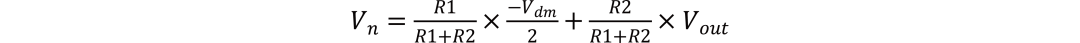

根据公式( 2-1),有

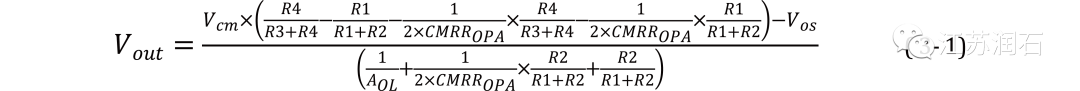

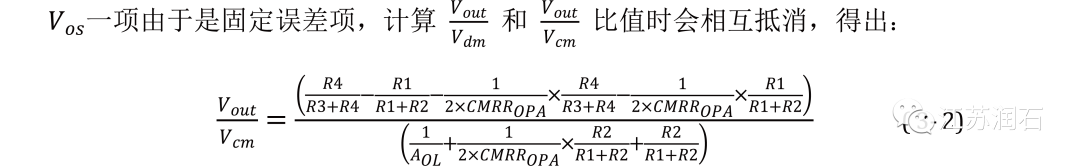

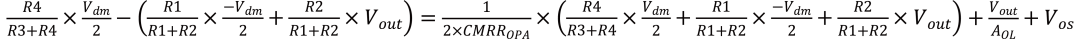

经过一系列合并同类项和化简后,得出:

此公式可以用于准确计算输入Vcm下输出的电压。

2)计算电路整体Adm_total

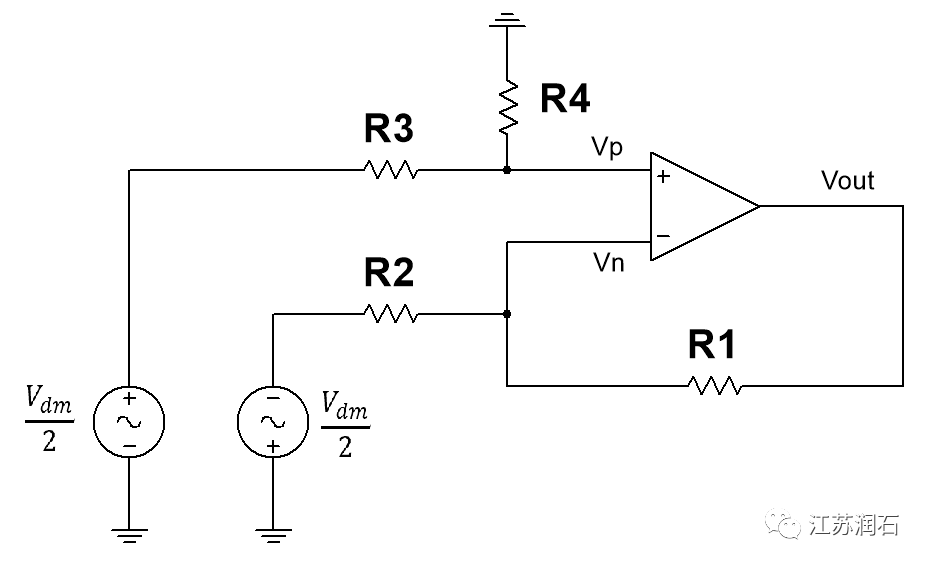

Figure 4对差模电压的差分放大电路图

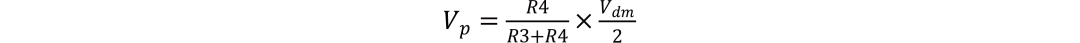

根据公式( 2-1),有

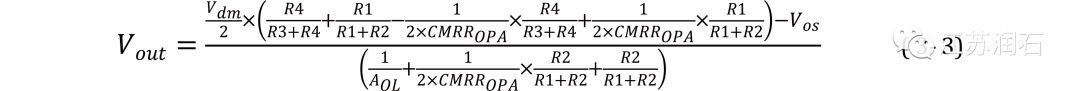

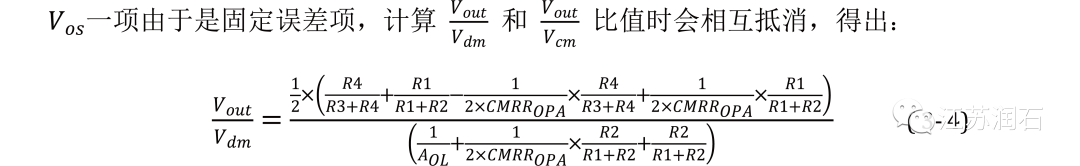

经过一系列合并同类项和化简后,得出:

此公式可以用于准确计算输入Vdm下输出的电压。

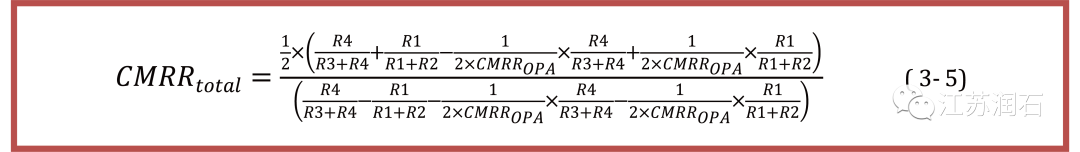

3)计算电路整体CMRRtotal

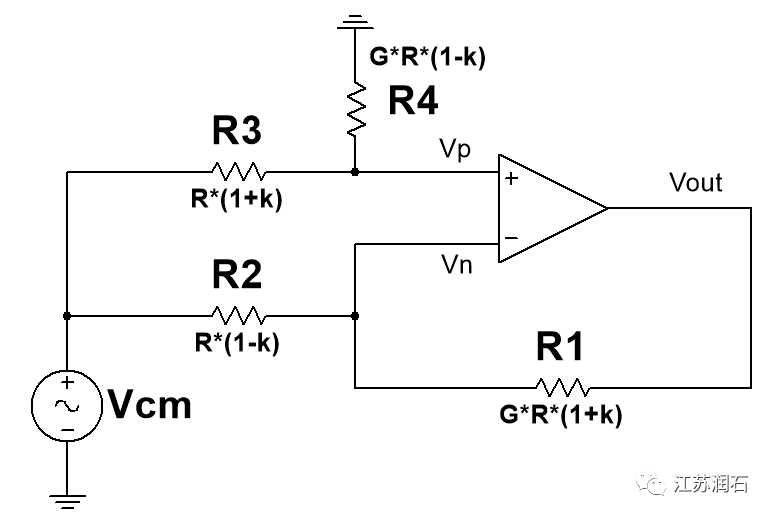

4)计算由电阻值误差引起的CMRRtotal

为了方便使用市面上常用的电阻值误差百分比来计算,

设 R1=G×R×(1+K),R2=R×(1-K),R3=R×(1+K) ,R4=G×R×(1-K) ,

此时由4个电阻引起的不平衡程度是最大的。

其中G是理论上差分放大电路的增益,K是电阻的精度。

Figure 5变更后对共模电压的差分放大器电路图

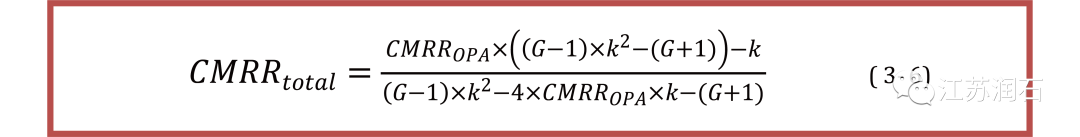

把 R1、R2、R3、R4 代入公式(3-5),并且经过一系列合并同类项和化简得,

其中,CMRROPA是运放器件自身给出的共模抑制比值,G是电路的理论增益,K是电阻的精度。

下表给出差分放大电路常见增益、电阻精度得出的CMRR值。假设运放自身CMRR =100dB。

从上表的数据可知,差分放大电路整体的CMRRtotal更多是外部4个电阻的精度来决定的,运放器件自身的CMRR值远远大于电路整体的值,所以一味的追求运放高CMRR值,而忽视了外部电阻网络精度带来的影响是不正确的。

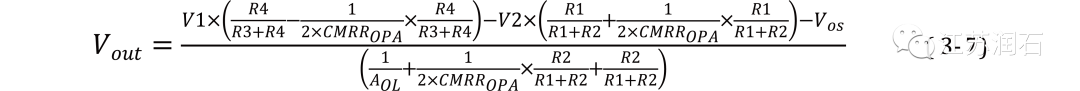

5)计算任意输入电压下的输出电压 (本节内容与CMRR计算无关,仅为展示计算Vout )

Figure 6对不同输入电压的差分放大电路图

根据公式( 2-1),得出:

其中AOL是运放的开环增益CMRROPA是运放器件自身的共模抑制比,Vos是运放的失调电压。

此公式可以用于准确计算两个输入电压V1、V2下输出的电压。

仿真验证

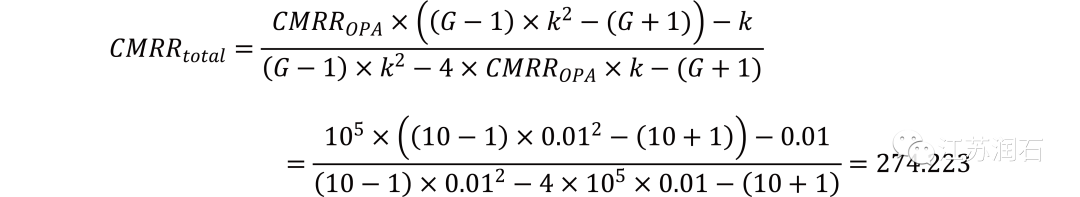

举例验证 Figure 7 电路中,G= 10,k=1%,电路整体的CMRR值。

1)理论计算电路的共模抑制比CMRRtotal

根据公式 (3-6),计算CMRRtotal

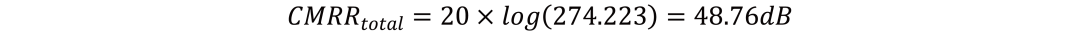

对数形式为

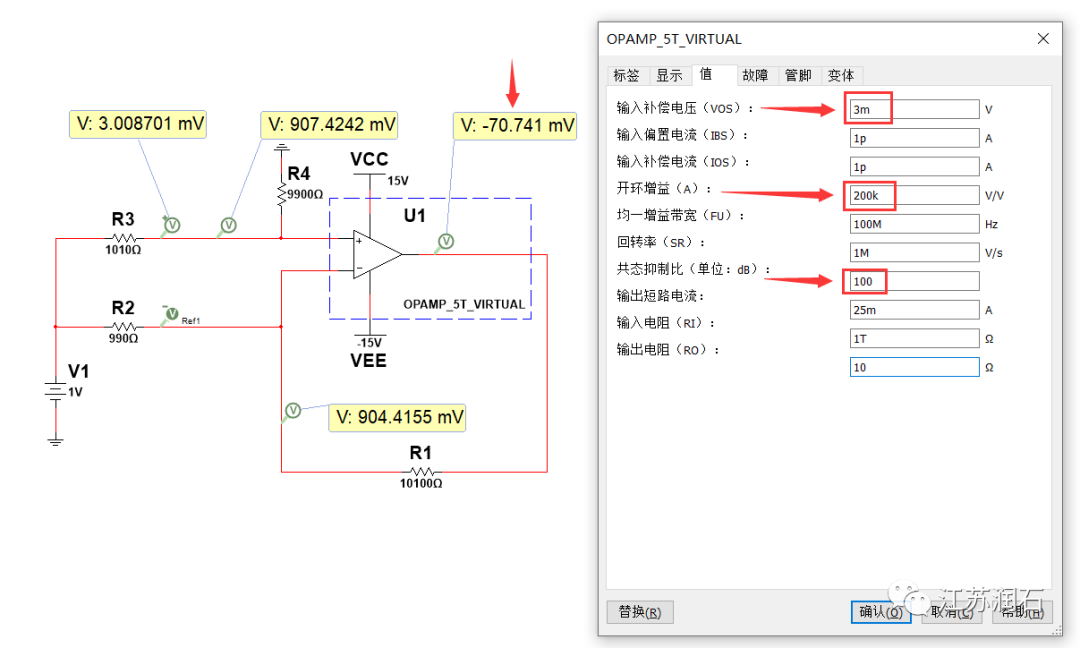

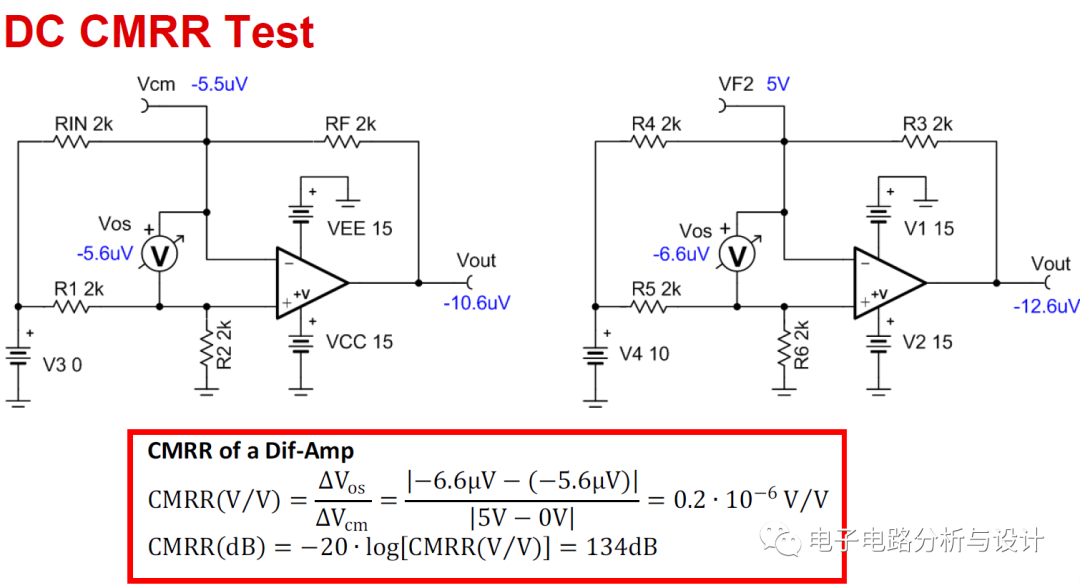

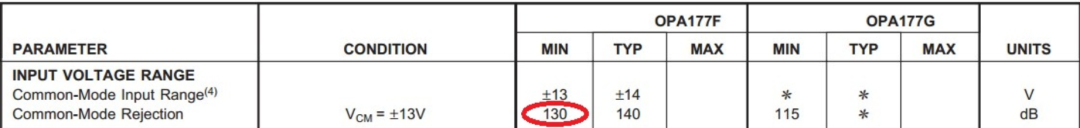

2)仿真验证电路的共模抑制比CMRRtotal

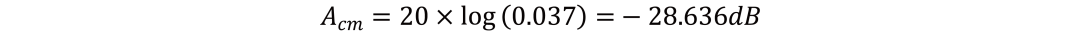

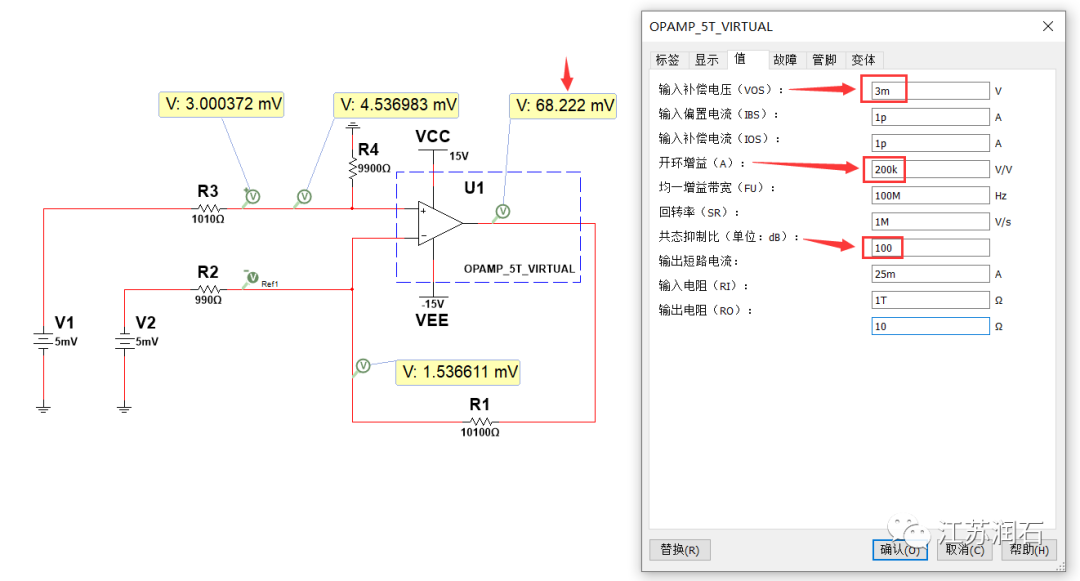

仿真软件中设置Vos=3mV,AOL=200k,CMRROPA=100dB

输入Vcm=1V ,Vout=-70.741mV仿真结果

Figure 7验证电路输入Vcm=1V时的输出电压

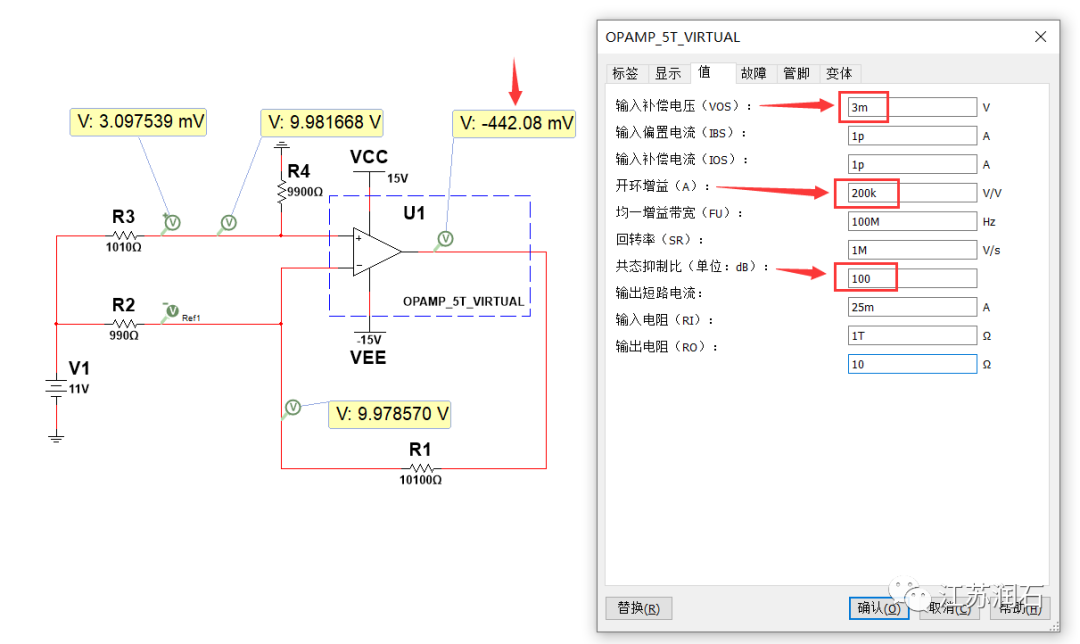

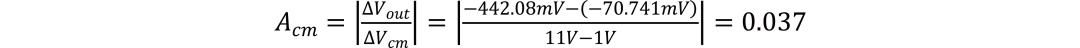

输入Vcm=11v,仿真结果Vout=-442.08mV

Figure 8验证电路输入 Vcm=11V时的输出电压

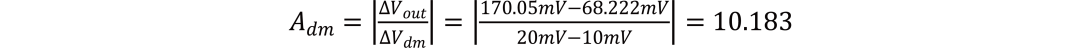

所以实测

对数形式为

输入Vdm=10mV ,仿真结果Vout=68.222mV

Figure 9验证电路输入Vdm=10mV 时的输出电压

输入Vdm=20mV ,仿真结果Vout=170.05mV

Figure 10验证电路输入Vdm=20mV 时的输出电压

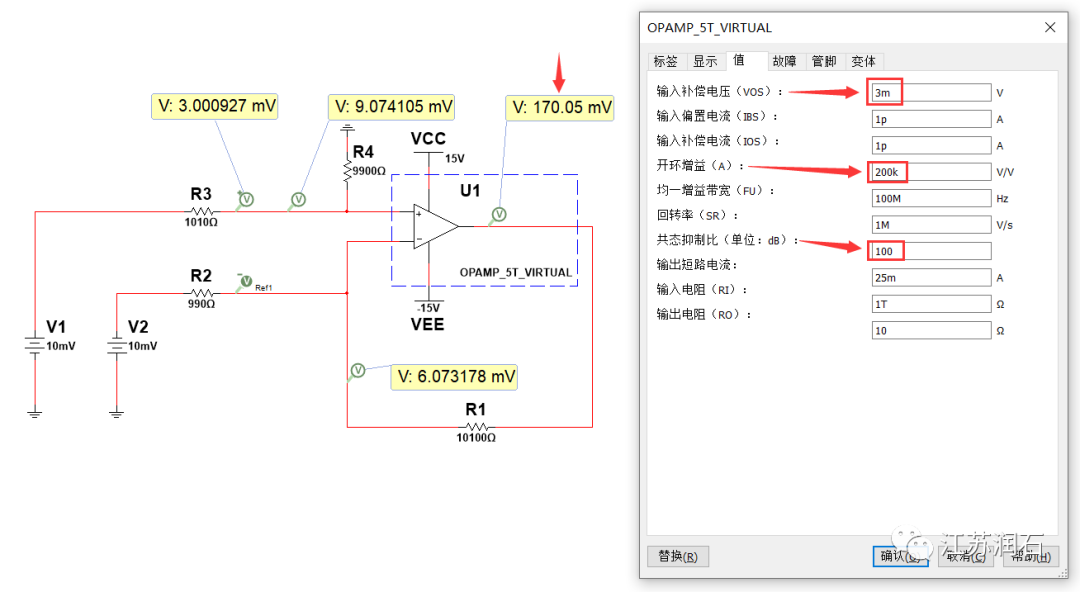

所以实测

对数形式为

实测

对数形式为

►►►

结论

通过对比CMRRtotal理论计算值(48.76dB)与仿真软件实测值(48.79dB)可知,本文档的计算方法非常准确有效,可以在短时间内帮助设计者了解电路的 CMRRtotal水平。

审核编辑:刘清

-

运放电路

+关注

关注

38文章

362浏览量

35060 -

共模抑制比

+关注

关注

3文章

82浏览量

16023 -

CMRR

+关注

关注

0文章

84浏览量

14933

原文标题:【芯知识】理解运放电路的共模抑制比CMRR

文章出处:【微信号:run-ic,微信公众号:江苏润石】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

关于运放共模抑制比的思考

关于仪表运放共模抑制比的问题

共模抑制比CMRR与电源抑制比PSRR相关介绍

求助,关于仪表运放共模抑制比的问题

放大器的共模抑制比的定义

共模抑制比,共模抑制比是什么意思

网络变压器共模抑制比CMRR概念及原理

共模抑制比CMRR与电源抑制比PSRR的仿真原理

介绍一下运放电路共模抑制比CMRR

介绍一下运放电路共模抑制比CMRR

评论