01、容差的概念

在工业生产中,通常把产品或零部件的参数(或质量特性值)的容许变化范围成为容差。在机械、电子等不同行业,产品的研发、设计、制造等环节都会涉及容差。从工程角度看,容差是实际参数值的允许变动量,这里的参数既包括机械加工中的几何参数,也包括物理、化学、电学等学科的参数。由于在生产过程中不能做到完全精确,就需要规定指标允许有一定的容许范围,这就是容差。

如手表走时的误差、产品测试过程中的设备状态参数允许变化的范围、棉纱单位面积的瑕疵点数等。

对于机械制造来说,容差通常称为公差,指允许几乎形状和尺寸的变动量,如尺寸公差、形状公差、位置公差等。

机械产品容差的目的是为了确定产品的几何参数,使其变动量在一定的范围之内,以便达到互换或配合的要求。从统计角度看,可以认为,某一指标的容许变化范围成为容差;

从设计质量角度看,容差是一种允许极限,是从经济角度考虑允许质量特性值的波动范围,它是贯穿于产品设计、制造、装配、使用与维护等整个寿命周期的重要技术信息。

02、容差在产品设计中的作用

容差有什么作用呢?对某一产品来说,若容差过松,往往生产成本较低,但产品质量与可靠性、装配性能、维修性、保障性、测试性、安全性等可能难以达到设计要求;若容差过紧,虽然质量能得到要求,但制造需要更高的要求和成本。因此,容差在质量与成本之间扮演者重要角色,在设计和制造环节之间起着不可缺少的桥梁作用,它不仅影响产品的质量与可靠性、产品功能的实现、工艺方法的选择,而且对产品的生产制造成本、使用维护成本及全寿命周期成本等产生显著影响。

21世纪的制造企业面临这全球性以知识为基础的竞争,企业必须解决缩短生产时间T、提高性能质量Q、降低制造成本C、提供优质服务S以及保持清洁环境E等问题,应保证T、Q、C、S与E的和谐统一。

一方面,产品的质量是由顾客提出的,质量工作应源于顾客需求,终结于顾客满意,制造商必须将顾客的声音(voc)贯穿于整个供应链的所有行动之中。

产品的形成过程实际上就是产品质量的形成过程,影响质量的因素贯穿于产品的整个寿命周期,包括开发研制、采购、生产、检测和测试、安装于运行、技术服务和维护等几个方面,仅对制造过程进行控制是不能保证产品质量的。

另一方面,在质量保证的过程中又要平衡相关成本。

但企业往往在质量和成本之间难以协调统一。从各个行业工程实践经验来看,设计决定了产品的固有质量和产品80%的成本。

因此,许多新的设计理念和制造模式,如六西格玛设计(DFSS)、虚拟制造、网络制造、敏捷制造、并行工程等应运而生,需要人们去探讨和研究这些新设计理念和制造模式所涉及的理念和技术问题。质量企业的立足之本,成本是生产之道,缩减成本、提高质量是现代企业管理中经常提及的目标,而容差设计的课题就是解决质量与成本之间的平衡问题。

既然容差的作用非同小可,那么,如何设计容差的问题就显得很重要了。容差设计是通过研究容差范围与产品质量、成本之间的关系,对质量和成本进行综合平衡的科学方法。工程实践与理论均表明,容差设计的好坏很大程度上决定了产品最终质量与全寿命周期成本,从而决定企业获利的情况。

因此,容差设计问题仍然是理论界应当而且十分关注的问题。

制造可靠的硬件要求你在设计阶段就应考虑所有的容差。许多参考文献讨论了由于参数偏差引起的有源器件误差,说明如何计算运算放大器失调电压、输入电流以及类似参数的影响,但是考虑无源元件容差的参考文献却寥寥无几。确实考虑了元件容差的参考文献也是从科学家的角度而不是从电路设计师的角度出发的。

然而,只要利用基本的电路公式和元件极限值来计算某个电路参数(如输出电压)在设备生命周期内在最坏情况下的取值范围,你就能够理解最坏情况的设计。最坏情况的设计允许元件数值有一个很宽的范围,由此产生多种多样的解决方案,其中有些解决方案可能是不可取的。

无源元件容差计算

电阻器是所有电子电路的基本元件,所以你应该详细地予以考虑。电阻器规定有购买容差P,你可以用百分比来度量P,常见的容差实例有0.5%、1%、2%、5%和10%。购买容差保证在你得到电阻器时其阻值在标称值之内。一只电阻器的阻值在你购买时通常接近其极限值,这是因为许多制造商在为电阻器容差严格分级时选择并消除分布中心,以便按更严格的容差等级销售。

在装配过程中,诸如焊接等外部应力都会使电阻器阻值改变。因此,在完工的装配件出厂之前,电阻器阻值变化可能会超过购买容差。因为温度、老化、压力、湿度、装配、阳光和灰尘等的外部应力都会改变元件的成分、尺寸和表面特性,所以元件值在其生命周期内会不断变化。在工作过程中元件值的变化称为漂移容差D,也以百分比来度量。

表1示出了估算的电阻器容差。注意,购买容差是与漂移容差不相关的,因为你可以通过微调来降低或消除购买容差,而漂移容差是在正常工作时发生的,除非在测量前系统进行校准,否则就会引起差错。某些电阻器的漂移容差大于购买容差。

电阻器的制造工艺和工作环境决定漂移容差。因为过大的漂移会导致废品,所以制造商们都采用稳定而可控的方法和抗漂移材料来制作容差严格的电阻器。在工厂中将漂移降低到最小的严格工艺和材料控制技术,在现场却不能将漂移降至最小。表1中的漂移容差在-25℃~+85℃的环境温度及合理外应力作用下是最坏情况的容差。除非制造商另有说明,温度漂移是不可预测的,电阻器阻值可能会由于温度的升高而增大或减小。在采用较低漂移容差之前,设计师应该向电阻器制造商咨询。

电阻器通常用R1或R2表示。遵照这个命名法,你可以用(1±T)R1来计算最终的电阻器阻值,以得到最坏情况的电阻器阻值,其中T是用小数表示的总容差。你可以使用加/减符号,因为容差的极性取决于外部条件、制作方法、材料和内部应力。你在计算时应该假设最坏情况的容差极性。你必须将各个电阻器容差表示为正的或负的,利用无论哪一个容差都能得到最坏情况的计算结果,除非数据表说明所有的电阻器都以指定的方向漂移。在计算R1=10 kΩ、容差为5%的绝对最坏情况的最大值时,你应该使用(1+0.01(5)+0.01(5))R1=1.1R1=11 kΩ。而该电阻器的绝对最坏情况的最小值为(1-0.01P-0.01D)R1=(1-0.05-0.05)R1=9kΩ。

本文没有详细讨论电容器容差的计算,你可以采用相同的方法对待电容器容差。由于各制造商用来制作电容器的方法差别很大,各类电容器之间的容差差别也比电阻器大得多。电解电容器的购买容差通常为80%,-20%,而有些玻璃电容器和NPO陶瓷电容器的购买容差则为1%。一般而言,最好将所有电容器容差增大至三倍,除非制造商的产品说明书另有不同建议。这种做法从保守的角度来看是错误的,不过在你不了解情况时就是一种很好的判断方法。

非比例计量电路

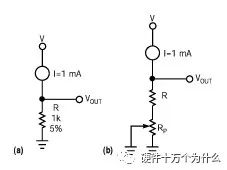

对于非比例计量电路,你必须取最大的电阻器容差,这是因为两种容差不会相消。你可以利用公式VOUT=IR来计算输出电压,式中I是一个理想的1mA电流源,而R是一个容差为5%的电阻器(图1a)。

VOUT=1mA (1±0.05±0.05)1 kΩ=(1±0.05±0.05)V。VOUT的范围为0.9V≤VOUT≤1.1V,不过,你只要利用另一个电阻器来调整初始容差,就可将VOUT的范围缩小(图1b)。

图1,非比例电路必须假设最大电阻器容差不会相消。基本的计算很简单(a),你只要增加另一只电阻器来调节初始容差,就可以缩小VOUT的范围(b)。

你可以如下计算可变电阻器阻值RP:

1、选择小于最小计算值R=0.9kΩ的最接近的十进阻值R,该值为R=0.82kΩ;

2、计算所选电阻器的最小阻值如下:RMIN=(1-P-D)R=0.9(0.82)=0.738kΩ;

3、可变电阻器RP必须补偿RMIN和1kΩ之差,所以RPMIN=1-0.738=0.262kΩ;

4、电位器的容差可能相当大,所以RP=RPMIN/(1-T)=0.262kΩ/(1-D-P)=0.262/0.8=0.328kΩ;

5、选择RP=500Ω。

最终得到的阻值为:R=820Ω,RP=500Ω。有些工程师认为,最坏情况的设计程序太严格,而且要使用的电位器阻值较大,分辨率较低,电位器漂移误差较大。有可能解决这一问题的一种方法是冒险降低电位器阻值,不过更好的解决方法是使用精度更高的部件。非比例电路必须考虑最大容差的偏移,因此,一个5%的购买容差会导致20%(±10%)的总容差。

比例计量电路

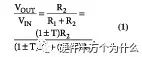

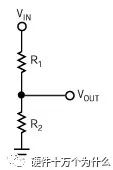

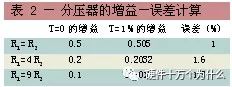

图2和公式1中的分压器是典型的比例计量电路。参照容差公式,你可以看到容差的某些部分在公式中相消。

图2,比例电路可消去电阻器阻值的某些容差。

为了得到最大增益值,你要把R2的容差设定得大,而把R1的容差设定得小。由于R2的容差大,它就以(1+T)R2的形式出现在公式的各部分中。表2以四种电阻器比例列出了理想增益、最大增益和百分比误差。要注意的是,当R1=R2时出现最小增益误差,而且该增益误差等于容差。该非比例电路必须取两倍容差,即2T,而比例电路只取容差T。

当分压器中两只电阻器的容差同时很大或很小时,两种容差就会相消。如果电阻器制造商保证在环境温度变化时所有电阻器以相同方向按比例漂移,则温度容差也会相消。

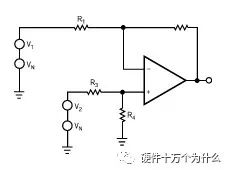

许多参考文献说,你不可能用分立元件制作一个CMR(共模抑制)良好的精密差分放大器。差分放大器的容差分析说明了为什么这种说法是正确的。考虑图3和公式2(参考文献1)中的差分放大器电路,假设该放大器是理想的。

图3,差分放大器利用比例电阻器来得到很高的CMR。

该电路的CMR是在无信号时测量的,所以V1=V2=0.0,公式2变成公式3:

当R1=R3和R2=R4时,增益为零,CMR为无穷大。实际上,电阻器容差和运算放大器误差总是将CMR限制在大约100 dB以下。将公式3改写为公式4,就使你的注意力集中到差分增益和电阻器容差上。公式4包含4个电阻器容差,因此有16个可能的误差因子。如果你研究所有的可能性,就会看到误差范围从所有电阻器容差向同一方向变化时的零一直到2T/(1-T)。

当总容差为1%(对0.5%电阻器来说,为P+D)时,电阻器容差可以导致CMR的范围从高达运算放大器极限值到低至-34.89dB。考虑到1%电阻器的购买容差和漂移容差,总的CMR可能低至-24.17 dB。你可以将这一误差作为CMR误差来计算,不过,在没有共模电压而有差分输入信号的情况下,这一误差就变成增益误差。

采用分立元件的差分放大器是难以制作和微调的,所以大多数设计师都使用具有内置微调电阻器的IC差分放大器。廉价的IC差分放大器具有高达-86dB 的CMR。

你在分析电路以确保长期性能和可制造性时,要切记无源元件具有购买容差和漂移容差,而且漂移容差可能大于购买容差。你可以在制造过程结束时微调购买容差,但是,你或你的系统只能在进行测量之前调节漂移容差。非比例电路要取两倍的电阻器容差,而比例电路可以将误差降低到容差值。精确的差分放大器难以用分立器件制造,但是具有电阻器微调和匹配功能的IC通常可以得到-90 dB的CMR。

审核编辑:郭婷

-

电容器

+关注

关注

64文章

6224浏览量

99697 -

电阻器

+关注

关注

21文章

3784浏览量

62150

原文标题:如何考虑电路设计的元件容差

文章出处:【微信号:电子汇,微信公众号:电子汇】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

通信应用中差分电路设计技术

元件容差在电路设计中的作用及考虑

元件容差在电路设计中的作用及考虑

评论