FPGA项目开发之 7 系列 FPGA 高级 SelectIO 逻辑资源

IO 灵活性是FPGA 最大的优点之一。如果我们设计的 PCB 信号走线不完美,IO的灵活性使我们能够对齐进入设备的高速数据,帮助我们摆脱困境。

设备 IO 结构中一个经常被忽视的功能是 IDELAY2 和 ODELAY2 原语。这些原语为开发人员提供了一个由 32 个抽头组成的可编程延迟线,可提供可调节或固定的延迟。

实际可用的原语取决于我们正在使用的 IO bank 的类型。High Performance IO (HP IO) 为用户提供 IDELAY2 和 ODELAY2 原语,而 High-Range IO (HR IO) 仅提供 IDELAY2 原语。

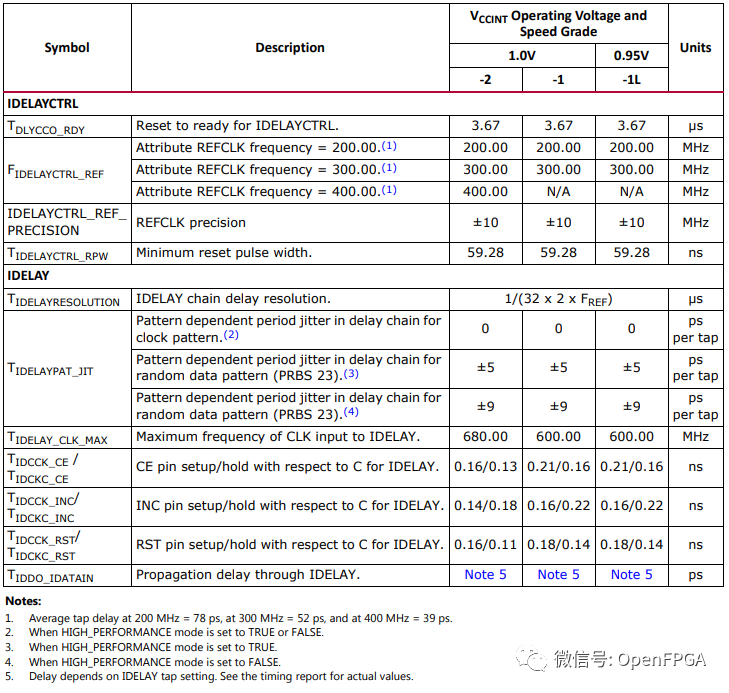

我们可以同时使用 IDELAY 和 ODELAY 来消除信号之间的小延迟。抽头之间的分辨率取决于FPGA的时钟频率和速度等级,7 系列 AC/DC 数据表如下所示:

当我们提供 200 MHz 参考时钟时,每个抽头增量都会将延迟增加 78 ps。这意味着总延迟约为 2.469 ns。

IDELAY 和 ODELAY 原语可以在四种模式下运行:

FIXED——延迟在此模式下是固定的,不能在运行时更改。

VARIABLE – 这是一个可变延迟,其中抽头值可以使用简单的界面增加或减少。

VAR_LOAD – 与变量模式类似,可以通过输入向量设置抽头延迟。

VAR_LOAD_PIPE – 这与 VAR_LOAD 类似,但是可以流水线化未来的延迟。

IDELAY2 模块能够延迟来自逻辑结构或 IO 输入的信号。

现在让我们看下如何在应用程序中实现 IDELAY 功能,并创建一个不同模式下的实例。

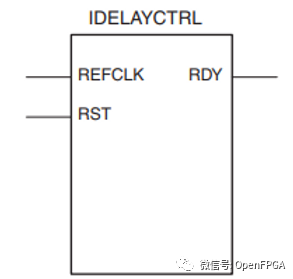

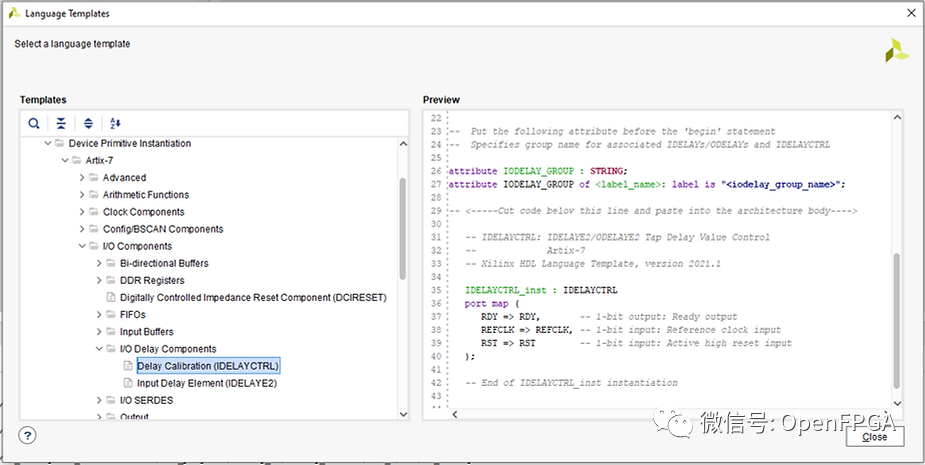

要开始使用 IDELY 或 ODELAY,我们需要实现一个 IDELAYCNTRL 模块。该模块不断校准其区域内的各个延迟抽头。该模块非常简单,需要参考时钟和复位,RDY 输出低时表示 IDELAYCNTRL 模块需要复位。

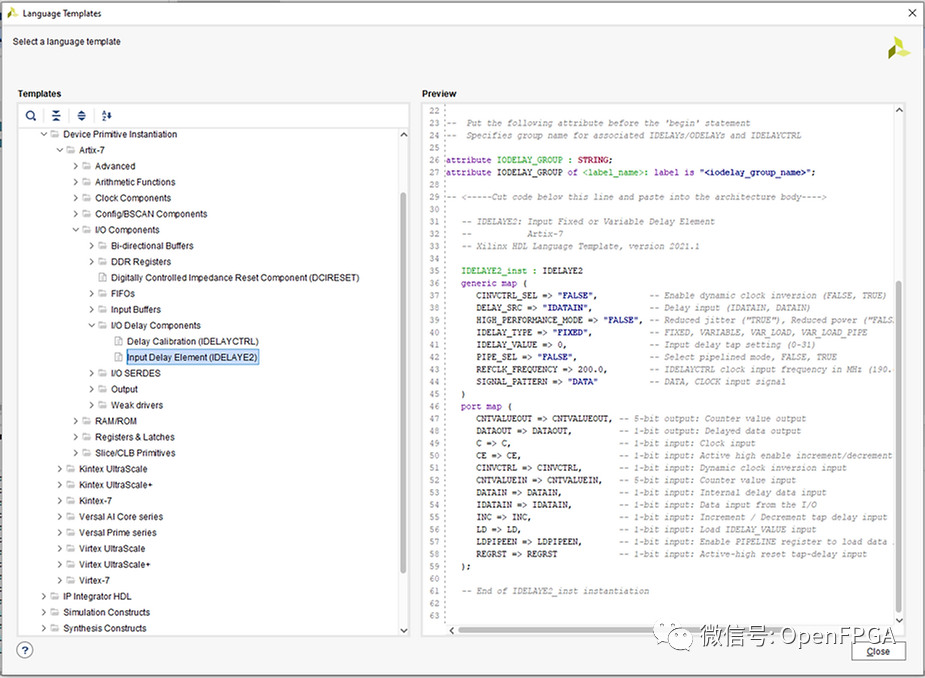

这些可以使用 Vivado 文本编辑器中提供的语言模板来实例化我们需要的模块。

我们也可以使用相同的语言模板来实例化 IDELAYCNTRL2。我们将要演示的设计将使用一个 IDELAYCNTRL 和两个 IDELAY2 原语。这就能测试不同配置 IDELAY2 时信号延迟之间的差异。

两个 IDELAY2 原语都将以 VAR_LOAD 模式运行。允许使用 CNTVALUEIN 和简单的 CE 和 INC 信号接口调整抽头延迟。

测试平台将执行以下步骤:

重置 IDELAYCNTRL。

将两个输入信号 IDELAY2 设置为 0 延迟。

设置两个 IDELAY 延迟 2,将两个信号。

将第二个 IDELAY2 延迟增加 1 ,同时将第一个 IDELAY 保留为 2。

将第二个 IDELAY2 减 1 ,让两者具有相同的延迟。

将第二个 IDELAY2 设置为具有 31 的最大可能延迟。

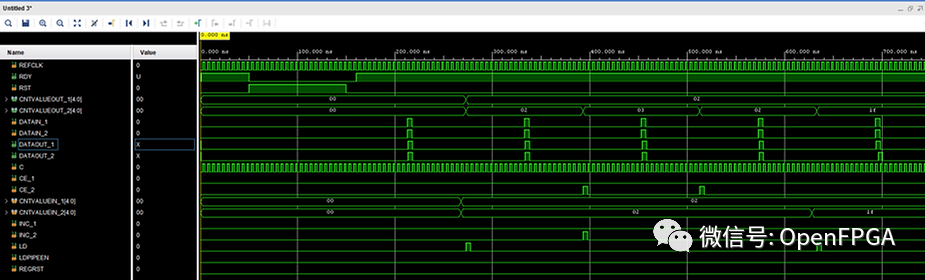

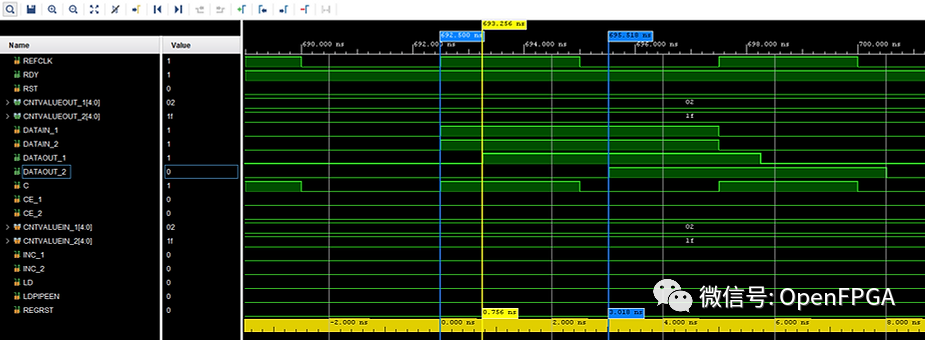

可以在下面看到整体仿真延迟比较小,无法看到该级别延迟的影响。然而,随着仿真执行不同的测试,我们将看到控制信号和抽头值发生变化。

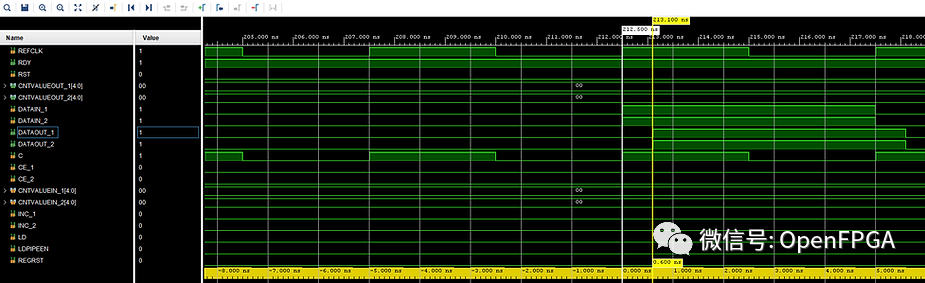

测试一的波形如下所示。尽管没有计算延迟,但输入信号和输出信号之间存在大约 60 ps 的延迟。

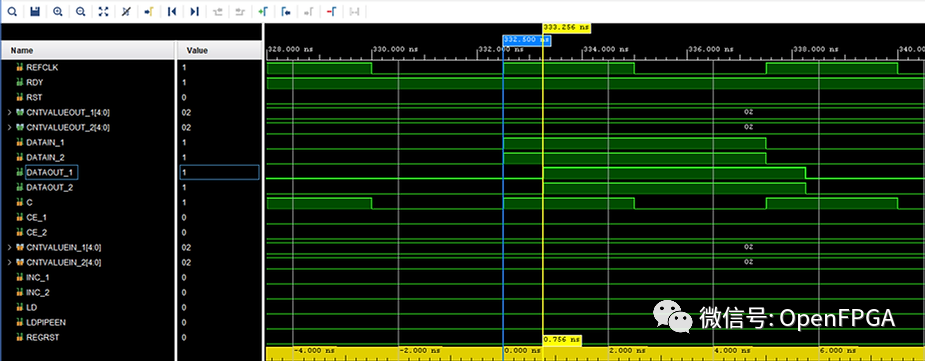

当延迟设置为 2 时,延迟为 756 ns,即 156 ps(两个 78 ps 的抽头延迟)加上原来的 0.6 ns 延迟。

第三个测试显示信号一和信号二之间有 78 ps 的延迟。对应于接头设置的差异,这也显示在计数值输出信号上。

第四个测试将两个信号路径设置为具有相同的延迟。测试三和四演示了简单的递增和递减接口是如何工作的。我们启用 IDELAY2,并根据 INC 的状态,增加或减少抽头延迟。如果 INC 设置为与 CE 一致,则增加抽头延迟,否则减少抽头延迟。

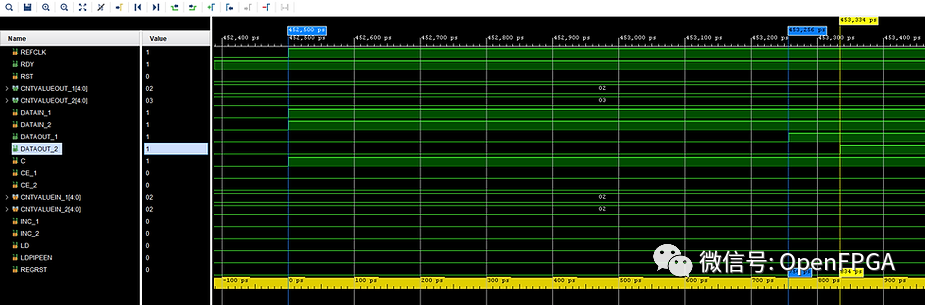

最后的测试将第二个信号路径设置为最大延迟。在这里可以看到信号 2 延迟了 3.018 ns。这是2.469 ns 的抽头延迟加上原来的 0.6 ns。

IDELAY 在我们的工具箱中是一个非常有用的工具,它提供了对 FPGA 中的输入信号进行细粒度对齐的能力。

-

FPGA

+关注

关注

1631文章

21808浏览量

606799 -

IO

+关注

关注

0文章

468浏览量

39461 -

应用程序

+关注

关注

38文章

3299浏览量

58002

原文标题:FPGA项目开发之 7 系列 FPGA 高级 SelectIO 逻辑资源

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

xilinx FPGA中oddr,idelay的用法详解

如何在应用程序中实现 IDELAY 功能

嵌入式应用程序中的USB 3.0链路共享怎么实现?

如何在PC上测试固件应用程序?

如何在应用程序“CyMeCube”中查看端点?

CH32F103如何在应用程序中响应中断?

如何在应用程序中实现IDELAY功能并创建一个不同模式下的实例

如何在linux应用程序中使用pwm捕获?

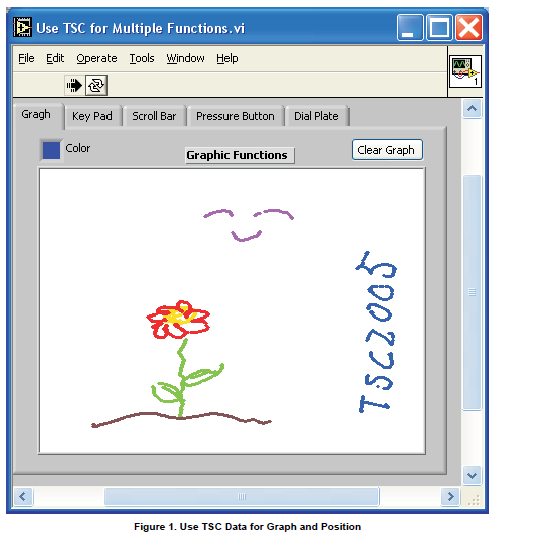

如何在软件中实现TI的触摸屏控制器提供的各种功能详细概述

如何在应用程序中实现 IDELAY 功能

如何在应用程序中实现 IDELAY 功能

评论