ASIC设计中详细设计方案的确定非常重要,同样的设计,别人可以用比你小30%的面积和少30%的处理时间来实现,这才是设计工程师的价值体现之处。任何设计在最开始的时候都是一头雾水,场景复杂,各种耦合。我们要做的是将所有的场景都整理出来,然后想办法进行归一。任何一开始觉得不可能做到的任务最后都能找到解决方法。这本来看似是没有规律的世界,但人类就是去不断寻找和发现这个物质世界的运行规律。当然,即使第一版设计我们尽可能的考虑到了更多的场景和实现方案,但是最后实现阶段还是会有一些考虑不周全和不合理的实现,由于时间成本原因,决定放到下一版再修改。这个过程就叫做优化!那么,如何优化一个设计?

找大寄存器组

首先是找设计中的大寄存器组,寄存器是面积较大的基本单元了,寄存器的数量决定了设计整体的面积数量级。小容量的存储用regfile,一般寄存器组用到了上千bit,就要考虑是否用RAM。上万bit的就是不合理的设计。

看到大寄存器组是要重点关注优化的对象,要注意的是,寄存器组是可以随意在任意bit取值的,RAM是需要一拍一拍的读取的,所以需要在高并行度和面积之前做折中(trade off)。数据通路寄存器打拍过多,肯定不合理,一个数据打一拍最起码是几十个bit,打多拍,就上百bit。而换一个设计思路,在控制上多少逻辑,控制信号+计数器,多做几组也就拢共几十个bit的样子。比如前一级模块传过来的数据和valid信号,数据是要晚几拍才使用,应该做成前一级模块先给valid信号,数据晚几拍再来,避免数据打拍。在数据通路上出现一些组合逻辑路径并不长,打了一拍,这样虽然时序会更好,但是最后增加的面积来说并不值得,所以多余的寄存器打拍完全可以“干”掉。

重定时

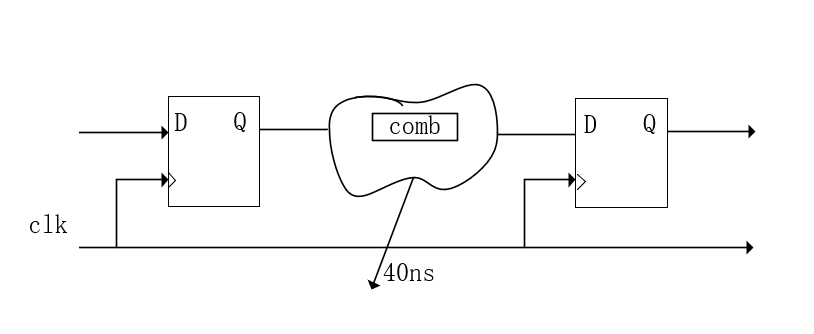

Retiming就是重新调整时序,例如电路中遇到复杂的组合逻辑,延迟过大,电路时序不满足,这个时候采用流水线技术,在组合逻辑中插入寄存器加流水线,进行操作,面积换速度思想。

任何的数字电路都可以等效成组合逻辑加D触发器打拍,两个D触发器之间的组合逻辑路径决定了,系统的工作频率,决定芯片的性能。所以为了提高芯片的工作频率,使用流水线技术在组合逻辑中插入寄存器。

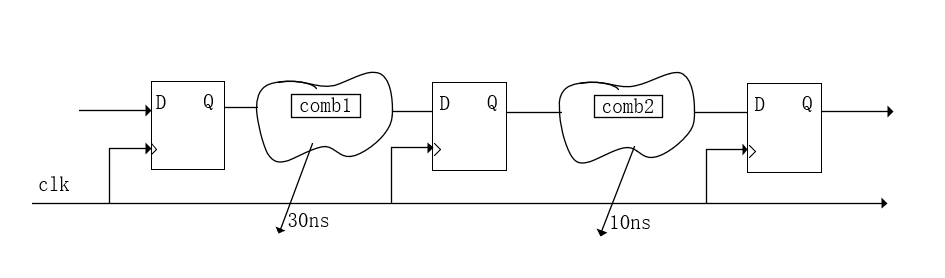

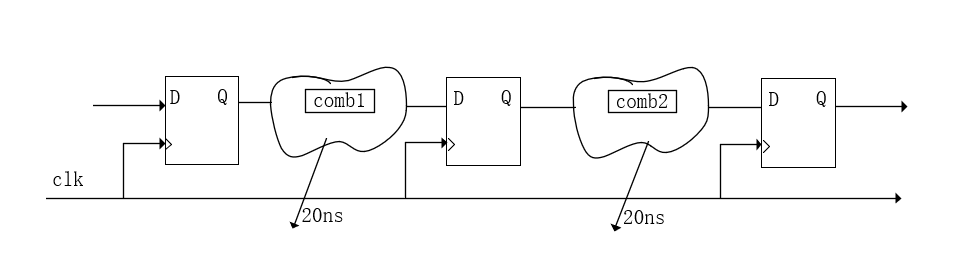

插入寄存器的位置需要慎重选择,不同的位置数据的打拍所消耗的寄存器的数量也不同,比方说你在位置a消耗25bit寄存器,位置b消耗20bit寄存器,能省则省。

前面插入寄存器的位置使得comb1的延迟为30ns,comb2的延迟为10ns,系统的最高工作频率是由最长路径决定的。也就是说你这个系统最高工作频率的周期,不小于30ns,前面是插入pipeline,这个时候我们不改变时序,采用重定时技术,使得各个组合逻辑之间的延迟相当。

疯狂复用

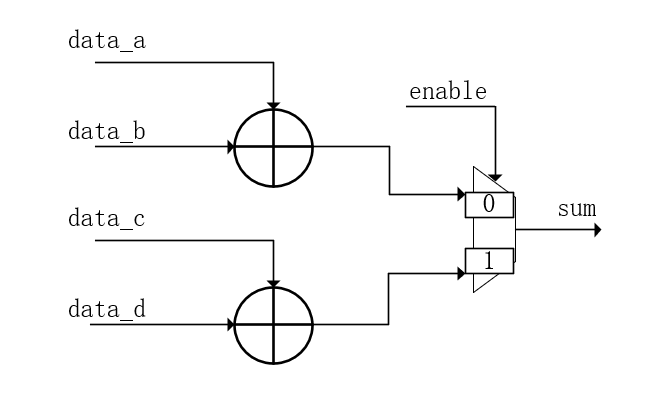

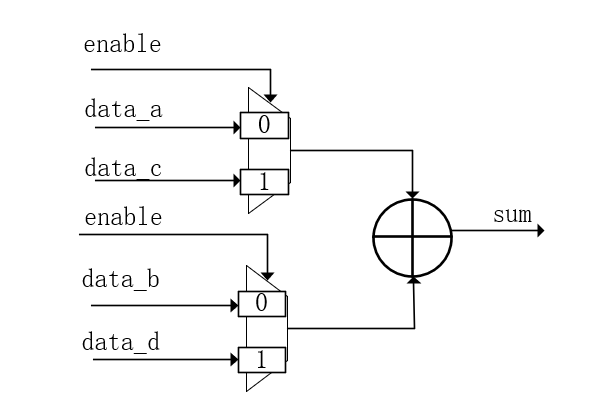

找计算逻辑相同的单元,复用最常见的就是计数器,能用一个计数器实现的,就别用俩,底层模块之间相同的逻辑尽量使用一块电路,减少重复的设计。基本逻辑单元的共享举例,面积:加法器 > 比较器 > 选择器。加比选。乘法器本质上也是全加器。所以就有先选后比,先选后加,先选后乘。画个图意思一下。

这里的加法器可以换成任何逻辑或模块。

乘法器分时复用度提高

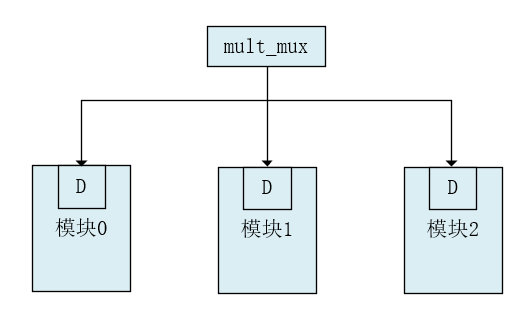

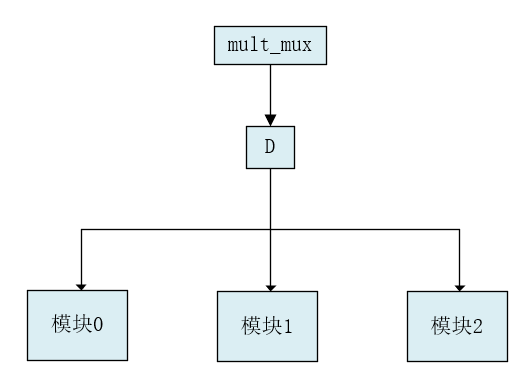

在计算模块中乘法器也是非常大的一部分逻辑,一个设计要考虑PPA最优,就要考虑乘法器的数量多少以及复用能不能最大化,追求最好的设计是整个数据通路中乘法器空闲不下来。乘法器调用方法,一般是在乘法器的输入保证寄存器输入,结果输出到各个复用模块时打一拍再使用。可以做成在进行完乘法运算后,就打拍,这样消耗的寄存器会少很多。画个图意思一下(单bit)。

修改前

修改后修改完后的寄存器省了很多,但是乘法器的输出寄存器负载会变大,不过后端综合时约束了max_fan_out工具会自动插buffer和复制寄存器,经过实测还是会节省很多面积,把一些优化工作可以交给工具去做,了解它,信任它,使用它。

RAM的复用

从设计的整体来看,RAM也可以复用,前面处理用过的ram,现在空下来,后面能否用。

最后

总结一下ASIC单个模块的设计/优化思路,列出所有条件,然后归一,复用,面积与速度呼唤的思想贯穿始终。

审核编辑:汤梓红

-

asic

+关注

关注

34文章

1204浏览量

120577 -

寄存器

+关注

关注

31文章

5357浏览量

120734

原文标题:如何优化一个设计?

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于ASIC单个模块的设计/优化思路

怎么利用Synphony HLS为ASIC和FPGA架构生成最优化RTL代码?

基于ASIC/SoC的UART核的设计

ASIC,ASIC是什么意思

串口WiFi模块实现远程控制电饭煲的设计思路分享.pdf

FPGA模块化设计与AlteraHardCopy结构化ASIC

VoLTE优化思路干货资料下载

日常网络优化思路资料下载

ASIC单个模块的设计和优化思路

ASIC单个模块的设计和优化思路

评论