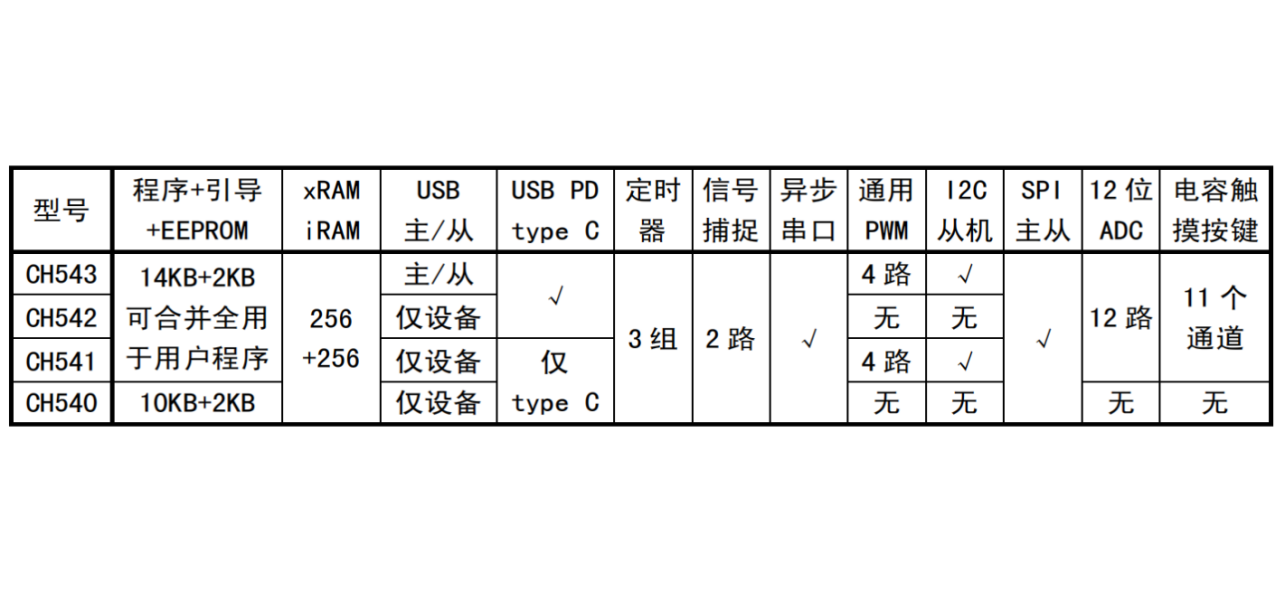

USB PD芯片CH543,支持BC/PD协议及主从设备,支持正反向充电

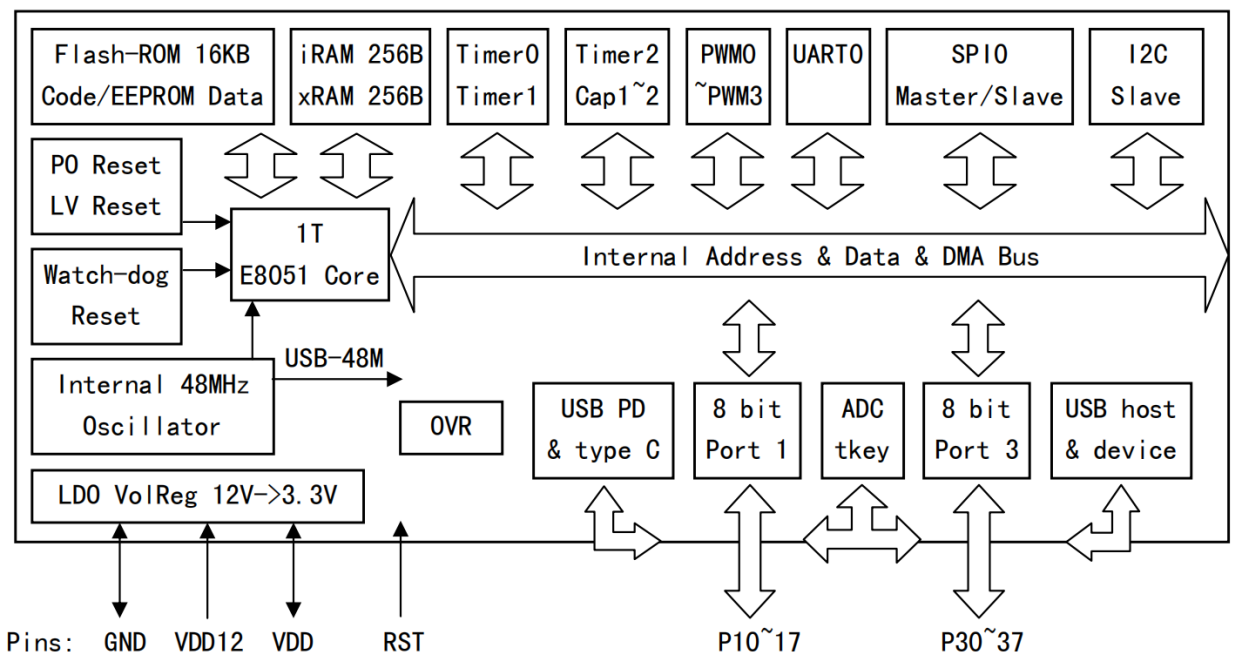

CH543芯片是一款兼容 MCS51指令集的USB和USB PD增强型E8051内核MCU,其79%的指令是单字节单周期指令,运行速度快。内置16K程序存储器 Flash-ROM和256字节内部iRAM以及 256字节片内xRAM, xRAM支持DMA直接内存存取。

CH543内置了USB Power Delivery控制器和PD BMC PHY收发器,支持 USB type C、BC、PD2.0、PD3.0,支持12V高压电源,作为PMIC用于电源管理、受电端、供电端、DRP。

CH543内置了USB主机控制器和收发器,支持全速和低速USB Host主机和USB Device设备。

CH543 还内置了12位ADC模数转换、电容式触摸按键检测模块、内置时钟、3组定时器和2路信号捕捉、4路PWM、异步串口、SPI、I2C 从机等功能模块。

增强型E8051内核CPU,特有 XRAM 数据快速复制指令,双 DPTR 指针。

内嵌USB控制器和USB收发器,支持USB2.0全速和低速主机或设备,支持DMA。USB端口支持BC充电协议。

提供USB Power Delivery控制器和PD收发器PHY,支持USB PD2.0和 PD3.0电力传输控制,支持 DRP。

P3.5引脚支持VDD12高压12V 输入输出,RST引脚作为通用输入支持 VDD12高压12V。

内置12V到3.3V或4.7V的低压差电压调整器,用于USB和I/O及 ADC 等模块,VDD12支持5V或3.3V或9V甚至12V或2.8V电源电压。

提供TSSOP20、SOP16、QFN20、ESSOP10封装。

特点

Core:增强型 E8051 内核,兼容 MCS51 指令集,其 79%的指令是单字节单周期指令,平均指令

速度比标准 MCS51 快 8~15 倍,特有 XRAM 数据快速复制指令,双 DPTR 指针。

ROM:16KB 非易失存储器 Flash-ROM,支持 10K 次擦写,可全部用于程序存储空间;或可分为

14KB 程序存储区和 256B 数据存储区 EEPROM 以及 1.75KB 引导代码 BootLoader/ISP 程序区。

EEPROM:数据存储区 EEPROM 共 256 字节,分为 4 个独立块,支持单字节读、单字节写、块写

(1~64 字节)、块擦除(64 字节)操作,在典型环境下一般支持 100K 次擦写。

OTP:一次性可编程数据存储区 OTP 共 32 字节,支持双字读(

4 字节)、单字节写。

RAM:256 字节内部 iRAM,可以用于快速数据暂存以及堆栈;256 字节片内 xRAM,可以用于数

据暂存以及 USB 或 USB PD 的 DMA 直接内存存取。

USB:提供 USB 控制器和 USB 收发器,支持 USB-Host 主机模式和 USB-Device 设备模式,支持

USB 2.0 全速 12Mbps 或者低速 1.5Mbps。支持最大 64 字节数据包,内置 FIFO,支持 DMA。USB

端口支持 BC 充电协议,支持 UART 异步串口 RXD/TXD 引脚映射。

USB PD 和 type C:提供 USB Power Delivery 控制器和 PD 收发器 PHY,支持 USB type-C 主从

检测,自动 BMC 编解码和 CRC,硬件边沿控制,支持 DMA,支持 USB PD2.0 和 PD3.0 电力传输

控制,支持 DRP。

Timer:3 组 16 位定时器,T0/T1/T2 为标准 MCS51 定时器。

Capture:定时器 T2 扩展为支持 2 路信号捕捉,支持前沿触发、后沿触发、周期检测。

PWM:4 路 8 位普通 PWM 输出或者 2 路高精度 12 位 PWM 输出,支持交错输出。

UART:标准 MCS51 异步串口,支持最高 3Mbps 或 460800bps 通讯波特率。

SPI:支持 Master/Slave 主从模式,内置 FIFO,时钟频率最高可接近系统主频 Fsys 的一半,

支持串行数据输入输出单工复用。

I2CS:I2C slave 从机控制器,支持 1MHz 时钟。

ADC:12 通道 12 位 A/D 模数转换器,可选输入缓冲或者简单放大。

Touch-Key:支持 11 通道电容触摸按键检测,除 RST 外的每个 ADC 通道都支持触摸按键检测。

GPIO:支持最多 17 个 GPIO 引脚(含 USB 和 USB PD 及 RST 引脚),支持 MCS51 兼容的准双向模

式,新增高阻输入、推挽输出、开漏输出模式。

P3.5 引脚支持 VDD12 高压 12V 输入输出,RST 引脚作为通用输入支持 VDD12 高压 12V。

Interrupt:支持 14 组中断信号源,包括与标准 MCS51 兼容的 6 组中断(INT0、T0、INT1、T1、

UART0、T2),以及扩展的 8 组中断(SPI0、I2C、USB、ADC、USB PD、PWMX/CMP、GPIO、WDOG),

其中 GPIO 中断可以从多个引脚中选择。

Watch-Dog:8 位可预设看门狗定时器 WDOG,支持定时中断。

Reset:支持 7 种复位信号源,内置上电复位 POR 和电源低压检测复位 LVR 及电源过压复位 OVR

模块,支持软件复位和看门狗溢出复位,可选引脚外部输入复位,可选 USB PD 硬件复位。

Clock:内置 48MHz 时钟源,用于产生所需频率的系统主频 Fsys 和 USB 时钟。

Power:内置 12V 到 3.3V 或 4.7V 的低压差电压调整器,用于 USB 和 I/O 及 ADC 等模块,VDD12

支持 5V 或 3.3V 或 9V 甚至 12V 或 2.8V 电源电压。

支持 VDD12 高压放电、RST 引脚 12V 高压放电。

Sleep:支持低功耗睡眠,支持 USB、USB PD/type C、UART0、SPI0 以及部分 GPIO 外部唤醒。

芯片内置唯一 ID 号,支持 ID 号和校验。

审核编辑:汤梓红

-

控制器

+关注

关注

114文章

17890浏览量

195342 -

usb

+关注

关注

60文章

8481浏览量

286099 -

PD

+关注

关注

4文章

561浏览量

46156

发布评论请先 登录

CH9245:双Type-C转PD芯片方案

集成低阻抗开关的 USB PD Source 控制芯片 HUSB352:小型化快充的理想之选

HUSB380:高性能USB PD Source控制芯片的卓越之选

探索HUSB338D:高性能USB Type - C PD Source控制芯片

高速USB转4串芯片CH9114系列

EZ - PD™ CCG7SC:单端口 USB Type - C 与 PD 和升降压控制器的深度剖析

EZ-PD™ PAG2-PD CYPAS2174 :USB 供电适配器的高效解决方案

TPS25730:USB Type - C和USB PD控制器的卓越之选

FS8024A USB PD协议SINK端诱骗取电芯片数据手册

什么是PD协议芯片,它的工作原理是什么 PD协议芯片XSP01A 的特点是什么

USB PD芯片CH543概述

USB PD芯片CH543概述

评论