传统的微控制器(MCU)架构(具有处理器、片上闪存和外设输入或输出器件)在40多年来基本保持不变。然而,新兴的应用程序和用例正在破坏这种长期建立的设计范式,因为系统要求不断发展,这些要求:

大量代码和/或

大量的处理和性能

例如,考虑小型连接设备(如物联网端点)或可穿戴设备(运行高级蜂窝或无线协议,如LTE-M,NB-IoT或Wi-Fi)的激增。这些通信堆栈包含大量代码,由于应用软件的庞大规模,通常不适合MCU的嵌入式闪存。

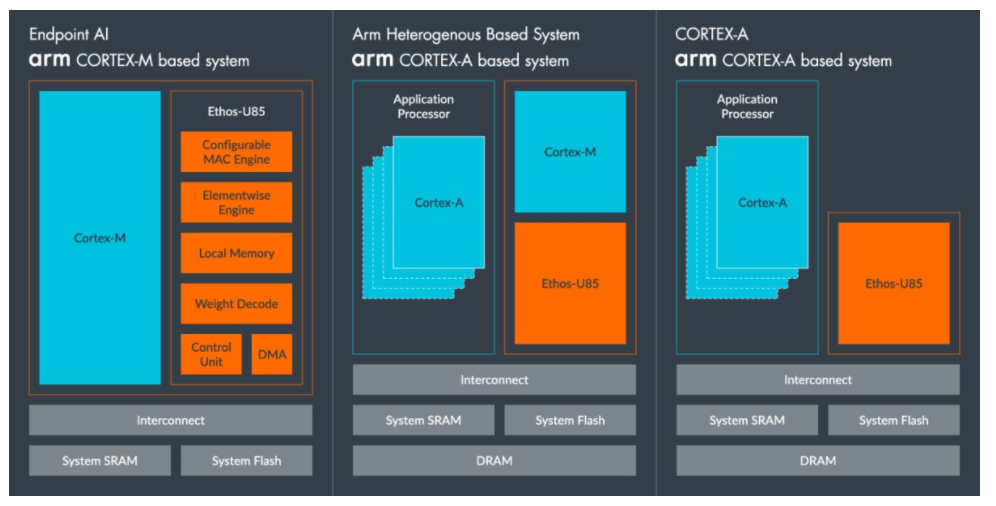

或者考虑人工智能(AI)和推理应用程序的快速增长,这些应用程序需要在网络边缘提供大量的数据处理性能,这反过来又会带来高水平的功耗。为了满足这些对更高性能和更高能效的双重竞争要求,设计人员可以在更现代的工艺技术(如22nm甚至更精细的几何形状)上构建设计。但是,这些较新的工艺节点不提供片上闪存。

这些用例给边缘设备设计人员带来了挑战:如何设计一种架构,提供执行大量代码所需的性能和内存空间,同时遵守极低功耗和更小芯片占位面积的限制。

内存扩展架构

答案是将部分或全部MCU闪存放在片外,以就地执行或XiP模式运行。XiP是一种直接从外部闪存执行代码的方法,而不是首先将其从闪存复制到RAM,然后从该RAM执行程序。由于XiP架构中的闪存位于芯片外部,因此设计人员不受芯片上容纳的存储器量的限制 - 外部存储器可以根据需要尽可能大,以有效处理非常大的代码集。

这种新型MCU架构的一个主要例子是恩智浦的RT系列“交叉处理器”,例如 i.MX RT1050。设计灵活性是这些器件的主要优势之一,因为它们不包括内部闪存,而是使用外部存储器,这使得这些MCU能够根据应用的要求容纳任何大小的代码和数据存储器空间。此外,通过从芯片中移除嵌入式闪存,恩智浦能够在芯片上放置其他功能,以帮助优化以提高性能或能效。

将闪存放在片外还可以在更先进的工艺节点(低于40nm)中制造处理器,以支持更高的处理速度、更高的能效和更低的成本。嵌入闪存具有挑战性,特别是对于现代工艺技术,嵌入闪存所需的额外制造步骤显着增加了硅的成本。采用片上闪存设计的MCU必须吸收该过程的成本- 比没有闪存的相同版本的该过程贵约30%至40% - 以及闪存本身的面积成本。

然而,要打造成功的XiP架构,设计人员不能只使用任何闪存。串行闪存通常用于应用程序存储,例如PC中的BIOS。为此,闪存模块的性能或电源效率并不是特别重要,因为它仅在启动时用于将闪存的内容复制到RAM。然而,当在XiP架构中使用闪存时,软件是按需从外部存储器中获取的,这意味着高性能和高能效变得至关重要。

Adesto设计了一种闪存设备,该设备经过专门优化,可作为XiP微架构的外部存储器运行。Adesto EcoXiP Octal xSPI非易失性存储器(NVM)利用串行闪存技术的进步来满足高性能要求,使闪存设备能够以随机访问来自恩智浦RT1050等设备的读取请求进行响应,并以低延迟和高吞吐量提供指令和数据。

闪存挑战1:性能瓶颈

构建外部闪存系统以在 XiP 架构中作为随机存取存储器运行会带来许多挑战。首先,处理器和外部闪存是独立的设备,通过串行总线接口连接。在传统的串行接口中,数据以串行方式传输,一次通过一条线路传输。这引入了性能瓶颈和数据流延迟,特别是在具有高性能要求的系统中。

Adesto 设计了 EcoXiP 来快速响应来自主机 MCU 的读取请求,并以低延迟和高吞吐量提供指令和数据。事实上,EcoXiP 器件符合 JEDEC 最新的八通道 SPI 协议 (xSPI),使通信速度比单线串行闪存快得多。EcoXiP 提供多线智能串行外设接口,可加快 CPU 和外部闪存之间的数据流,允许数据一次通过八条并行数据线传输。

此外,生态优化还具有双倍数据速率 (DDR) 功能,这是高速数字内存中常见的功能。DDR的工作原理是在串行时钟的上升沿和下降沿发送数据位。现代串行闪存器件的时钟速度大于100MHz,并且由于发送数据位只需要半个时钟周期,因此DDR有可能使外部存储器的吞吐量翻倍。将八进制接口与 DDR 功能相结合,可将 xSPI 协议的吞吐量提高到单线串行闪存 16 倍。

EcoXiP 还通过减少命令接口的开销来解决延迟问题。“带包装的突发读取”命令的“连续”模式通过减少后续读取数据所需的时钟周期数,允许更快地访问数据。使用此命令消除了发送命令和地址的需要,然后在连续的缓存未命中中等待阵列访问时间(虚拟周期)。这可以节省大约20个周期,从而减少CPU看到的平均延迟。

闪存挑战2:电源效率

构建具有离散CPU和外部闪存的XiP系统的另一个挑战是,除了相互通信所需的能量外,为这两个独立的设备供电可能会增加系统的总能耗。EcoXiP 的设计通过在 XiP 模式下提供具有竞争力的功耗来降低这种风险。对于 133MHz 八通道 SPI 读取,EcoXiP 读取电流通常为 35mA,约为类似八通道 SPI 器件速率的一半。此外,EcoXiP 还提供可配置强度的 I/O 驱动程序。优化驱动程序的强度可最大限度地降低 CPU 与 EcoXiP 之间通信所需的功耗。

此外,EcoXiP 在 CPU 不需要闪存时提供深度省电模式和超深度省电模式。在超深省电模式下,该器件通常消耗 200 nano 安培,从而实现极低的功耗,对唤醒时间的影响很小。

与基于RAM的系统相比,超深度省电模式提供了XiP的另一个优势。该模式下闪存的功耗明显低于片上SRAM或外部DRAM的功耗。一些基于RAM的系统设计人员会选择在深度睡眠时关闭存储器的电源,但这需要从外部闪存重新加载RAM,这是一项耗时且耗电的操作。

闪存挑战3:无线更新

XiP系统设计人员面临的另一个挑战是提供一种对外部闪存上的程序信息执行无线(OTA)更新的方法。使用 OTA 更新写入闪存可能会长时间阻止闪存响应读取,从而阻止系统执行更新所需的下一条指令,从而导致处理死锁。

EcoXiP 的并发读写(也称为边写读或 RWW)允许主机处理器继续从闪存阵列的分区读取数据,同时修改另一部分的数据。例如,涉及对串行闪存进行擦除和编程操作的定期数据记录不会使XiP程序处于暂停状态。借助 RWW 功能,编程期间的指令和数据获取将照常在闪存的不同分区中继续进行。

Adesto与为微电子行业开发开放标准和出版物的全球领导者JEDEC密切合作,为MCU如何与XiP架构中的串行闪存设备进行通信建立标准。阿德斯托是第一家实施所有串行闪存 JEDEC 标准的闪存制造商,包括 JESD216D、JESD251 和 JESD252,因此遵守这些标准的设计人员可以可靠地实施 EcoXiP,以构建针对 XiP 架构优化的高级器件。

结论

虽然片外闪存不是芯片设计人员面临的每个挑战的答案,甚至不是每个系统或应用的答案,但XiP架构能够支持可扩展的外部软件和数据存储空间,以适应新兴用例,特别是对于边缘物联网和人工智能应用。将外部串行闪存与嵌入式处理器结合使用,可提供高度可扩展的平台,以应对当今不断发展的嵌入式系统面临的许多挑战。

审核编辑:郭婷

-

物联网

+关注

关注

2910文章

44778浏览量

374672 -

AI

+关注

关注

87文章

31155浏览量

269481 -

NB-IoT

+关注

关注

412文章

1448浏览量

184639

发布评论请先 登录

相关推荐

有方科技助力物联网边缘计算产业发展

物联网学习路线来啦!

物联网边缘计算的概念

华邦电子为边缘设备打造生成式AI性能

RISC-V适合什么样的应用场景

基于RK3588核心板的AI边缘计算网关设计方案

边缘计算智能网关为物联网设备高效通信赋能

risc-v多核芯片在AI方面的应用

NanoEdge AI的技术原理、应用场景及优势

Supermicro全新系统产品组合将前沿AI性能推向边缘计算环境

Supermicro通过业界领先的全新系统产品组合,将前沿AI性能推向边缘计算环境

XiP架构适合边缘物联网和AI的代码和性能要求

XiP架构适合边缘物联网和AI的代码和性能要求

评论