FPGA浮点转定点运算、除法转乘法运算以及运算误差分析

FPGA在常规运算时不能进行浮点运算,只能进行定点整型运算,在处理数据的小数乘加运算和除法运算时FPGA一般是无能为力的,其中一种常用的处理方法就是数据进行浮点到定点的转换。

浮点数转化为定点数一般有两种方法:

浮点数直接乘以一个数值。浮点小数(X)到定点数据(Xq)的转换其实很简单,就是把浮点小数乘以一个很大的2的n次幂的数据Xq=X*2^n,来把小数转化为整数,然后再进行数据的乘加运算,运算结果通过移位来得到实际对应的理论数据结果。

直接把浮点数转化为有符号的二进制小数用SxQn来表示,然后进行乘加运算,运算结果通过移位来得到实际对应的理论数据结果。

通过上述两种方法运算能完成浮点到定点乘加运算的结果,但是上述两种方法存在一定的问题:

存在浮点小数(X)进行整数转化定点数据(Xq)后依然还是一个小数的情况。

浮点数转化为二进制数存在数据位宽激增情况,使得SxQn的数据位宽变大。

数据运算存在一定的截位误差,这部分误差只能减小而不能消除。

浮点到定点数据转化后数据位宽变大,占用逻辑资源增加。

在实际使用时由于直接把浮点数转化为有符号的二进制小数用SxQn来表示这种方法局限性较多,近而大都采用浮点数直接乘以一个数值这种方式,但是这种方式使用时需要注意截位误差和量化误差。

第一种浮点数直接乘以一个数值方法具体过程如下:

浮点数(x)转换为定点数(xq):xq=(int)x2^Q 定点数(xq)转换浮点数(x):x= (float)xq2^(-Q) 比如,16进制数2000H,用Q0表示就是8192;若用Q15表示,则为0.25。 下面介绍Q格式运算中Q值的确定:

(1)定点加减法:需要转换成相同Q格式才能加减 (2)定点乘法:不同Q格式的数据相乘,相当于Q值相加 (3)定点除法:不同Q格式的数据相除,相当于Q值相减 (4)定点左移:相当于Q值增加 (5)定点右移:相当于Q值减少 比如,Q15表示的4000H(浮点数0.5)乘以Q15表示的4000H,4000H×4000H=1000 0000H,乘完之后Q值变为15+15=30,即结果为0.01B,即为浮点数0.25。 对应浮点数的除法运算时是把除法转换成乘法运算来实现。即分子/分母(A/B)转化为A*(1/B),这时会面临B是固定值和变值两种情况 1、如果B是固定值利用这种方式即可把(1/B)转化为定点数,然后进行乘法运算,这样计算速率较块,且通过合理的选择放大倍数来减小数据的误差。 2、如果对应B不是固定值,那么就将B变为对应位宽的整数,然后再进行数据的乘法运算。 数据的误差来源于浮点转化为定点时截位和运算结果截位引起的,这里可以通过常用的截位方式来实现截位。 常见的截位方式有:

1、负数直接截位后+1,就是所有数都按绝对值取floor 2、Truncate:直接截位,就是正数取floor,负数按绝对值取ceil 3、Rounding:舍入截位,就是所有数按绝对值取四舍五入

-

FPGA

+关注

关注

1629文章

21729浏览量

602978 -

数据

+关注

关注

8文章

7002浏览量

88940

原文标题:FPGA浮点转定点运算、除法转乘法运算以及运算误差分析

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【安富莱——DSP教程】第7章 DSP定点数和浮点数(重要)

第7章 DSP定点数和浮点数

verilog程序定点数的资料

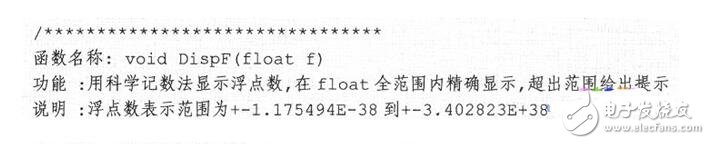

功能函数中的浮点数转换为定点数

定点数和浮点数的区别是什么

请问ADSP-21469的汇编指令集ISA/VISA中有没有专门用来进行浮点数和定点数转换的指令?

功能:双字节十六进制定点数转换成格式化浮点数

在FPGA里浮点数与定点数表示法原理展示

单片机浮点数运算的源码设计

定点数和浮点数在STM32单片机中使用傅里叶(FFT)变换的理解

定点数和浮点数的概念 浮点数二进制序列与指数表达式之间的转化

FPGA浮点数转化为定点数方法

FPGA浮点数转化为定点数方法

评论