0 引言

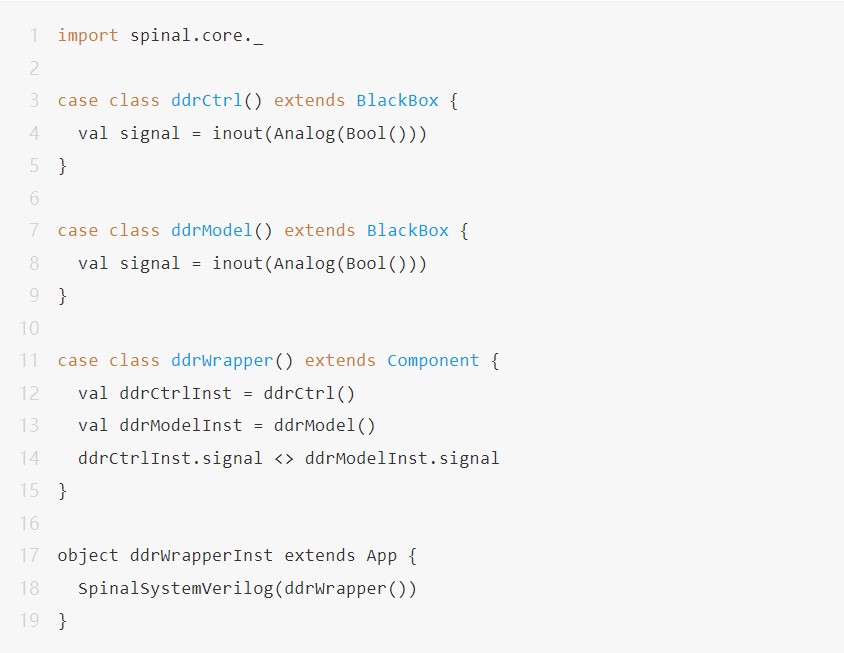

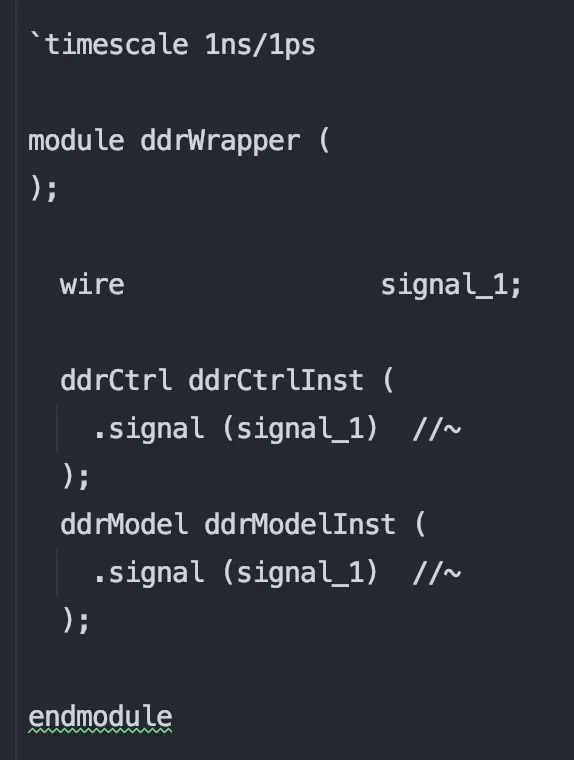

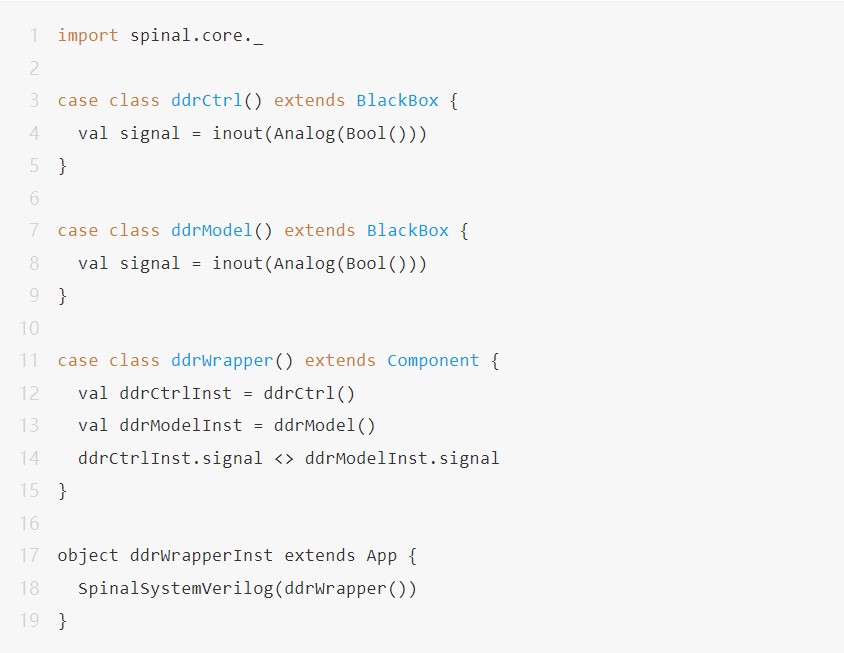

在SpinalHDL 1.7.0版本里,在仿真方面开始支持了VCS,这解决了在FPGA设计里采用Verilator时无法仿真厂商IP的问题。故此,前段时间尝试了把集成FPGA厂商DDR IP的测试。不曾想却遇到了一个从未遇到的错误。在DDR仿真里一般由控制器IP以及厂商的Memory Model组成,我将其各自封装成了一个Blackbox,而在集成的时候确过不去了。为简单起见,这里采用下面的代码示例:

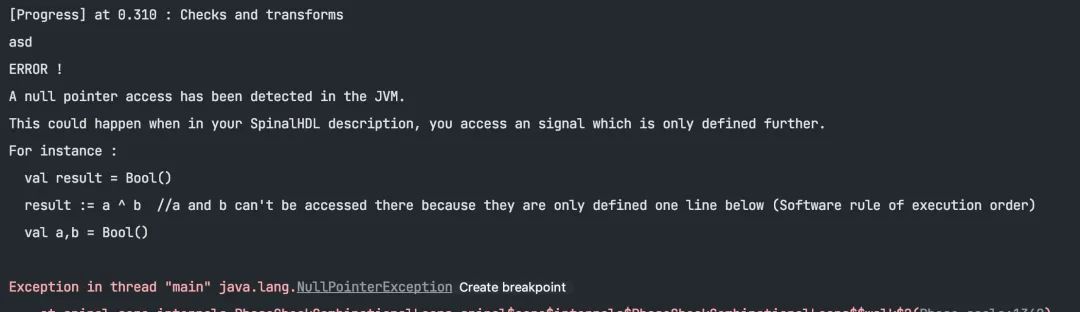

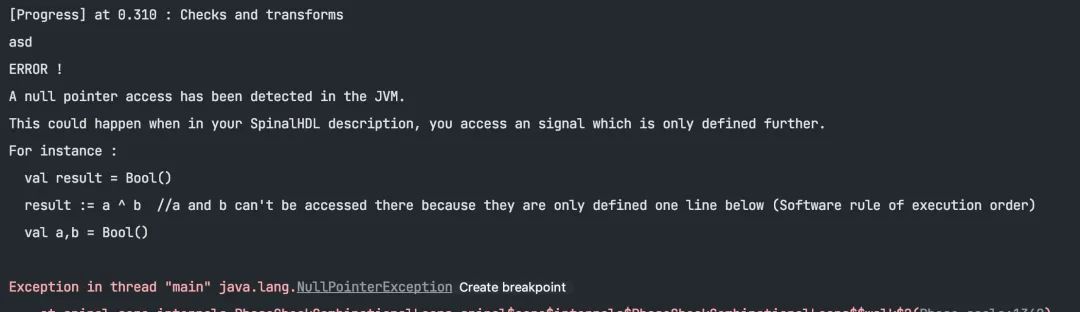

看起来似乎没啥毛病对吧,而且在之前写Verilog时候inout端口也是这么连接的。然而在运行的时候却报了下面的错误:

这错误类型我熟,但貌似明显我并没有犯这个错误啊…… 》解决之道

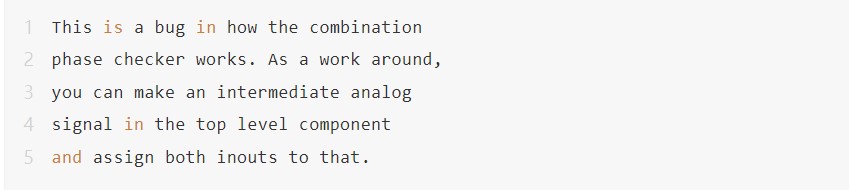

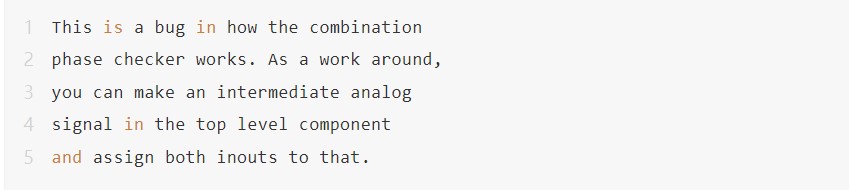

首先需要说明的是,这种使用场景也仅在仿真的时候会使用到,而真实的设计场景是不会有这么用的。但上面这个场景确实存在。在git上大神给出了下面的答复:

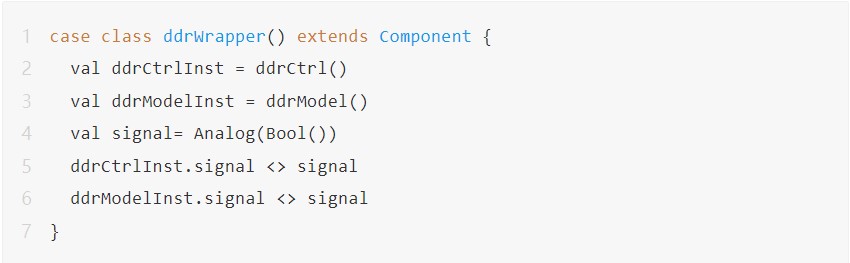

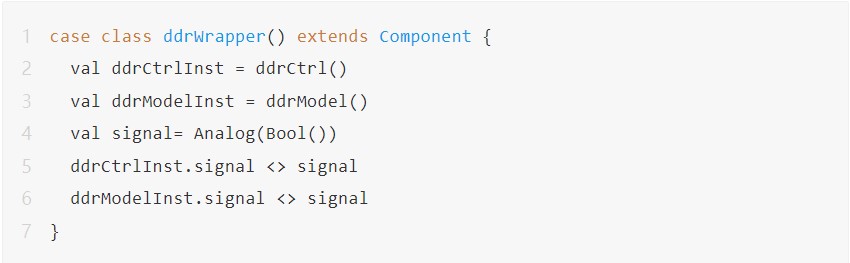

针对这种场景,这里给出一个解决方案,ddrWrapper重写如下:

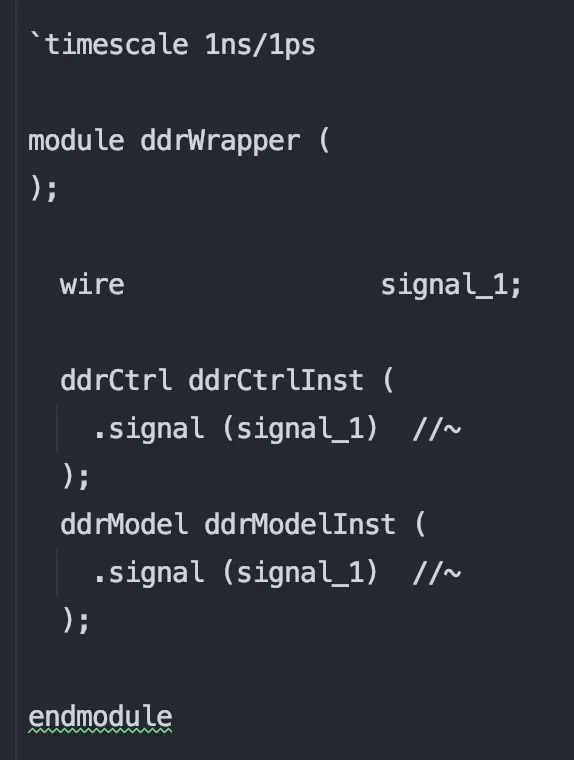

修改后即可达成我们想要的效果:

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:踩坑系列——inout连接不上

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

相关推荐

芯片外部引脚很多都使用inout类型的,为的是节省管腿。一般信号线用做总线等双向数据传输的时候就要用到INOUT类型了。就是一个端口同时做输入和输出。 inout在具体实现上一般用三态

发表于 01-17 10:08

。 inout在具体实现上一般用三态门来实现。三态门的第三个状态就是高阻'Z'。 当inout端口不输出时,将三态门置高阻。这样信号就不会因为两端同时输出而出错了,更详细的内容可以搜索一下三态门tri-state

发表于 08-09 08:21

workbench和FOC套件连接不上是什么原因呢?明明PC和板子连着了,但是却一直有个连不上的警告???跟不连板子没啥区别

发表于 11-30 09:48

是否可以将一个inout端口直接连接到另一个inout端口?在我的应用中,这个特定的信号只能连接两个外部设备,但是通过FPGA。它是两个外部设备的双向引脚。我已经看到其他地方建议使用类

发表于 04-15 15:08

请教一个问题,两个2540设备,一主一从,主查找到这个从设备,会启动与从设备的连接动作,但是这个时候,从掉电了,我监控到的结果是主一直停留在connecting的状态,就是启动建立连接的时候,为什么连接

发表于 11-06 09:32

; data_inout_buffer); 当我试图映射信号时,它显示错误:错误:Xst:528 - 信号单位中的多源>;此信号连接到多个驱动程序。(2)我无法监控chipcope pro分析仪中

发表于 04-07 08:04

VS-RK3399安卓主板adb 链接不上问题如何解决?近来有不少人都在问,为啥RK3399的android系统,怎么都连接不

发表于 07-20 15:09

Inout端口信号做输入时,观察例子中的输出Data_out_t就应该是高阻态的,Inout在具体实现上一般用三态门来实现。三态门的第三个状态就是高阻''Z''。当Inout端口不输出

发表于 11-11 10:24

•3895次阅读

。 芯片外部引脚很多都使用inout类型的,为的是节省管腿。就是一个端口同时做输入和输出。 inout在具体实现上一般用三态门来实现。三态门的第三个状态就是高阻'Z'。当inou

![的头像]() 发表于

发表于 08-13 13:45

•1.7w次阅读

新一代互联网络在高性能、高可扩展性、高可用性和易部署性等方面提出了更高的要求,使得路由器结构越来越复杂,我们需要掌握的相关知识也越来越多,那么你知道路由器pppoe连接不上怎么办吗?下面是小编整理的一些关于路由器pppoe

发表于 04-27 10:34

•4.5w次阅读

现在越来越多的小伙伴对于教大家为什么wifi有信号却连接不上的方法这方面的问题开始感兴趣,因为大家现在都是想要熟知,那么既然现在大家都想要知道教大家为什么wifi有信号却连接

发表于 06-04 09:15

•1.3w次阅读

Xshell为什么连接不上服务器?Xshell可在Windows桌面下访问不同系统下的远程终端服务器,并且进行操作控制。新手用户有时在用Xshell远程连接Linux服务器时,可能

![的头像]() 发表于

发表于 06-09 13:47

•4513次阅读

芯片外部引脚很多都使用inout类型的,为的是节省管腿。一般信号线用做总线等双向数据传输的时候就要用到INOUT类型了。就是一个端口同时做输入和输出。

![的头像]() 发表于

发表于 06-25 09:10

•6395次阅读

Verilog语言是一种硬件描述语言(HDL),用于描述数字逻辑电路和系统。它是一种非常强大且广泛使用的语言,在数字电路设计中扮演着重要的角色。其中, inout 是Verilog中的一种信号类型

![的头像]() 发表于

发表于 02-23 10:15

•3130次阅读

InOut类型的仿真是指通过计算机软件模拟和模拟硬件组件之间的输入和输出交互过程,以验证和评估电子电路设计的正确性和性能。下面将详细介绍InOut类型的仿真及其实现方法。 一、InOut类型的概述

![的头像]() 发表于

发表于 02-23 10:17

•987次阅读

inout连接不上如何解决呢

inout连接不上如何解决呢

评论