现象

就是一个endpoint既有setup违反,又有hold违反;如果去修hold可能setup恶化;如果去修setup可能hold恶化。

成因

1、不同PVT条件下的cell delay variation较大;

2、某些cell的library setup time或library hold time特别大;

3、setup与hold的uncertainty或者derate约束较为严格或悲观;

4、launch clock和capture clock的skew较大,OCV导致setup和hold都较难收敛;

5、Timing path具有较大的cross-talk,因为串扰对setup和hold都是恶化的。

path种类

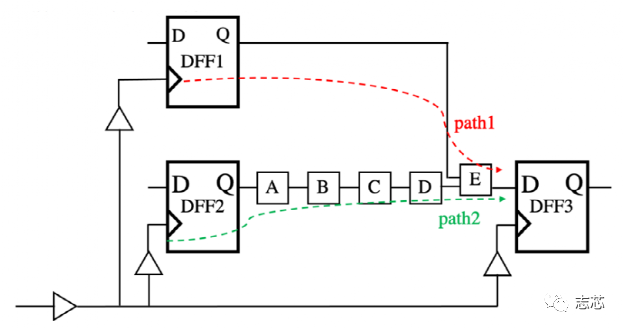

1、endpoint相同,startpoint不同:

Path1容易出现hold问题,path2容易出现setup问题;如果在path1和path2的commen part修timing就会导致另外一个path的恶化;所以应该分别在path1的非commen part修hold,在path2的非commen part修setup。

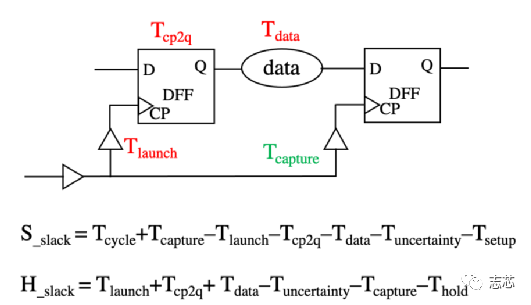

2、endpoint相同,startpoint相同,Launch clock和capture clock的skew较大:

Launch clock和capture clock的非commen part会吃掉大量OCV,使得setup和hold都恶化;所以需要思考一是是否可以做短非commen part,二是非commen part选用一些在不同PVT下cell delay variation较小的CK cell。

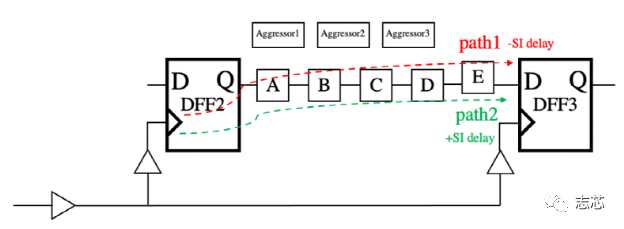

3、endpoint相同,startpoint相同,timing path上串扰较大:

串扰对setup和hold都是恶化的,可以使用“NDR rule” “shielding” “size drive-cell” “insert buffer”等方法fix cross-talk。

4、endpoint相同,startpoint相同,也没有cross-talk等问题,但是有互卡:

首先看约束(包括uncertain、derate)是否合理,如果不合理需要校正。看看不同PVT library中setup/hold time是否差异很大,是否可以考虑换一下不同的lib cell。看看path上不同PVT条件下的cell delay variation是否巨大。如果是可以考虑:1换VT,一般LVT的cell在不同PVT下delay差异较小;2、换corner,是否可以考虑换收敛的corner;3换lib cell,换cell delay variation的cell。

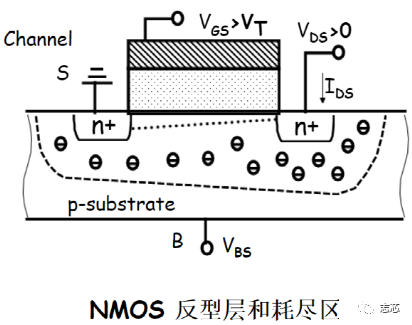

不同VTcell的delay差异

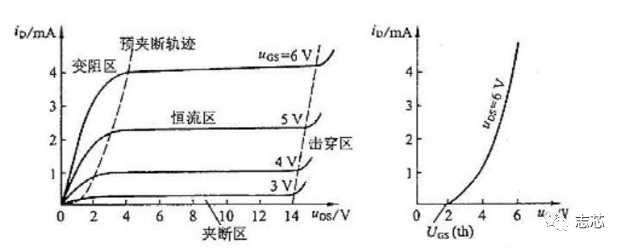

VT指的是MOS管的阈值电压(threshold voltage)。当栅源电压(Vgs)由0逐渐增大,直到MOS管沟道形成反型层(图中的三角形)所需要的电压为阈值电压。

影响VT有如下因素。金半接触电势差:和栅极金属方块电阻以及衬底掺杂浓度有关;氧化层中的电荷密度;半导体费米势;栅氧化层厚度;衬底掺杂浓度。源衬电压。

在一般工艺中,一般是通过控制衬底掺杂浓度来实现不同VT的。

如果MOS管阈值电压小,那么其饱和电流小,一般MOS管开启瞬间在饱和区,饱和电流小意味着需要的逃逸掉的载流子更少;对于低VT的cell,显然是更容易导通,而且其导通速度受PVT影响更小。

真的可以考虑换收敛corner

如下案例来自网友,原文链接如下,作者是“mnluan”。https://bbs.eetop.cn/thread-616584-1-1.html

说保hold,这样的回答是对的,传统思路就是保hold然后setup降频。但是我想说,如果不允许降频,你又会怎么办呢?

分享一下我们当时做出的不一样决定。在我们的案例中,有个800M的clock gate路径,同时出现了hold和setup的violation。如果保hold,setup势必要降频,而我们的降频无法做到从800M降频到750M,要降频就是直接降到了400M。而一旦降到400M,不要说性能了,功能都错了。

因为对于送入芯片的数据根本处理不过来。这样一来,即使保住了hold,也是个废品。所以当时我们分析了整个产品,不单纯是我们自己设计的芯片,查看板上其他芯片的文档。发现有个芯片工作温度最低是0度,而不是我们的-40度,于是首先调整了我们自己分析hold的corner,换成0度的库分析,hold violation减少了一些,但还是violation。接着又从客户那边了解到,实际使用时,会给产品进行一段时间的预热,所以我们大胆的把分析hold的corner调整到了TT下,hold check是过去的。

然后我们对工艺厂这些年生产我们芯片时的良率进行了分析,得出结论是,他家的Process大概率不在FF上,可以用TT分析。最后,我们保证了SS corner下的setup,用TT corner下的hold check代替了传统FF corner下的hold check。

-

MOS管

+关注

关注

108文章

2385浏览量

66497 -

电压

+关注

关注

45文章

5547浏览量

115530 -

Delay

+关注

关注

0文章

10浏览量

10870

原文标题:setup和hold互卡情况和解决办法

文章出处:【微信号:数字ICer,微信公众号:数字ICer】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Matlab的cell数组的问题

5 Cell to 10 Cell Li Protecto

BM209 Series Two-cell Li Batte

VIA/ 威盛 VT6410 /VT6420/ VT6421

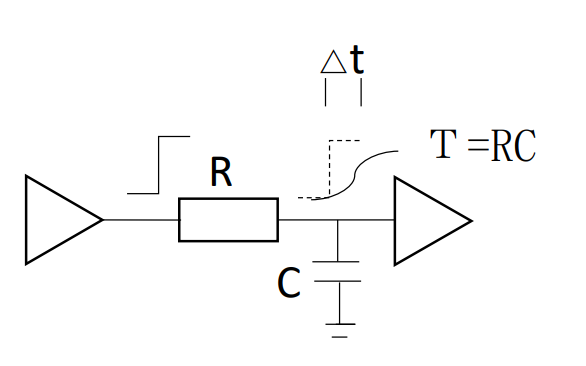

How Delay Lines Work

in-cell panel_In-Cell触摸屏原理

全贴合In-Cell/On-Cell/OGS三种屏幕技术之间存在哪些差别

芯片延迟Delay测试的学习课件PDF文件免费下载

stm32 delay文件总结

不同VT cell的delay差异

不同VT cell的delay差异

评论