在FPGA设计开发中,很多场合会遇到同一根信号既可以是输入信号,又可以是输出信号,即IO类型(Verilog定义成inout)。

对于inout型的信号,我们既可以使用FPGA原语来实现,也可以使用Verilog代码来实现。下面将介绍在Xilinx 7系列FPGA上两种实现方式的差别和注意点。

1.FPGA原语实现

首先,我们编写的代码如下:

`define PRIMITIVE module io_buf( input T , input I , output O , inout IO ); `ifdef PRIMITIVE IOBUF #( .DRIVE (12 ), // Specify the output drive strength .IBUF_LOW_PWR ("TRUE" ), // Low Power - "TRUE", High Performance = "FALSE" .IOSTANDARD ("DEFAULT" ), // Specify the I/O standard .SLEW ("SLOW" ) // Specify the output slew rate ) IOBUF_INST ( .O (O ), // Buffer output .IO (IO ), // Buffer inout port (connect directly to top-level port) .I (I ), // Buffer input .T (T ) // 3-state enable input, high=input, low=output ); `else assign IO = T? I:1'bz; assign O = IO; `endif endmodule

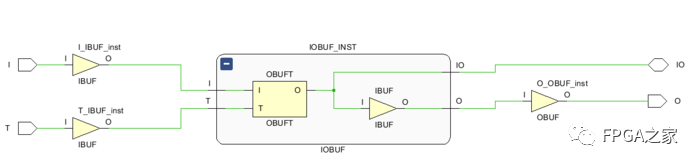

该代码通过原语IOBUF实现IO功能,使用Vivado编译后的原理图如下图所示。可以看到IOBUF内部由OBUFT和IBUF原语构成。

2.使用Verilog实现

把`define PRIMITIVE注释掉,则为通过Verilog的实现方式,如下图:

//`define PRIMITIVE

module io_iobuf(

input T ,

input I ,

output O ,

inout IO

);

`ifdef PRIMITIVE

IOBUF #(

.DRIVE (12 ), // Specify the output drive strength

.IBUF_LOW_PWR ("TRUE" ), // Low Power - "TRUE", High Performance = "FALSE"

.IOSTANDARD ("DEFAULT" ), // Specify the I/O standard

.SLEW ("SLOW" ) // Specify the output slew rate

) IOBUF_INST (

.O (O ), // Buffer output

.IO (IO ), // Buffer inout port (connect directly to top-level port)

.I (I ), // Buffer input

.T (T ) // 3-state enable input, high=input, low=output

);

`else

assign IO = T? I:1'bz;

assign O = IO;

`endif

endmodule

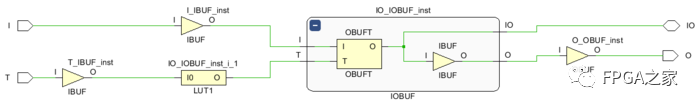

该代码使用Vivado编译后的原理图如下图所示。该实现方式也会调用IOBUF原语,但多消耗了一个LUT资源。

通过Verilog实现时,我们在把IO信号当成输入时给赋值高阻态(1‘bz)。假如我们把此时的IO信号赋值1‘b0或者1‘b1,会出现什么情况呢?我们把1‘bz写成1‘b1,如下所示:

//`define PRIMITIVE

module io_iobuf(

input T ,

input I ,

output O ,

inout IO

);

`ifdef PRIMITIVE

IOBUF #(

.DRIVE (12 ), // Specify the output drive strength

.IBUF_LOW_PWR ("TRUE" ), // Low Power - "TRUE", High Performance = "FALSE"

.IOSTANDARD ("DEFAULT" ), // Specify the I/O standard

.SLEW ("SLOW" ) // Specify the output slew rate

) IOBUF_INST (

.O (O ), // Buffer output

.IO (IO ), // Buffer inout port (connect directly to top-level port)

.I (I ), // Buffer input

.T (T ) // 3-state enable input, high=input, low=output

);

`else

assign IO = T? I:1'b1;

assign O = IO;

`endif

endmodule

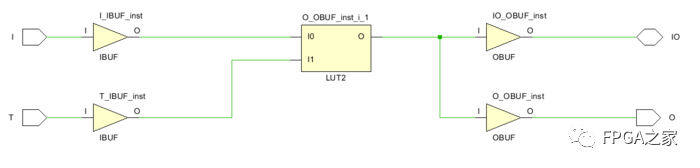

编译后的原理图如下,可以看到并不会调用IOBUF原语,IO的不能实现输入功能,这就是解释了为什么在使用Verilog实现一根信号的IO功能时需要赋值1‘bz。

-

FPGA

+关注

关注

1629文章

21732浏览量

603084 -

Xilinx

+关注

关注

71文章

2167浏览量

121338 -

代码

+关注

关注

30文章

4781浏览量

68542

原文标题:FPGA之IO信号类型深入理解

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

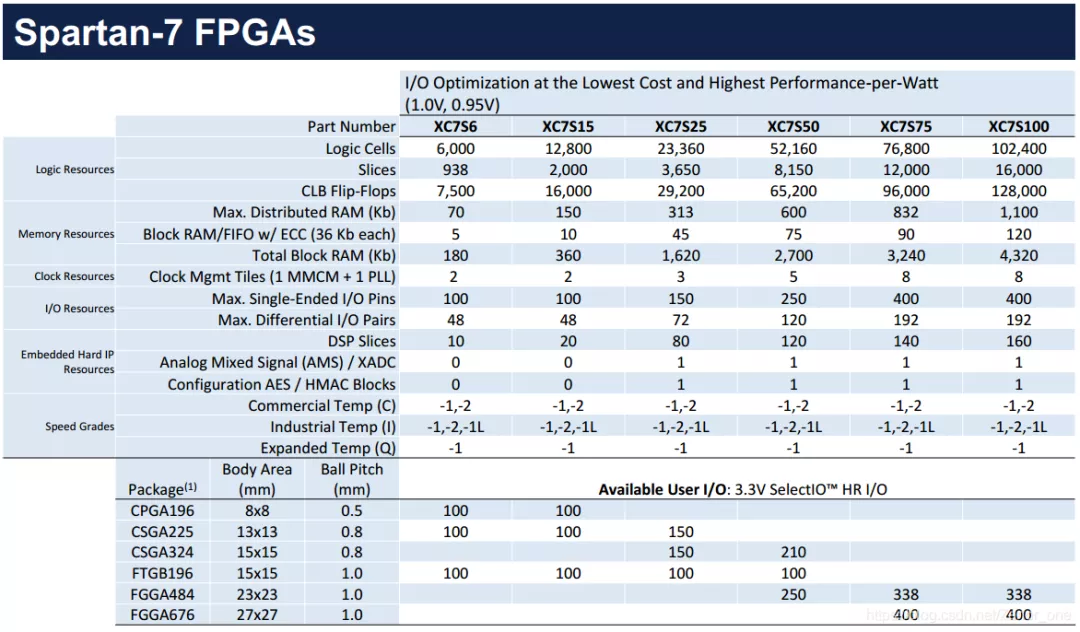

Xilinx 7系列FPGA的时钟结构解析

Xilinx 7系列FPGA管脚是如何定义的?

Xilinx 7系列FPGA芯片管脚定义与封装

实现ARM9与FPGA的并口通信的两种方式

两种JESD204B A/D转换器转FPGA设置与实现技巧

在MATLAB/simulink中建模时的两种不同实现方式

MATLAB/simulink中两种实现建模方式的优势

Xilinx 7系列与Ultrascale系列FPGA的区别

在Xilinx 7系列FPGA上两种实现方式的差别

在Xilinx 7系列FPGA上两种实现方式的差别

评论